Proyecto de Sistemas Informáticos - E

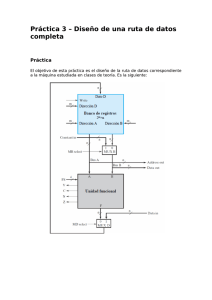

Anuncio