Memòria del projecte en format PDF

Anuncio

Desarrollo de software de control para acceso a discos

duros SATA

TITULACIÓN: Ingeniería Técnica Industrial en Electrónica Industrial

AUTOR: Mohamed Anaimi

DIRECTOR: Esteban del Castillo Pérez

FECHA: Septiembre del 2010

Índice 1 Introducción .................................................................................................5 2 Objetivo.........................................................................................................7 3 Especificaciones previas ..............................................................................8 4 Antecedentes.................................................................................................9 4.1 La evolución de los discos ............................................................................... 9 4.2 Elementos que hacen posible el funcionamiento del disco SATA ............. 13 4.2.1 Ordenador............................................................................................................ 13 4.2.2 Disco SATA: ........................................................................................................ 13 4.2.3 Advanced Host Controller Interface (AHCI) ..................................................... 14 4.3 Interfaz de usuario (parte gráfica)............................................................... 15 4.4 Beneficios del programa de gestión del disco.............................................. 16 5 Análisis previo ............................................................................................17 6 Disco SATA.................................................................................................18 6.1 El Hardware (el nivel físico) ......................................................................... 18 6.1.1

6.1.2

6.1.3

6.1.4

Spread Spectrum Clocking.................................................................................. 18 Cables y Conectores ............................................................................................ 18 Señales OOB (Out Of Band).............................................................................. 20 Secuencia de inicialización del phy ................................................................... 21 6.2 El nivel de Enlace........................................................................................... 21 6.2.1 Codificación 8b10b: Caracteres de datos, caracteres de control y patrón Coma

........................................................................................................................................ 21 6.2.2 Primitivas y Tramas ............................................................................................ 23 6.3 El nivel de Transporte................................................................................... 25 6.3.1 Modos de transferencia ....................................................................................... 25 6.3.1.1 Programmed I/O ............................................................................................ 26 6.3.1.2 DMA .............................................................................................................. 27 6.3.1.3 ULTRA DMA................................................................................................ 30 6.3.2 Los registros Shadow .......................................................................................... 32 6.3.2.1 Registro de comandos .................................................................................... 33 6.3.2.2 Puerto de datos............................................................................................... 34 6.3.2.3 Registro de datos............................................................................................ 35 6.3.2.4 Registro del dispositivo ................................................................................. 36 6.3.2.5 Registro de control del dispositivo ................................................................ 37 6.3.2.6 Registro de errores ......................................................................................... 38 6.3.2.7 Registro de características.............................................................................. 39 6.3.2.8 LBA alto ........................................................................................................ 40 6.3.2.9 LBA bajo........................................................................................................ 41 6.3.2.10 LBA medio .................................................................................................. 42 6.3.2.11 Registro de cuenta de sectores ..................................................................... 43 2

6.3.2.12 Registro de estado ........................................................................................ 44 6.3.2.13 Registro de estado alternativo...................................................................... 45 6.3.3 FIS (Frame Information Structure)................................................................... 46 6.3.4 Nuevo bloque de registros SATA ........................................................................ 47 6.3.5 Direccionamiento 48-bit...................................................................................... 48 6.3.6 Descripción de comandos.................................................................................... 50 6.3.5.1 Read Sectors .................................................................................................. 50 6.3.5.2 Read Sectors EXT.......................................................................................... 53 6.3.5.3 Write Sectors.................................................................................................. 55 6.3.5.4 Write Sectors EXT......................................................................................... 57 6.3.5.5 Read multiple................................................................................................. 59 6.3.5.6 Read multiple EXT ........................................................................................ 61 6.3.5.7 Write multiple ................................................................................................ 62 6.3.5.8 Write multiple EXT ....................................................................................... 65 6.3.5.9 Read DMA..................................................................................................... 66 6.3.5.10 Read DMA EXT .......................................................................................... 68 6.3.5.11 Write DMA .................................................................................................. 69 6.3.5.12 Write DMA EXT ......................................................................................... 71 6.3.5.13 Identify Device ............................................................................................ 72 6.3.5.14 Device reset.................................................................................................. 74 6.4 SATA II .......................................................................................................... 75 6.4.1

6.4.2

6.4.3

6.4.4

Extensiones de SATA .......................................................................................... 75 Multiplicador de Puertos..................................................................................... 75 Selector de Puerto................................................................................................ 76 Cables y Conectores ............................................................................................ 76 7 El lenguaje de programación C ................................................................77 8 Desarrollo del software..............................................................................79 8.1 Parte gráfica: ................................................................................................. 80 8.2 Parte funcional: ............................................................................................. 83 8.3 Pasos para la realización del software ......................................................... 86 9 Resultados finales.......................................................................................88 9.1

9.2

9.3

9.4

9.4

La función Editar .......................................................................................... 88 La opción Copiar ........................................................................................... 89 La opción Comparar ..................................................................................... 90 La opción Buscar ........................................................................................... 91 La opción Configurar.................................................................................... 92 10 Manual de instalación y uso....................................................................93 10.1 Instalación del disco duro SATA................................................................ 93 10.2 Instalación del sistema operativo MS-DOS............................................... 94 11 Presupuesto...............................................................................................96 12 Conclusiones .............................................................................................97 13 Bibliografía y referencias ........................................................................98 13.1 Referencias ................................................................................................... 98 13.2 Bibliografía................................................................................................... 98 3

14 Anexo.........................................................................................................99 14.1 Comandos..................................................................................................... 99 14.2 contenido de la respuesta al comando Identify device ............................ 101 14.3 Diferentes rutinas extraídas del código ................................................... 106 14.3.1

14.3.2

14.3.3

14.3.4

14.3.5

14.3.6

La función Disk_access48( )........................................................................... 106 La función x_disco48( ) .................................................................................. 110 La función main( ) .......................................................................................... 113 La rutina de atención a la interrupción ......................................................... 115 La función SetIdeDriver( ).............................................................................. 120 La función de obtención del valor tecleado.................................................... 122 4

1 Introducción

Mediante la realización de este proyecto se pretende obtener una aplicación que permita

el acceso a discos duros del tipo SATA1. La aplicación nos permitirá realizar

operaciones de búsqueda, copia, comparación y edición sobre cualquier parte de

cualquier disco duro, de este tipo o compatible, accesible en el sistema.

El usuario podrá ver la información del disco en bits i código ASCII2. El acceso será del

más bajo nivel posible, puesto que el consumidor podrá editar cualquier bit de los

sectores del disco. Este software puede ser útil para restablecer información alterada en

el disco duro, de forma que pueda ser reconocido de nuevo por el sistema operativo

quedando accesible su información (recuperación de información), para realizar copias

de seguridad con idéntico contenido (copia imagen), para realizar búsqueda de patrones

(que permita localizar ficheros posiblemente borrados), etc

Actualmente se comercializan muchas aplicaciones para Windows que permiten hacer

esta tarea. El inconveniente de estas es que en caso de fallo del sistema operativo, el

disco duro queda totalmente aislado y por tanto el acceso será imposible. Una ventaja de

este programa es que opera bajo DOS3. Esto permite un rápido acceso a las herramientas

desarrolladas en este proyecto y las hace independientes de cualquier sistema operativo

instalado en el disco dañado. Las funciones principales del programa están explicas en

el apartado Resultados finales.

ATA paralela significa conexión de tecnología avanzada en paralelo, del inglés Parallel

Advanced Technology Attachment (PATA). Ha sido la interfaz de las unidades de disco

duro de los ordenadores de sobremesa durante más de 15 años. ATA paralela se puede

encontrar en ordenadores de sobremesa, portátiles, electrónica de consumo y algunos

servidores actuales. Aún existe gran cantidad de unidades de disco duro PATA en el

mercado. Hasta que se produzca la total transición de paralelo a serie, muchos

ordenadores seguirán utilizando las unidades de disco ATA paralela.

La interfaz ATA serie (SATA) se diseñó para ser la sustituta de la interfaz ATA paralela

en los sistemas de almacenamiento de red, ordenadores de sobremesa, ordenadores

portátil y electrónica de consumo. SATA permite trasladar más datos en menos tiempo,

lo que aumenta el rendimiento y la flexibilidad. La cola de comandos nativa, una de las

características clave de SATA, hace posible ordenar y dar prioridad a varios comandos

al mismo tiempo, y reducir el desgaste mecánico de la unidad. Otras características,

como la conexión en caliente, la aceleración de giro escalonada y la velocidad de

transferencia rápida de 3 Gb/s, hacen de SATA la elección perfecta para servidores,

estaciones de trabajo, ordenadores de sobremesa, dispositivos de electrónica de

consumo y ordenadores portátiles.

1

Véase el apartado 6.0 para ver la definición y las características de los discos SATA.

El código ASCII (acrónimo inglés de American Standard Code for Information Interchange) es un

código de caracteres basado en el alfabeto latino. Fue creado en 1963. el código ASCII utiliza 7 bits para

representar los caracteres.

3 "DOS" es una familia de sistemas operativos para PC.

2

5

Tal y como hemos sido testigos durante estos últimos años, y al mismo ritmo que han

ido creciendo las prestaciones de los discos duros, los canales de comunicación por los

que circula la información entre estos y el resto del sistema ha ido sufriendo una

paulatina y en el mismo tiempo una imprescindible modernización, acorde con el cada

vez mayor caudal de datos en tránsito entre ambos extremos de la comunicación: host y

disco duro.

Esta aplicación ya fue desarrollada, por el profesor Esteban del Castillo, para discos

Parallel ATA de hasta 137 Gigabytes de memoria. Nuestro objetivo será aprovechar la

misma aplicación y mejorarla para acceder a discos Serial ATA con una limitación de

memoria mucho más superior. Para eso se tendrá que adecuar el programa de tal forma

que no se vea afectado por la enorme evolución de la capacidad de los discos duros

permitiendo el correcto funcionamiento del mismo con dispositivos cuyas prestaciones

son mejores que los actuales.

Más adelante se hará una explicación detallada de la arquitectura de los discos SATA

tanto a nivel físico y eléctrico como a nivel lógico. Esto será el punto de partida para

entender las diferencias que hay respecto a los discos PATA.

Es importante destacar que gracias a organismos como ‘Technical Committee T13’ o

bien ‘Serial ATA International Organisation’ se ha hecho posible mantener una cierta

compatibilidad entre los diferentes tipos de discos pese la complejidad de las interfaces.

Quizá el paso más significante es la conservación de elementos, en las especificaciones

del Serial ATA, que permiten el funcionamiento del ATA paralelo.

El controlador SATA por un lado emula el funcionamiento de un interfaz ATA

estándar, lo que permite a los programas BIOS y drivers actuales (denominados

genéricamente software Heredado) acceder a los dispositivos SATA como si se trataran

de dispositivos estándar ATA, y por otro implementa nuevos recursos para permitir que

drivers SATA de nuevo desarrollo (software Nativo) puedan acceder a las nuevas

funcionalidades y posibilidades del interfaz SATA.

Para la realización de este proyecto vamos a tener que programar tanto a alto nivel (C)

como a bajo nivel (ensamblador). Afortunadamente disponemos de una herramienta

sencilla de programación (Borland C) que permite enlazar ficheros de los dos tipos y

generar el ejecutable (.exe) deseado para Disk Operating System.

6

2 Objetivo

El objetivo principal de este proyecto es la realización de una aplicación que permita el

acceso directo del usuario a los discos duros SATA. La aplicación está diseñada tanto

para usuarios con pocos conocimientos de informática como para programadores y

personal de mantenimiento.

Para realizar dicho proyecto se conseguirán otros dos objetivos didácticos: el primero es

el conocimiento de los dispositivos de almacenamiento masivo, para conseguir esta

información se consultarán manuales de fabricantes, documentos de especificaciones y

también estándares publicados.

El otro objetivo tiene que ver con la aplicación de los conocimientos adquiridos con los

estudios de la carrera. Se trata de la profundización en la programación en lenguaje C

sobre plataforma PC. Esto hace de este proyecto un importante complemento de

formación, y posiblemente una continuación de la asignatura INFORMATICA

INDUSTRIAL II.

7

3 Especificaciones previas

Para la realización de este proyecto se marcaran las siguientes especificaciones previas:

• El software debe desarrollarse en lenguaje de programación C.

• Como paso previo, la realización de un código con una interfaz simple de lectura

y escritura en el disco.

• Se tendrá que mantener la compatibilidad con el programa original.

• Se debe utilizar la interfaz facilitada y adecuarla para cantidades superiores de

memoria.

• Las modificaciones hechas en el programa original no deben afectar en ningún

caso las funciones ya implementadas.

El lenguaje de programación para este proyecto será el C, un código de fácil manejo con

gran compatibilidad con muchos PCs. Este código permite programar tanto a alto nivel

como a bajo nivel. Es importante destacar que se incluye en el proyecto un fichero

hecho en lenguaje ensamblador, este último es para el manejo de las interrupciones

donde es imprescindible la reducción de los tiempos de ejecución del código.

El código que se tiene que realizar en la fase previa es totalmente orientativo. Podemos

decir que es una introducción a una aplicación práctica de los conocimientos adquiridos

de los manuales de especificaciones de los discos duros. En este caso no importa la

parte grafica (interfaz de usuario) sino la parte funcional. Conseguir una simple lectura

y escritura de un sector nos abrirá muchas puertas en el entendimiento de los diferentes

métodos de acceso a estas unidades de almacenamiento.

Las especificaciones anteriores se basan en la idea de hacer un programa para gestión de

los diferentes tipos de discos duros que podemos encontrar en el mercado hoy en día.

En el mismo tiempo se hace una prevención de posibles detalles de futuros avances en

los discos duros como ahora el volumen de estos, un ámbito que avanza de forma brutal.

Vista la gran evolución de las capacidades de los discos duros, nos vemos obligados a

modificar la interfaz de usuario para una correcta visualización del número de sectores

del disco y el tamaño de este. El número de sectores a los que se pueden acceder

superará pronto el límite de tamaño de las variables que se pueden definir en C.

8

4 Antecedentes

4.1 La evolución de los discos

En 1957, se introdujo como un componente de IBM RAMAC la primera unidad de

discos duros.

Requirió 50 discos de 24 pulgadas para guardar cinco megabytes (millón bytes, se

abrevió MB) de datos y costó US$35.000 por año o arrendarlo a US$7.000 por

megabyte anual. Fue el primer ordenador comercial que utilizaba disco duro de

cabeza móvil (unidad de disco magnético) como almacenamiento secundario. IBM

lo lanzó el 4 de septiembre de 1956.

RAMAC eran las iniciales en inglés de "Sistema de Contabilidad con Memoria de

Acceso Aleatorio" ("Random Access Memory ACcounting System" . Su diseño

estuvo motivado por la necesidad de sustituir el fichero de tarjetas perforadas

utilizado por la mayoría de las oficinas de la época. El primer RAMAC destinado a

ser usado en la industria del automóvil estadounidense fue instalado en la Chrysler's

MOPAR Division en 1957. Sustituyó a un gigantesco fichero que era parte del

sistema de procesamiento para el control de inventario y pedidos de piezas de

MOPAR. El 305 fue uno de los últimos ordenadores de tubo de vacío construídos

por IBM.

El sistema de disco IBM 350 almacenaba cinco millones de caracteres de siete bits

(aproximadamente 4,2 MiB). Tenía cincuenta discos de veinticuatro pulgadas de

diámetro. Dos brazos independientes se desplazaban verticalmente seleccionar un

disco y horizontalmente para seleccionar una pista de grabación, todo para control

de servomecanismos. El tiempo medio de posicionamiento en un registro era de

seiscientos milisegundos. En la década de 1950 se añadieron varios modelos

mejorados.

El ordenador IBM RAMAC 305 con almacenamiento en disco 350 tenía un coste en

"leasing" de 3.200 dólares mensuales en dólares de 1957, equivalente a un precio de

compra de unos 160.000 dólares. Se construyeron más de 1.000 unidades. La

producción terminó en 1961, el RAMAC pasó a ser obsoleto en 1962 con el

lanzamiento del IBM 1401 y retirado del mercado en 1969.

En el 1962 IBM introdujo un nuevo modelo, el 1301, con una capacidad de 28 MB

y una velocidad de transferencia y una densidad de área 10 veces mayor que el

RAMAC 305. La distancia entre los cabezales y la superficie del disco había

descendido desde 20,32 µm a 6,35 µm.

A partir del año 1962, muchos fabricantes comenzaron a vender discos duros como

el 1301. La Unidad de almacenamiento en disco de IBM, con su mayor capacidad,

flexibilidad y velocidad, se ha ampliado la capacidad operativa de la serie 7000 de

los ordenadores de IBM (7070, 7094, 7080 y 7090).

9

Figura 1. El modelo 1301 con 28MB de memoria

Utilizado en combinación con la serie 7000, el 1301 había muchos de los mismos y las

características físicas generales de funcionamiento como cuando se utiliza con el IBM

1410 Data Processing System. Estas características incluyen: el concepto del cilindro

(verticalmente alineados de lectura / escritura cabezas, una a una superficie del disco,

para proporcionar la lectura y escritura de información en temas relacionados con el

disco correspondiente y para eliminar la necesidad de acceso para el movimiento

vertical); longitud de registro flexibles (diferentes registros de longitud podría ser

almacenados en el archivo, aumentando enormemente la capacidad de almacenamiento

real); y selectiva frente (números de registro fueron asignados por el usuario para una

mayor eficacia en muchos puestos de trabajo, las direcciones no tienen que ser

consecutivos, secuencial o numérico).

El 1301 de los discos giran a 1.800 rpm. El 1301 proporcionó las 50 pistas por pulgada

y grabación de hasta 520 bits por pulgada de pista (gracias a una reducción media en la

cabeza-a-distancia de la superficie de 800 a 250 micropulgadas). Como resultado, la

capacidad de almacenamiento por pulgada cuadrada de la superficie se incrementó 13

veces más de lo que había sido con la tecnología de IBM RAMAC de 1956.

El Modelo 1 de la 1301 había un módulo, el Modelo 2 con dos módulos. Módulo de la

capacidad de la 1301 utilizadas con 7000 equipos de la serie fue de 28 millones de

caracteres, que se utiliza con el equipo del 1410, la capacidad del módulo fue de 25

millones de caracteres. Hasta el 10 módulos (cinco unidades de 1301) podría ser

incorporada - 7631 utilizando el archivo de la unidad de control de IBM, y en algunos

casos, los adaptadores y los canales de datos - a un sistema informático, proporcionando

una capacidad máxima de 280 millones de caracteres de la serie 7000 máquina y 250

millones para el 1410.

10

Fabricado en la planta de IBM en San José, California, los 1301s fueron entregados a

los clientes en el tercer trimestre de 1962. (A pocos días antes del 1301 se anunció

oficialmente en junio de 1961, un modelo de ingeniería del 1301 fue enviado a IBM en

Poughkeepsie, NY, instalaciones para el uso en las pruebas del famoso sistema SABRE

reserva. Más tarde, en pleno funcionamiento, el sistema SABRE adjunta seis tambores

magnéticos de almacenamiento y 16 de IBM 1301s.)

El Modelo 1 con un costo módulo de $ 2.100 por mes para alquilar o podrían ser

comprados por 115.500 dólares. El Modelo 2 con dos módulos de un costo de $ 3.500

por mes para alquilar o 185.500 dólares a la compra.

Figura 2. El modelo 2310

En 1965, IBM lanzó el modelo 2310, cuya notable característica era ser un elemento de

almacenamiento desmontable (el primer disco flexible). En abril de 1967, IBM anunció

una expansión de cuatro modo de sistema de 1130. Nuevas características para el

escritorio de computadora del tamaño de IBM más pequeño a la vez, incluyó la

capacidad de leer la información de cinco discos magnéticos al mismo tiempo.

Anteriormente, sólo un equipo autónomo de disco (primer plano) estaba disponible. Sin

embargo, en 1967, hasta cuatro discos adicionales (a la derecha, parte trasera) se podría

agregar. Cada uno puede almacenar hasta un millón de caracteres de información.

El 2314, lanzado en 1966, tenía cabezales de lectura de ferrita (óxido de hierro).

Anunció un año después de la System/360 en abril de 1965, el IBM 2314 proporcionó

ocho unidades de disco y una de repuesto, junto con una unidad de control en una

misma instalación. Un paquete nuevo disco con 11 discos duplicó el número de

superficies de almacenamiento de más de los disponibles en el paquete de la primera de

11

disco extraíble. La densidad de grabación el incremento de la capacidad de

almacenamiento de 29,2 millones de bytes por paquete o 233 millones de bytes en las

ocho instalaciones de carga.

El tiempo de acceso y la latencia de la 2314 era la misma que la de más edad de IBM

2311, pero el 2314 ofrece el doble de la velocidad de datos de 310.000 bytes por

segundo. El 2314 también fue interesante porque era cuatro veces menor en el precio

por megabyte de almacenamiento.

Ayudado por OS/360 - s el IBM S/360 'del sistema operativo - el 2314 grandes bases de

datos les permite tener acceso, y el sistema pasó de un trabajo a otro de forma

automática siempre y cuando las instrucciones necesarias y los datos fueron en línea.

Algunos observadores han dicho que OS/360 ayudado a hacer del 2314 el producto de

almacenamiento más rentable que el tiempo y que el 2314 ha contribuido al éxito de la

IBM S/360.

En enero de 1969, IBM anunció dos nuevas versiones del 2314 - la A1 1 Modelo y

Modelo 1 A2 - cada uno con un tiempo de acceso un 20 por ciento más rápido que el

disponible anteriormente Modelo 1. Uno de los nuevos modelos de almacenamiento en

disco con cinco unidades de disco independiente, y el otro tenía ocho. La versión de

cinco unidades con una capacidad de almacenamiento de 145,8 millones de bytes; la

más grande tenía una capacidad de 233,4 millones de bytes. El tiempo de acceso

promedio se redujo en 75 a 60 milisegundos. El tiempo de acceso mínimo era de 25

milisegundos.

Las nuevas versiones incluidas sus unidades de control propio y han sido diseñados para

su uso con S/360 Modelos 30, 40, 50, 65, 67, 75 y 85. El más pequeño de 2314 alquiló

3.875 dólares al mes y se vendió por $ 175.075. La versión más grande de alquiler de

5.675 dólares al mes, con un precio de compra de 256.400 dólares. Primer cliente de los

envíos se habían programado para el tercer trimestre de 1969.

Más tarde, en 1969, una caja con dos unidades que se ofrecía. En 1970, la unidad de

almacenamiento de 2319 se ha configurado con tres unidades de 2314, más la

electrónica de control para la adhesión a los más pequeños de la recién anunciada

System/370 transformadores.

En el 1980 se hizo el primer disco duro de 5,25" (cinco-coma-veinticinco pulgadas),

desarrollado por la compañía Seagate. La revolución de la computadora personal a

comienzos de 1980 cambió todo, es la introducción de los primeros discos duros

pequeños. Eran discos de 5.25 pulgadas los que manejaban de 5 a 10 MB de

almacenamiento- el equivalente de 2.500 a 5.000 páginas de tecleo de información- en

un aparato del tamaño de la caja de un zapato pequeño. Al tiempo se consideró que una

capacidad de almacenamiento de 10 MB era demasiado grande para una llamada

computadora "personal". Los primeros PCS usaron discos flexibles trasladables como

aparatos de almacenamiento casi exclusivamente. El término "disco blando" con

precisión se refiere a los primeros discos para PC de 8 y 5.25 pulgadas que tuvieron

éxito. Los discos internos de hoy, más pequeños, se construyen 3.5 pulgadas de forma

similar a los anteriores, pero se albergan en un casco de plástico rígido, que es más

durable que el techado flexible de los discos más grandes.

12

Alrededor de 1992 varios modelos 1.8 pulgadas aparecieron, peso sólo unas onzas y

entrega capacidades de hasta 40 MB. Igualmente aparecieron con formato de 1.3

pulgadas, del tamaño de una fosforera. Factores de forma más pequeños por supuesto,

no eran necesariamente mejor que los más grandes.

En el periodo entre 1995 y 1999 el disco duro más pequeño que puede encontrarse en

ésta época es el de 4 GB, mientras que el más grande es de 15 GB. Podría decirse que

los discos duros de cualquier tamaño, permiten instalar Windows, Office y un programa

de contabilidad, y aún sobrará capacidad para, digamos, unas 50.000 cartas y varios

millones de apuntes bancarios.

En la actualidad, ya contamos en el uso cotidiano con discos duros de más de un

terabyte (TB) o 1.048.576 megabytes.

4.2 Elementos que hacen posible el funcionamiento del disco SATA

4.2.1 Ordenador

Este puede ser portátil o de sobremesa. Contiene todos los dispositivos que nos

permiten, entre otras cosas, el acceso al disco. Podemos incluir también todos los

periféricos como ahora el teclado, el ratón y la pantalla. La placa base tiene que ser

compatible con los discos SATA de grandes capacidades.

4.2.2 Disco SATA:

Figura 3. Disco Serial ATA

13

Se trata de un disco duro con una interfaz serie de transferencia de datos con la placa

base. Un hecho ya conocido es que con estos discos se alcanzan velocidades de

transferencia muy superiores a los discos que usan la conexión paralela.

La primera generación especifica en velocidades de 1.5 Gbit por segundo, también

conocida por SATA 1.5 Gb/s o Serial ATA-150. Actualmente se comercializan

dispositivos SATA II, a 3 Gb/s, también conocida como Serial ATA-300 y los SATA

III, a 6 Gb/s, que incluyen una velocidad de 6.0 Gb/s estándar. Los discos que soportan

la velocidad de 3Gb/s son compatibles con un bus de 1,5 Gb/s.

4.2.3 Advanced Host Controller Interface (AHCI)

Este dispositivo se encarga de emular el funcionamiento de un interfaz ATA estándar. La

emulación puede consistir en presentar los dispositivos como si fueran Maestros de

distintos puertos ATA, o presentarlos por parejas como si fueran Maestro y Esclavo de

un puerto ATA. La emulación es completa, tanto a nivel del comportamiento del

controlador como de los dispositivos, incluyendo el comportamiento de los bloques de

registros de Comando y de Control, las transferencias en modo PIO, DMA y UDMA,

las interrupciones y los distintos procesos de inicialización.

En el interfaz paralelo, toda la comunicación a nivel de comandos, datos y estado entre

un dispositivo y el driver se hace mediante los registros de Comando y de Control

situados en el propio dispositivo. Cada dispositivo dispone de su propio bloque de

registros y el driver lee y escribe directamente en ellos. Las direcciones de los registros

son distintas para cada puerto ATA, pero son las mismas tanto para el Maestro como

para el Esclavo de cada puerto, debiendo el driver seleccionar previamente a uno de

ellos mediante la escritura de un bit de selección de dispositivo en uno de los registros.

El dispositivo que no está seleccionado simplemente no hace caso a ninguna lectura o

escritura en el bloque de registros, salvo las escrituras de dicho bit para detectar cuándo

el driver lo selecciona para comunicarse con él.

En el caso del interfaz SATA, el driver no puede evidentemente leer y escribir

directamente en los registros de los dispositivos, por lo que el controlador SATA

implementa un bloque de registros por cada dispositivo (denominado Bloque de

Registros Shadow) que refleja el contenido y el comportamiento de los registros de los

dispositivos. El driver entonces lee y escribe realmente en el bloque de registros shadow

del controlador SATA, mientras que por el otro lado el controlador y los dispositivos

SATA se intercambian la información a través de la línea serie para sincronizar los

contenidos de los registros. En el caso de una emulación Maestro/Esclavo, es

responsabilidad del controlador SATA enviar la información al dispositivo adecuado, en

función del bit de selección de dispositivo escrito previamente por el driver en el

registro shadow correspondiente.

14

4.3 Interfaz de usuario (parte gráfica)

Como ya se ha comentado anteriormente, en este proyecto no se tendrá que hacer una

interfaz de usuario puesto que ya disponemos de una diseñada para un programa de

acceso a discos PATA.

Disponemos de una interfaz muy completa que incluye prácticamente todas las opciones

necesarias para la gestión de los discos duros. Esta interfaz permite elegir, en caso de

varios discos, el dispositivo que se desea visualizar, editar, copiar, etc. La lista de los

dispositivos disponibles y su información correspondiente se visualiza nada más al

iniciar el programa.

La interfaz está diseñada para acoplar trozos de código en forma de ficheros de un único

proyecto donde se hará la comparación de discos, copia de una unidad a otra, búsqueda

de información en modo binario o ASCII y por supuesto la edición manual de los

sectores de los discos.

Figura 4. Portada de la interfaz ejecutada en Windows (no permite ver discos)

La capacidad de almacenamiento de los discos SATA, en la mayoría de los casos, es

muy superior a los dispositivos con conexión paralela. Por esta razón, la interfaz

necesita unas actualizaciones, sobre todo cuando se imprime por pantalla el tamaño del

disco en Megabytes.

La interfaz permite la posibilidad de acceso a cualquier sector del disco. Para ello el

usuario podrá ir avanzando los sectores de uno en uno o bien introducir de forma

numérica el orden del sector que quiere visualizar o editar. Las variables que contienen

estos datos próximamente no podrán contener todo el valor. Quizá este sea uno de los

detalles más importantes que se tendrán en cuenta como previsión de la evolución de las

capacidades de almacenamiento de los discos duros.

15

4.4 Beneficios del programa de gestión del disco

• Es un recurso flexible y adaptable a diferentes tipos de usos. El programa puede

ser usado por programadores para corrección de sectores dañados, eliminación

de datos y ficheros que afectan el correcto funcionamiento del sistema…también

la aplicación puede servir como simple herramienta para hacer copias de

seguridad o bien copia de datos de unos discos a otros.

• Con este programa se consigue reducir de forma significativa el tiempo que dura

una transferencia de datos de un disco duro: un ejemplo comprobado es el hecho

de copiar 122 GB de memoria de un disco a otro en una hora y media. Mover

esta cantidad de datos en Windows de un disco a otro puede tardar diez veces

más.

• El usuario se enfrenta a una tecnología sencilla, especialmente si se compara con

otras herramientas para este fin.

• El programa no necesita ningún tipo de instalación. Solo se tendrá que acceder a

MS-DOS ubicado en un dispositivo de almacenamiento USB y ejecutar la

aplicación. La ventaja de esto es que el acceso al disco es independiente de la

información que tiene el mismo. En Windows, el sistema operativo se ubica en

la memoria del disco duro. Si el disco está dañado no se podrá arrancar salvo

que se use otro dispositivo compatible.

• Para la mayoría de casos el uso de esta aplicación no requiere muchos

conocimientos previos. Es una aplicación intuitiva.

• El programa se podrá utilizar para la gestión de prácticamente todos los tipos de

discos duros que se pueden encontrar en el mercado. Independientemente de la

tecnología empleada y los protocolos de transferencia de datos (hay pocas

limitaciones). Se podrá acceder a discos duros de los diferentes fabricantes.

• El programa estará diseñado para gestionar discos duros con una capacidad de

almacenamiento de datos mucho más superior a la actual. Se prevé un futuro uso

de esta aplicación pese el progreso continuo en este ámbito.

16

5 Análisis previo

Antes de empezar a realizar el programa de gestión de los discos duros deben fijarnos

en las características principales que debe tener.

Disponemos de una interfaz que se tiene que acoplar al proyecto y también de un

programa ya hecho para gestión de discos duros IDE. Nuestro objetivo será hacer una

parte que trabaje en paralelo con la existente sin influir en el correcto funcionamiento de

esta.

Entonces nos encontramos con dos opciones. La primera consiste en modificar todas las

funciones del programa origen e introducir el código para el correcto funcionamiento en

los discos SATA. En este caso se emplearán condicionales en casi todas las líneas de

código en las que hay diferencia de funcionamiento.

La segunda opción es la redacción de funciones totalmente independientes para el

acceso a los disco serie y la conservación de las anteriores. En este caso, el flujo del

programa dependerá del tipo del disco (véase el apartado 8.2).

Está claro que la solución óptima es la segunda porque con esta evitaríamos tocar el

código original y nos ahorraríamos posibles errores en el funcionamiento habitual del

programa proporcionado. Aparte de eso, el código que regula las condiciones será

mínimo (solo al ejecutar una función u otra).

El inconveniente de esta solución es la extensión del código. Se puede llegar a duplicar

las líneas de código del programa y por lo tanto un aumento del tamaño del programa.

El tiempo de ejecución no se verá afectado porque, dependiendo del disco al que se

acceda, se usarán unas funciones u otras.

Un detalle muy importante que hay que tener en cuenta es la diferencia en los comandos

que se envían al disco. Hablamos de comandos para discos que implementan 28 bits

para el Direccionamiento de bloque lógico (LBA) con un máximo de 137.4 GB y otros

comandos diferentes para los dispositivos de 48 bits de direccionamiento para

capacidades muy grandes (144 Petabytes).

Por cuestiones de compatibilidad, los comandos de los discos de 28 bits suelen ser

válidos para los discos de direccionamiento superior (48 bits). Como diseño previo del

proyecto hemos decidido acceder a cada disco con los comandos propios

implementados especialmente para este, pese la existencia de la posibilidad de utilizar

los otros comandos con ciertas limitaciones. Un ejemplo de estos casos es el comando:

READ SECTOR, este comando es para discos que implementan un direccionamiento de

28 bits. Se podrá acceder a un disco de una capacidad superior a 137 GB siempre y

cuando se lea un sector con orden inferior a esta cantidad de memoria. Si pretendemos

leer un sector que se encuentra en una posición superior la lectura será errónea.

17

6 Disco SATA

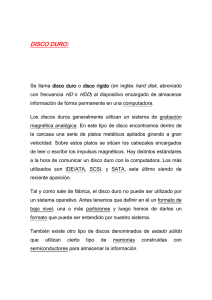

El disco duro es un dispositivo de almacenamiento de datos no volátil, que conserva la

información aun con la pérdida de energía y que emplea un sistema de grabación

magnética digital. Dentro de la carcasa hay una serie de platos metálicos apilados

girando a gran velocidad. Sobre los platos se sitúan los cabezales encargados de leer o

escribir los impulsos magnéticos.

6.1 El Hardware (el nivel físico)

La interfaz SATA se compone de dos pares de señales diferenciales, una para transmitir

en un sentido y otra para transmitir en el sentido opuesto. La información se transmite

en código NRZ a una tensión nominal de +/- 250 mV. El interfaz eléctrico al cable se

realiza por medio de un transceptor denominado Phy.

Las velocidades de transmisión normalizadas por el momento son de 1,5 Gbps y 3 Gbps

(1.500 y 3.000 Mbaudios respectivamente), equivalentes a una velocidad en el enlace

físico de 150 y 300 MB/s respectivamente (ya que cada carácter se compone de 10 bits,

debido a la codificación empleada 8b10b).

6.1.1 Spread Spectrum Clocking

SATA utiliza una técnica denominada Spread Spectrum Clocking para rebajar el nivel

de emisión electromagnética, distribuyéndola en un rango de frecuencias en vez de estar

toda concentrada en una frecuencia fija. La técnica consiste en modular la frecuencia del

reloj de transmisión, de manera que la frecuencia se hace variar lentamente siguiendo

una forma triangular (decrece linealmente con el tiempo desde la frecuencia máxima

hasta una determinada frecuencia mínima, y desde ahí crece de nuevo linealmente con

el tiempo hasta la frecuencia máxima). En SATA la frecuencia máxima es igual a la

frecuencia nominal, la frecuencia mínima es el 99,5% de la frecuencia nominal, y el

periodo de la modulación triangular es de 33,33 us. Como la frecuencia se modula

desde la frecuencia nominal hacia abajo, la técnica se denomina down-spreading.

El receptor recibe los bits en código NRZ a la velocidad nominal de 1,5 ó 3 Gbps,

teniendo en cuenta las variaciones en la frecuencia de recepción debidas a la técnica de

down-spreading. A partir de la secuencia de bits el receptor recupera y deserializa los

datos (convierte la secuencia serie en paralelo), y detecta una secuencia especial de bits

denominada patrón Coma que le permite alinear los caracteres de entrada (es decir, le

permite saber qué bit es el primero de cada carácter).

6.1.2 Cables y Conectores

Los dispositivos SATA, tanto de 3,5” como de 2,5”, disponen de un conector macho

con dos segmentos, uno de señal y otro de alimentación, mientras que los controladores

pueden disponer de un conector hembra con los dos segmentos o de un conector macho

con sólo el segmento de señal.

El segmento de señal dispone de 7 contactos, 4 para los dos pares de señal y 3 para

masa. El segmento de alimentación dispone de 15 contactos, 3 para cada alimentación

18

(5V, 12V y 3,3V), uno reservado y el resto para masas. Para permitir la conexión en

caliente, los contactos tienen distintas longitudes para secuenciar la conexión.

Figura 5. Conectores serie

En el caso de conexión directa, el conector del dispositivo se inserta directamente en el

conector hembra de dos segmentos del controlador, lo que proporciona al dispositivo

todos los contactos tanto de señal como de alimentación. Para hacer posible este tipo de

conexión, las posiciones de las señales de transmisión y recepción en el segmento de

señal del controlador están invertidas respecto a las del dispositivo.

En el caso de conexión por cable, el segmento de señal del dispositivo se conecta al

conector macho de señal del controlador mediante un cable de señal SATA, el cual está

formado por dos secciones de cable twinaxial, una para cada par de señal diferencial. La

longitud del cable puede ser de hasta 1 metro y sus dos extremos son simétricos, por lo

que cualquiera de los extremos se puede conectar tanto en el controlador como en el

dispositivo. El conector macho de señal del controlador también tiene invertidas las

19

posiciones de las señales de transmisión y recepción, por lo que el cable de señal no

intercambia las posiciones de los pares. Por otro lado, el segmento de alimentación del

dispositivo se conecta a un cable de alimentación SATA que puede venir directamente

de la fuente de alimentación del equipo o puede terminar en un conector para su

conexión en algún lugar del equipo.

Para facilitar la transición de ATA a SATA, en los dispositivos de 3,5” se permiten

varias configuraciones mixtas de conectores SATA y ATA (denominados conectores

heredados):

• Configuración 35A1: Conector de dos segmentos SATA y ningún conector

heredado

• Configuración 35B1: Conector de dos segmentos SATA y conector heredado de

alimentación y puentes de configuración.

• Configuración 35B2: Conector de señal SATA y conector heredado de

alimentación y puentes de configuración.

• Configuración 35B3: Conector de señal SATA y conector heredado de

alimentación.

• Configuración 35B4: Conector de dos segmentos SATA y conector heredado de

puentes de configuración.

• Configuración 35B5: Conector de dos segmentos SATA y conector heredado de

alimentación.

• Configuración 35C1: Conector de señal SATA, conector heredado de señal ATA

y conector heredado de alimentación

Los dispositivos de 2,5” sólo disponen del conector de dos segmentos SATA:

6.1.3 Señales OOB (Out Of Band)

Las señales OOB (Out of Band) son unos patrones de señales de baja velocidad que no

aparecen durante las transmisiones, y que sólo se utilizan durante la inicialización del

enlace. Consisten en ciclos de duraciones predefinidas de reposo y de transmisión de

unas determinadas secuencias de señal (primitivas ALIGN, que se describen más

adelante). La transmisión de las primitivas ALIGN se usa sólo para producir una

envolvente, de forma de el receptor distingue las distintas señales OOB por la duración

del intervalo de reposo que hay entre las consecutivas secuencias de señal (la duración

de las secuencias de señal no se utiliza para distinguir las distintas señales OOB).

SATA define dos señales OOB:

• COMRESET / COMINIT

El controlador la envía para transmitir la señal COMRESET, que origina una

inicialización hardware en el dispositivo. El dispositivo la envía para transmitir la señal

COMINIT, para solicitar al controlador la inicialización del enlace (negociación de la

velocidad y comienzo de la comunicación).

20

•

COMWAKE

Esta señal la puede enviar tanto el controlador como el dispositivo, y se utiliza para

despertar al otro Phy desde un estado de ahorro de energía, y también durante el proceso

de inicialización del enlace.

6.1.4 Secuencia de inicialización del phy

La secuencia de inicialización del phy consiste en una secuencia de señales OOB

seguida de una secuencia de negociación de velocidad.

La secuencia OOB puede comenzarla el controlador con la transmisión de

COMRESET, o puede comenzarla el dispositivo con la transmisión de COMINIT. La

secuencia también incluye un intercambio de señales COMWAKE y una fase de

calibración de la impedancia de salida del transmisor del controlador (y opcionalmente

también del dispositivo) para adaptarse a la impedancia de la interconexión (ya que

puede ser directa o por cable).

La fase de negociación de velocidad comienza entonces con la transmisión por parte del

dispositivo de primitivas ALIGN a la velocidad más alta que soporte (las primitivas se

describen más adelante), mientras que el controlador transmite un determinado dato a la

velocidad más baja que soporte. Si el controlador soporta la velocidad a la que el

dispositivo está transmitiendo las primitivas ALIGN, entonces pasa a transmitir también

primitivas ALIGN a dicha velocidad, lo que el dispositivo interpreta como que la

velocidad de enlace es correcta.

Si el dispositivo no recibe primitivas ALIGN a esa velocidad en un intervalo de tiempo,

entiende que el controlador no soporta esa velocidad de enlace y comienza un nuevo

proceso a la velocidad inmediatamente más baja que soporte.

6.2 El nivel de Enlace

El nivel de enlace define el uso de la codificación 8b/10b, el uso de las distintas

Primitivas y algunos otros detalles como los relativos al código de detección de errores

(CRC) y a la aleatorización de datos (scrambling), para distribuir la emisión de energía

electromagnética cuando se transmiten secuencias repetitivas de caracteres.

6.2.1 Codificación 8b10b: Caracteres de datos, caracteres de control y patrón Coma

La codificación 8b10b es muy utilizada actualmente en transmisión serie a velocidades

cercanas y superiores al Gbps. Es la codificación utilizada por Fibre Channel (1 y 2

Gbps), posteriormente adoptada por Gigabit Ethernet (1 Gbps), y actualmente en uso

por SAS y SATA (1,5 y 3 Gbps), FireWire 800 (800 Mbps), así como por InfiniBand

(2,5 Gbps).

21

La codificación tiene las siguientes funciones:

• Asegurar suficientes transiciones en la línea como para que el receptor pueda

recuperar el reloj y así pueda recibir adecuadamente la secuencia de bits,

• Incrementar en gran medida las posibilidades de detección de errores simples y

múltiples que puedan ocurrir durante la transmisión, y

• Permitir la transmisión de caracteres especiales que contienen un patrón

fácilmente reconocible por el receptor (denominado patrón Coma), que le

permite alinear palabras en la secuencia de bits que recibe (es decir, le permite

conocer qué bit es el primero de una palabra).

La codificación 8b10b consiste en sustituir cada octeto (8 bits) por un código de 10 bits

antes de su transmisión. De todos los posibles códigos de 10 bits (en total 2^10 = 1024)

sólo se utilizan 512 para codificar todos los posibles caracteres de datos (que en total

pueden ser 2^8 = 256), y unos pocos códigos más para codificar una serie de caracteres

de control (el motivo de utilizar el doble de códigos que de caracteres a codificar se

explica más adelante).

Todos los caracteres que se transmiten en SATA se agrupan en una secuencia de 4

octetos denominada dword. El primer carácter de una dword puede ser un carácter de

dato, en cuyo caso la dword está formada por 4 caracteres de dato (y la información que

transporta es por lo tanto un dato de 32 bits), o puede ser un carácter de control, en cuyo

caso la dword está formada por el carácter de control y 3 caracteres de datos (la dword

en este caso se denomina Primitiva, y transporta información de control).

La codificación 8b10b utiliza un formato particular para expresar los caracteres de 8

bits:

• Zxx.y

Por un lado la letra Z identifica si el carácter es un dato (en cuyo caso Z = D), o si es un

carácter de control (en cuyo caso Z = K). Por otro lado, xx es el valor decimal de los

bits 4:0 mientras que y es el valor decimal de los bits 7:5 del carácter. Entonces Dxx.y

expresa cualquiera de los 256 posibles caracteres de datos, mientras que Kxx.y expresa

cualquiera de los caracteres de control válidos (la codificación 8b10b sólo permite 12

códigos de control válidos).

El codificador 8b10b convierte cada carácter Dxx.y y Kxx.y a su correspondiente

código de 10 bits, teniendo en cuenta que cada carácter puede codificarse mediante dos

códigos distintos, dependiendo del valor de un parámetro que se denomina disparidad

(por eso se necesitan el doble de códigos que de caracteres a codificar).

El concepto de disparidad es el siguiente: de todos los posibles códigos de 10 bits, el

sistema 8b10b sólo utiliza aquellos que tienen:

• 5 unos y 5 ceros. En este caso se dice que el código tiene disparidad neutra,

• 6 unos y 4 ceros. En este caso el código tiene disparidad positiva, y

• 4 unos y 6 ceros. En este caso el código tiene disparidad negativa.

22

La idea es que cada código que se transmita cancele la disparidad producida por el

código anterior, de forma que el nivel de continua de la señal eléctrica es nulo

permanentemente.

De los 12 posibles caracteres de control permitidos por el sistema 8b10b, SATA utiliza

dos: el K28.3 y el K28.5.

De los 12 posibles caracteres de control permitidos por el sistema 8b10b, hay 3 cuyos

códigos de 10 bits contienen en sus 7 primeros bits un patrón especial que se denomina

Coma, que consiste en 2 bits a un valor seguidos por 5 bits al valor contrario. Los phys

utilizan este patrón especial para conseguir la sincronización (alineación) a nivel de

dword, es decir, para conocer qué bit es el primero de una dword (una vez conseguida la

alineación, el phy sabe que cada 40 bits comienza una nueva dword). De los dos

caracteres utilizados por SATA, sólo el K28.5 contiene el patrón Coma, por lo que este

carácter sólo se utiliza en la primitiva ALIGN, mientras que el carácter K28.3 se utiliza

en todas las demás primitivas. De esta manera los Phys alinean los caracteres sólo

cuando reciben la primitiva ALIGN.

6.2.2 Primitivas y Tramas

Las primitivas y las tramas son las dos estructuras utilizadas para intercambiar

información entre el controlador y el dispositivo.

Las primitivas constan de una sola dword que comienza por un carácter de control, y es

la forma más simple de intercambio de información. Las primitivas proporcionan

información de control de bajo nivel.

Las tramas son secuencias de dwords que transportan información. Las tramas siempre

comienzan con la primitiva SOF (Start of Frame) y terminan con la primitiva EOF (End

of Frame). La última dword (que no sea una primitiva) anterior a la primitiva EOF es el

CRC de la trama, mientras que el resto de la trama (es decir, las dwords entre el SOF y

el CRC) es la información propiamente dicha transportada en la trama y se denomina

FIS (Frame Information Structure). Es posible la transmisión de ciertas primitivas de

control de flujo en el interior de la trama (HOLD, HOLDA y CONT).

Las primitivas definidas en SATA son:

•

ALIGN

Se envía para que el nivel físico del receptor reajuste sus operaciones internas (entre

otras, alinear la secuencia de bits de entrada en dwords de la manera correcta, a partir

del patrón Coma).

•

CONT

Se utiliza para eliminar secuencias repetitivas de la misma primitiva, con el objetivo de

reducir el nivel de emisión electromagnética. Cuando hay que enviar repetidamente la

misma primitiva, lo que se hace es enviar la primitiva seguida de la primitiva CONT y

seguida de dwords aleatorias. El receptor interpreta como si estuviera recibiendo

23

repetidamente la primitiva recibida anteriormente a la primitiva CONT, en tanto no

reciba una nueva primitiva.

•

DMAT

La envía el receptor de una trama para solicitar al transmisor que aborte una

transferencia de datos por DMA.

•

EOF

Se usa para indicar el final de una trama.

•

HOLD

El transmisor la envía dentro de una trama en puesto de una dword de dato cuando no

tiene una dword de dato preparada para su transmisión (underrun), y el receptor la envía

para indicar que no puede recibir todavía una nueva dword de dato (overrun).

•

HOLDA

Se envía en respuesta a una primitiva HOLD, y se transmite siempre que se esté

recibiendo

HOLD.

•

PMACK

Se envía en respuesta a una primitiva PMREQ_S o PMREQ_P, y se transmite cuando el

receptor está preparado para entrar en el modo de ahorro de energía solicitado.

•

PMNAK

Se envía en respuesta a una primitiva PMREQ_S o PMREQ_P, y se transmite cuando el

receptor no está preparado para entrar en el modo de ahorro de energía solicitado o no lo

soporta.

•

PMREQ_P

Se envía para solicitar la entrada en el modo de ahorro de energía parcial.

•

PMREQ_S

Se envía para solicitar la entrada en el modo de ahorro de energía total (denominado

Slumber).

•

R_ERR

La envía el receptor de una trama en respuesta a la primitiva WTRM para indicar que se

ha detectado un error en la trama recibida.

•

R_IP

La envía el receptor de una trama en respuesta a la recepción de cada dword de dato.

•

R_OK

24

La envía el receptor de una trama en respuesta a la primitiva WTRM para indicar que no

se ha detectado ningún error en la trama recibida.

•

R_RDY

Se envía en respuesta a una primitiva X_RDY para indicar que se está preparado para

recibir una trama.

•

SOF

Se usa para indicar el principio de una trama.

•

SYNC

Se usa cuando no hay tramas ni primitivas que enviar (el enlace está desocupado).

•

WTRM

La envía el transmisor de una trama tras el EOF mientras espera que el receptor de la

trama envíe el estado de la recepción (R_ERR o R_OK).

•

X_RDY

Se envía para indicar que hay una trama preparada para su transmisión. La trama no se

envía hasta que no se reciba la primitiva R_RDY.

6.3 El nivel de Transporte

6.3.1 Modos de transferencia

Los dispositivos SATA pueden transferir información principalmente empleando dos

métodos: PIO y DMA.

El modo PIO (Programmed I/O) depende del procesador para efectuar el trasiego de

datos. A nivel de rendimiento no hay mayor problema, ya que los micros actuales tienen

la suficiente capacidad para gestionar estas operaciones y alternarlas con otras, por

supuesto.

El otro método es el DMA, así la CPU se desentiende de la transferencia, teniendo ésta

lugar por mediación de un chip DMA dedicado. La variante de la transferencia DMA

usada actualmente en los discos duros es la BusMaster DMA. Esta modalidad

aprovecha las ventajas de los chipsets de las placas base, cada vez más optimizados para

estas labores (de acceso directo a memoria). Además de liberar al procesador, puede

obtener por parte de éste un control casi total, de forma que la información sea

transferida con la máxima prioridad.

25

6.3.1.1 Programmed I/O

El método más antiguo de transferir datos en la interfaz IDE/ATA es el empleo del

modo PIO (Programmed I/O). Esta técnica se basa en que la CPU del sistema y el

hardware de apoyo controlen directamente la transferencia de datos entre el sistema y el

disco duro. Existen varias velocidades de transferencia utilizando este método, estas

variaciones se llaman modos de entrada - salida programados, o más comúnmente,

modos de PIO.

Durante mediados de los años 90, la entrada - salida programada era el único camino

que la mayor parte de sistemas utilizaban para el acceso a discos duros IDE/ATA. Tres

modos de velocidad fueron definidos en las normas ATA aparte de otros dos que fueron

añadidos más tarde. A continuación la tabla nos muestra los cinco diferentes modos de

PIO, con el tiempo de ciclo para cada transferencia y el rendimiento correspondiente del

modo:

Figura 6. Diferentes modos PIO

Algunas cosas sobre esta tabla deben ser mencionadas. Ante todo, los modos PIO son

definidos en función de su tiempo de ciclo, representando cuantos nanosegundos que

este necesita para efectuar una transferencia. El índice de transferencia máxima es el

recíproco del tiempo de ciclo, es el doble porque la interfaz es dos octetos (16 bits).

También, es necesario destacar la ausencia en la tabla del supuesto " modo 5 de PIO ",

Este no existe y nunca fue puesto en práctica en ningún disco duro. Al parecer, una vez

alguna discusión ocurrió sobre la creación de un modo PIO más rápido, que

provisionalmente llamaron " el modo 5 de PIO". Este modo debía soportar una

velocidad de transferencia de 22.2 MB/S, pero nunca fue puesto en práctica

(probablemente porque el modo mucho más rápido Ultra DMA de 33 MB/S 2 lo

superaba mucho). Algunos fabricantes de placa madre se encargaron de dar apoyo a este

modo propuesto para sus programas de BIOS pero al final no tuvieron éxito.

Obviamente, los modos más rápidos son mejores, porque proporcionan una velocidad

de transferencia de la interfaz teóricamente más alta. Esta representa la velocidad de

transferencia de datos alrededor del dispositivo. Hay que recordar que es la velocidad de

la interfaz y no necesariamente la velocidad de transferencia soportada por el disco, que

es casi siempre más lento (y debería ser). Desde luego hoy todos los nuevos discos

soportan velocidades de transferencia superiores a la máxima velocidad que el mejor

modo PIO puede alcanzar, una de la razones porque PIO ha perdido importancia.

26

Como ya se ha mencionado, la I/O programadas se realiza por la CPU, el procesador del

sistema es el responsable de ejecutar las instrucciones que transfieren los datos al disco

y desde él, usando posiciones de entrada - salida especiales. Estos trabajos técnicos son

ideales para dispositivos lentos como teclados y módems, pero para dispositivos de

funcionamiento similar a los discos duros causa problemas de funcionamiento. PIO no

es lo único que implica una atención elevada, la CPU está "distraída" con su trabajo

ordinario hasta que un disco duro necesita ser leído o escrito. Esto quiere decir que la

utilización de PIO es inmejorable para funcionamientos ligeros y tascas simples. Pero

en el mismo tiempo quiere decir que con más transferencias de datos, más atascada está

la CPU. Como las tasas de transferencia de los discos duros siguen aumentando, la

carga sobre la CPU se hace cada vez mayor. Esta es otra razón clave por la cual los

modos PIO son menos usados en nuevos sistemas, estos modos han sido substituidos

por modos DMA, y más tarde por Ultra DMA.

Existen dos canales IDE, cada canal admite el empleo de dos dispositivos, designados

como el máster y el esclavo. Los sistemas modernos permiten que el dispositivo máster

y el esclavo corran en modos PIO diferentes sobre el mismo canal, esto se llama

independent device timing y es una función del chipset y la BIOS. Si no se suporta esta

característica, ambos dispositivos pueden ser limitados al modo PIO más rápido del

dispositivo más lento de los dos, pero esto no es un gran problema desde la segunda

mitad de los años 90.

Los modos PIO no requieren ningún driver especial en circunstancias normales, la

BIOS del sistema contiene toda la información necesaria para un correcto

funcionamiento de estos modos. Esta compatibilidad universal, pese su simplicidad

conceptual, es la manera tradicional usada por defecto en la mayoría de discos. Hoy en

día, sin embargo, PIO se sigue usando para discos modernos, que usan Ultra DMA para

disminuir la carga sobre la CPU y permitir disfrutar de un rendimiento más alto. La

compatibilidad de los modos PIO es todavía universal en casi todos los sistemas y

discos actuales. Se usa, por ejemplo, como último recurso cuando el driver o el software

presentan problemas con el acceso vía Ultra DMA.

6.3.1.2 DMA

Como ya se ha descrito en el apartado anterior (programmed I/O). Aquel método de

transferencia de datos entre el disco duro y el sistema tiene defectos muy serios puesto

que requiere el cuidado y la atención de la CPU del sistema. Claramente, una mejor

solución es dejar la CPU fuera del escenario completamente, y hacer que el disco duro y

la memoria del sistema se comuniquen directamente. El acceso directo a memoria o

DMA es el término genérico que se refiere a un protocolo de transferencia donde un

dispositivo periférico transfiere información directamente a memoria o desde la misma,

sin que se necesite una intervención del procesador de sistema para realizar la

transacción. DMA ha sido usado en el PC durante años con el bús ISA, para

dispositivos como las tarjetas de sonido y la interfaz del disquete. El DMA

convencional usa los canales de DMA regulares que son un recurso del sistema

estándar.

27

Varios modos DMA diferentes han sido definidos para la interfaz IDE/ATA, están

agrupados en dos categorías. El primer juego de modos incluye modos DMA de un solo

Word. Cuando se usan estos modos, cada transferencia es de un solo Word de datos (un

Word es el término técnico de dos Bytes, o bien 16 bits de memoria). Hay tres modos

DMA de un solo Word.

Figura 7. Diferentes modos DMA Single Word

Como hablé en el apartado de PIO, la tasa de transferencia máxima es doble del tiempo

de ciclo específico para cada modo. Obviamente, estas velocidades de transferencia no

son impresionantes para las especificaciones de hoy en día. Lo que es realmente claro es

que realizar transferencias de una sola palabra cada vez es horriblemente ineficaz. Por

eso, los modos Single Word DMA fueron rápidamente sustituidos por los modos DMA

Multiword. Como el nombre indica, con estos modos "una serie" de transferencias

ocurre una tras otro, un Word después de otro, evitando hacer, por separado, una

transferencia para cada palabra. Aquí están los modos de transferencia DMA

MultiWord:

Figura 8. Diferentes modos DMA Multiword

Puesto que el DMA Multiword es más eficiente, y también tiene velocidades de

transferencia más altas, los modos Single Word DMA fueron rápidamente abandonados

después de que el estándar ATA-2 fuera extensamente adoptado – estos modos fueron

quitados de las normas ATA en las especificaciones del ATA-3. Entonces todos los

28

accesos vía DMA hoy en día (incluyendo Ultra DMA) son en realidad de MultiWord. El

término "MultiWord" se da por sabido en casi todos los estándares del Serial y Parallel

ATA.

Otra característica importante del DMA es que hay dos modos diferentes de hacer

transferencias. DMA convencional es lo que llaman “tercera parte” del DMA, que

quiere decir que los controladores del DMA sobre la placa madre coordinan las

transferencias de DMA. ("la tercera parte" es el controlador DMA.) Lamentablemente,

estos controladores DMA eran viejos y muy lentos – se puede decir que no han sido

modificados durante mucho tiempo. Estos dispositivos estaban bastante ligados a los

viejos los buses de ISA, que se dejaron de usar para interfaces del disco duro por

motivos de rendimiento. Cuando los modos 1 y 2 del DMA Multiword comenzaron a

hacerse populares, se hizo el empleo del bús PCI de alta velocidad para tarjetas de

controladores IDE/ATA. En aquel punto, el viejo modo de hacer transferencias vía

DMA tuvo que ser cambiado.

Los Discos duros modernos usan “primera parte” de DMA transferencias. El término

"primera parte " quiere decir que el dispositivo periférico hace, él mismo, el trabajo de

transferir datos de la memoria y hacia ella, sin el controlador externo del DMA.

También se llama Bus Mastering, porque cuando dichas transferencias ocurren el

dispositivo se hace "amo del bús”. Bus Mastering permite al disco duro y la memoria

trabajar sin depender de los viejos controladores DMA incorporados en el sistema, o de

cualquier apoyo de la CPU. Esto requiere el empleo del bús PCI - viejos buses como

MCA también eran compatibles con el Bus Mastering, pero no son de uso abundante.

En resumen, este método permite que la transferencia de datos entre la memoria del

sistema y el disco duro sea más eficiente y también permite bajar la carga sobre la

unidad central de proceso durante las transferencias.

Curiosamente, a pesar de las ventajas del Bus Mastering, el empleo del modo 2 del busmastering multiword DMA nunca ganó realmente popularidad por varios motivos. El

más importante era el pobre apoyo a esta tecnología en los primeros dos años. La

Utilización de PIO no requería ningún trabajo y era muy simple. También, DMA no fue

compatible con la primera versión de Windows 95, entonces se tuvieron que utilizar

Drivers especiales. Los problemas con la implementación del Bus Mastering DMA en

los sistemas entre 1996 y 1998 eran numerosos: dificultades con los Drivers, el

software operaba correctamente, los lectores de CD-ROM no eran compatibles con los

Drivers, etcétera. Ante estos problemas, DMA no marcó la diferencia como ya se

esperaba. Es seguro que la reducción de uso de la CPU estaba muy bien, pero ya que la

velocidad máxima del mejor modo DMA era la misma que la del modo PIO más alto

(16.7 MB/S) no quedaba claro que DMA ofrecía unas ventajas importantes en

comparación con PIO. Dadas las pequeñas diferencias, muchos programadores

estuvieron lejos de usar DMA, para evitar las incompatibilidades y problemas de

estabilidad que muy a menudo presentaba este último.

Bus Mastering DMA finalmente entró en crisis cuando la industria siguió adelante con

los proyectos de Ultra DMA. Cuando Ultra DMA/33 duplicó la velocidad de

transferencia de la interfaz, DMA tuvo una ventaja de velocidad clara sobre PIO aparte

de otras mejoras de eficacia. La compatibilidad con el DMA se planteó de forma

correcta en Windows 9x, y la mayor parte de los problemas de los viejos Drivers fueron

eliminados. Hoy en día, el uso del Ultra DMA es un estándar en la industria.

29

6.3.1.3 ULTRA DMA

Desde luego, los discos duros se hacen más y más rápido, y la velocidad máxima del

modo 2 del DMA Multiword, 16.7 MB/S, pronto se hizo insuficiente para los discos

más rápidos. Sin embargo, los ingenieros que trabajaron para acelerar la interfaz

descubrieron que no era ninguna tarea simple. La interfaz fue diseñada para

transferencias de datos lentas - aproximadamente 5 MB/S. El aumento de la velocidad

de la interfaz (reduciendo el tiempo de ciclo) causó todos los tipos de problemas

relacionados con la interferencia. Para hacer la interfaz más rápida, unas medidas

diferentes tuvieron que ser tomadas: mejora de la eficacia de la interfaz. El resultado era

la creación de un nuevo tipo de modos de transferencia DMA, que se llamaron modos

Ultra DMA.

El avance tecnológico clave introducido en Ultra DMA era el double transition

clocking. Antes del Ultra DMA, una transferencia de datos ocurría en cada ciclo de

reloj, provocado por el pulso del reloj de la interfaz (o el “Strobe”). Con Ultra DMA, los

datos se transfieren tanto si esta a 1 o a 0 el reloj. El Doble cronometrado de las

transiciones, con algunos otros cambios menos importantes hechos, para mejorar la

eficacia, basándose en la técnica señalada, permitieron que en el rendimiento fuera

duplicado para cualquier velocidad de reloj.

Para mejorar la integridad de esta interfaz prácticamente más rápido, Ultra DMA

también introdujo el cyclical redundancy checking o CRC en la interfaz. El dispositivo

que envía los datos usa el algoritmo CRC para calcular la información redundante de

cada bloque de datos enviados en la interfaz. Este " código CRC" se envía con los datos.

En el otro extremo de la interfaz, el dispositivo que recibe los datos hace el mismo

cálculo CRC y compara el resultado con los datos que el remitente entrega. Si la

información no cuadra, esto quiere decir que los datos fueron corrompidos de algún

modo y el bloque de datos se elimina. (CRC es similar en concepto y operación al modo

de comprobación de errores de la memoria del sistema.) Si los errores ocurren con

frecuencia, el sistema puede determinar si hay problemas de hardware y así baja a un

modo más lento de Ultra DMA, o bien desactiva del todo estos modos.

La primera puesta en práctica del Ultra DMA fue especificada en el estándar

ATA/ATAPI-4 que incluía tres modos Ultra DMA, que proporcionaban hasta 33 MB/S

de rendimiento. Más tarde, se han ido añadiendo modos más rápidos del Ultra DMA.

Esta tabla muestra todos los modos actuales del UDMA, con sus tiempos de ciclo y

tasas de transferencia máximas:

Ultra DMA

Mode

Cycle Time

(nanoseconds)

Maximum Transfer

Rate (MB/s)

Defining Standard

Mode 0

240

16.7

ATA/ATAPI-4

Mode 1

160

25.0

ATA/ATAPI-4

30

Mode 2

120

33.3

ATA/ATAPI-4

Mode 3

90

44.4

ATA/ATAPI-5

Mode 4

60

66.7

ATA/ATAPI-5

Mode 5

40

100.0

ATA/ATAPI-6

Mode 6

15

133

ATA/ATAPI-7

(SATA 1.0)

Figura 9. Diferentes modos Ultra DMA

El tiempo de ciclo muestra la velocidad del reloj de la interfaz, la frecuencia del reloj es

la inversa de este número. La tasa de transferencia máxima es cuatro veces el inverso

del tiempo de ciclo - la doble transición que cronometra el medio cada ciclo tiene dos

transferencias, y cada transferencia mueve dos Bytes.

Double transition clocking es el que permite al modo 2 del UDMA tener una velocidad

de transferencia máxima de 33.3 MB/S, a pesar del hecho de tener un tiempo de ciclo

idéntico al modo 2 del MultiWord DMA, que alcanza la mitad de esta cifra. Ahora,

usted puede preguntarse: ¿si ellos usaron el Double transition clocking para alcanzar los

33.3 MB/S, cómo consiguieron los 66 MB/S, los 100 MB/S, y luego los 133 MB/S?

Bien, lo que se hizo realmente es acelerar la interfaz después. Pero el empleo del

Double transition clocking les permitió quedarse en la mitad de la velocidad que

realmente necesitaban. Sin este método, el modo 5, por ejemplo, del Ultra DMA habría

requerido un tiempo de ciclo de 20 nanosegundos en vez de 40, haciendo la puesta en

marcha mucho más difícil.

Incluso con las ventajas del Double transition clocking, funcionando por encima de los

33 MB/S finalmente se excedieron las capacidades del cable 40-conductor standard

IDE. Para usar modos superiores al 2 se requería un cable IDE especial 80-conductor.

Este cable usa los mismos 40 pins que los viejos cables, pero añade 40 líneas de tierra

entre las 40 señales originales para separarlas y para resolver problemas de corrupción

de datos y interferencias. (El cable de 80 conductores en realidad fue especificado en

ATA/ATAPI-4 con los primeros modos Ultra DMA, pero era "opcional" para los modos

0, 1 y 2.)

Hoy, todos los sistemas modernos que usan discos IDE o SATA deberían usar uno de

los modos Ultra DMA. Hay varios requisitos específicos para trabajar con Ultra DMA:

• Compatibilidad con el disco duro: El disco duro mismo debe ser compatible con

Ultra DMA. Además, el disco debe permitir el modo apropiado del Ultra DMA.

• Compatibilidad con el controlador: se debe usar un controlador capaz de hacer

transferencias Ultra DMA. Este puede ser el controlador de la interfaz

incorporado en la placa madre, o bien uno añadido en la tarjeta de la interfaz.

31

• Compatibilidad con el Sistema operativo: La BIOS y/o el sistema operativo

deben ser compatibles con las transferencias Ultra DMA, y el disco duro debe

ser programado para funcionar en Ultra DMA en el sistema operativo.

• Un cable de 80 conductores: Para modos Ultra DMA superiores al 2, se debe

usar un cable de 80 conductores. Si el sistema no reconoce ningún cable de 80

conductores se desactivan los modos 4,5 y 6 del UDMA.

En los nuevos sistemas hay pocas limitaciones con la compatibilidad del Ultra DMA,

porque el hardware es nuevo y diseñado para funcionar con este modo de tranferencias.

En los sistemas más viejos, la cosa es un poco más compleja. En teoría, los nuevos

discos deben ser compatibles con los controladores más viejos, de tal modo que si

instalamos un disco compatible con Ultra DMA en un PC viejo, esto debe causar que el

sistema funcione con un modo lento como ahora PIO 4. Lamentablemente, ciertas

placas madre no funcionan bien cuando se usa un disco UDMA, y esto puede causar

errores. Una mejora de la BIOS del fabricante de la placa madre es una idea buena, si

somos capaces de hacerlo. Otra solución sería usar una utilidad de software especial

Ultra DMA (dada por el fabricante del disco) para informar el disco duro de que no

tiene que funcionar en modos UDMA. La misma utilidad puede ser usada para permitir