Pindado - Jcee - Universitat Politècnica de Catalunya

Anuncio

Phase Locked-Loop (PLL): Fundamento y aplicaciones

R. Pindado

Universitat Politècnica de Catalunya

Departament d’Enginyeria Electrònica

E.U.E.T.I.T. c/Colón,1 08222 Terrassa.

E-mail: pindado@eel.upc.es

Resumen: La presente ponencia introduce la terminología de los circuitos de bucle de enganche de fase

(Phase Locked-Loop: PLL) analógico. Presenta el cálculo de los márgenes de frecuencia entre los que se

produce la sintonía de un PLL y examina el comportamiento del mismo dentro y fuera de sintonía. El

trabajo finaliza con una exposición de algunas de las principales aplicaciones de los circuitos PLL.

.

1. Introducción

v d = K m ViM VoM sen (ω i t + θ i ) sen(ω o t + θ o ) =

El circuito PLL es un sistema realimentado cuyo objetivo

principal consiste en la generación de una señal de salida

con amplitud fija y frecuencia coincidente con la de

entrada, dentro de un margen determinado.

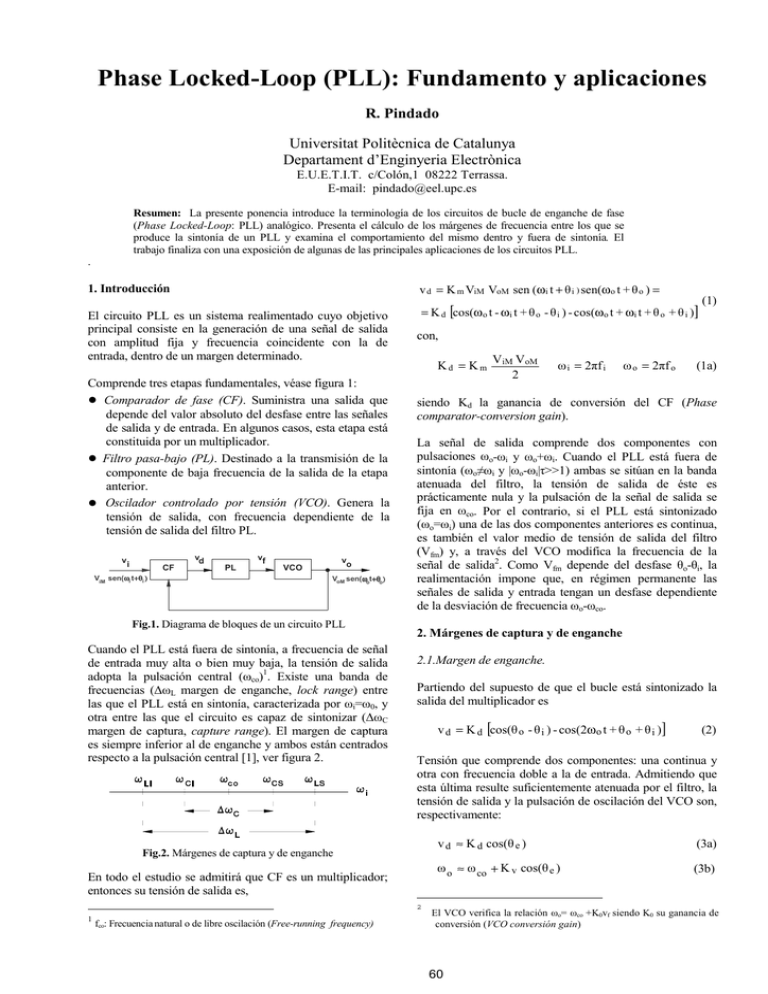

Comprende tres etapas fundamentales, véase figura 1:

● Comparador de fase (CF). Suministra una salida que

depende del valor absoluto del desfase entre las señales

de salida y de entrada. En algunos casos, esta etapa está

constituida por un multiplicador.

● Filtro pasa-bajo (PL). Destinado a la transmisión de la

componente de baja frecuencia de la salida de la etapa

anterior.

● Oscilador controlado por tensión (VCO). Genera la

tensión de salida, con frecuencia dependiente de la

tensión de salida del filtro PL.

vi

CF

ViM sen(ω

ωi t+θ

+θi )

vd

PL

vf

vo

VCO

VoM sen(ω

ωot+θ

+θo)

Fig.1. Diagrama de bloques de un circuito PLL

Cuando el PLL está fuera de sintonía, a frecuencia de señal

de entrada muy alta o bien muy baja, la tensión de salida

adopta la pulsación central (ωco)1. Existe una banda de

frecuencias (∆ωL margen de enganche, lock range) entre

las que el PLL está en sintonía, caracterizada por ωi=ω0, y

otra entre las que el circuito es capaz de sintonizar (∆ωC

margen de captura, capture range). El margen de captura

es siempre inferior al de enganche y ambos están centrados

respecto a la pulsación central [1], ver figura 2.

= K d [cos(ω o t - ω i t + θ o - θ i ) - cos(ω o t + ω i t + θ o + θ i )]

con,

Kd = Km

ω i = 2πf i

ω o = 2πf o

(1a)

La señal de salida comprende dos componentes con

pulsaciones ωo-ωi y ωo+ωi. Cuando el PLL está fuera de

sintonía (ωo≠ωi y |ωo-ωi|τ>>1) ambas se sitúan en la banda

atenuada del filtro, la tensión de salida de éste es

prácticamente nula y la pulsación de la señal de salida se

fija en ωco. Por el contrario, si el PLL está sintonizado

(ωo=ωi) una de las dos componentes anteriores es continua,

es también el valor medio de tensión de salida del filtro

(Vfm) y, a través del VCO modifica la frecuencia de la

señal de salida2. Como Vfm depende del desfase θo-θi, la

realimentación impone que, en régimen permanente las

señales de salida y entrada tengan un desfase dependiente

de la desviación de frecuencia ωo-ωco.

2. Márgenes de captura y de enganche

2.1.Margen de enganche.

Partiendo del supuesto de que el bucle está sintonizado la

salida del multiplicador es

v d = K d [cos(θ o - θ i ) - cos(2ω o t + θ o + θ i )]

(2)

Tensión que comprende dos componentes: una continua y

otra con frecuencia doble a la de entrada. Admitiendo que

esta última resulte suficientemente atenuada por el filtro, la

tensión de salida y la pulsación de oscilación del VCO son,

respectivamente:

En todo el estudio se admitirá que CF es un multiplicador;

entonces su tensión de salida es,

2

fco: Frecuencia natural o de libre oscilación (Free-running frequency)

ViM V oM

2

siendo Kd la ganancia de conversión del CF (Phase

comparator-conversion gain).

Fig.2. Márgenes de captura y de enganche

1

(1)

v d ≈ K d cos(θ e )

(3a)

ω o ≈ ω co + K v cos(θ e )

(3b)

El VCO verifica la relación ωo= ωco +K0vf siendo K0 su ganancia de

conversión (VCO conversión gain)

60

en las que θ e = θ o - θ i es el desfase entre las señales de

entrada y de salida y K v (igual a K0 Kd [2]) es la ganancia

de lazo (loop gain). Mientras el bucle esté sintonizado, la

pulsación de salida sólo puede variar entre los siguientes

límites

ω LS ≈ ω co + K v

ω LI ≈ ω co − K v

∆f L =

(4)

∆ω L

2π

vf =

Kd

ω i = ω co ±

(5)

Kv

4τ 2 K 2v + 1 + 1

2

≈ ω co ±

Kv

τ

(12)

Por tanto, las pulsaciones límite de captura son

2.2.Margen de captura.

Como el proceso de captura sucede en un régimen

transitorio, la determinación de los límites entre los que se

produce es tediosa, aunque puede recurrirse a procesos

iterativos e introducir hipótesis simplificadoras.

ω CS = ω co +

Kd

1 + (ω o - ω i ) 2 τ 2

cos (ω o t - ω i t + θ e - Φ f )

∆ω C = ω CS − ω CI = 2

Kv

τ

(13)

Kv

τ

∆f C =

∆ω C

2π

(14)

Cuando el PLL está sintonizado, la ecuación (6) degenera

en la (15a), deduciéndose (15b). La variación de la tensión

de salida del filtro y de la desviación de pulsación con el

desfase existente entre las señales de salida y entrada se

representa en la figura 2.

(6)

(6a)

Supóngase que se parte de una pulsación de entrada muy

alejada de la natural ( | ω i - ω co | τ « 1 ) de manera que el

PLL esté fuera de sintonía ( ω o ≠ ω co ) y que se varía

progresivamente ωi acercándose hacia ωco. En el momento

de la captura, en primera aproximación y como máximo, el

valor de tensión del filtro es:

Kd

ω CI = ω co −

denominado margen de captura (capture range).

con:

Φ f = arc tg (ω o - ω i )τ

Kv

τ

La captura o sintonía del PLL se realiza dentro del margen

siguiente:

La captura implica que la componente de frecuencia fo-fi

de salida del multiplicador, ver ecuaciones 1, se sitúe en la

banda pasante del filtro; por ello, su tensión de salida se

puede aproximar según las fórmulas 6. Por otra parte, el

PLL sintoniza a una frecuencia relativamente próxima a su

valor natural.

vf =

(11)

4τ 2 K 2v + 1 + 1

2

denominado margen de enganche (lock range).

vf ≈

(10)

Una nueva iteración produce los resultados (11) y (12) que

confirman la solución.

o lo que es análogo, el PLL permanece sincronizado dentro

del margen siguiente:

∆ω L = ω LS - ω LI = 2K v

4τ 2 K 2v + 1 − 1

Kv

≈ ω co ±

2

τ

1

ω i = ω co ±

τ

v f ≈ K d cos (θ e )

(15a)

ω o = ω co + K 0 v f = ω co + K v cos (θ e )

(15b)

(7)

1 + (ω o - ω i ) 2 τ 2

Por tanto, la pulsación de la tensión de salida pasa a ser,

ω o = ω co +

Kv

(8)

1 + (ω o - ω i ) 2 τ 2

o bien,

ω i − ω co =

Kv

Fig.2. Tensión de salida del filtro y desviación de pulsación en

función del desfase cuando el PLL está en sintonía.

(9)

1 + (ω co - ω i ) 2 τ 2

Dicha característica de transferencia presenta una doble

utilidad. Por una parte, determina el valor de la tensión de

salida del filtro en función del desfase entre las señales de

Haciendo uso de la aproximación 2τK v « 1 se determinan

las soluciones (10).

61

comparador de fase es continua y, por tanto, se encuentra

dentro de la banda pasante del filtro. La componente AF,

de frecuencia doble al valor de la entrada (también a la de

salida) se sitúa en la banda atenuada. En consecuencia, la

tensión de salida del filtro es prácticamente continua, con

valor dependiente del desfase θe.

entrada ya salida del PLL, ver figura 3 superior. Por otra

parte, define el desfase entre ambas señales en función de

la desviación de frecuencia cuando el PLL está

sintonizado, véase figura 3 inferior.

ωo - ωco

Kv

0

-K v

vf

Kd

0

i

Se consideran tres casos, correspondientes a sendos

valores de frecuencia de la señal de entrada incluidos en

el margen de captura. Las figuras 4 muestran algunas

formas de onda obtenidas como resultados de simulación3

durante los regímenes transitorio y permanente, a partir

de condiciones iniciales nulas.

-Kd

ωo - ωco

Kv

o-

De acuerdo con las figuras 3, el valor absoluto del

desfase θe es {inferior, igual, superior} a 90 grados según

que la desviación de frecuencia de la señal de salida con

respecto a la de libre oscilación sea {positiva, nula,

negativa}. Por otra parte, el valor medio de tensión de

salida del filtro será {positivo, nulo, negativo}, si el valor

absoluto del desfase θe es {inferior, igual, superior} a 90

grados.

vf

Kd

La tabla 2 registra los valores del desfase entre las señales

de entrada y de salida (θe) así como el valor medio de la

tensión de salida del filtro (Vfm) en los tres casos

considerados, coincidentes con los obtenidos en la

anterior figura 3.

0

-K v

0

o-

i

fi (kHz)

1

0,95

1,05

θe (º)

90

105,5

75,5

Vfm (mV)

0

-25

25

Tabla 2. Resultados del PLL en sintonía

-Kd

3.2. El PLL fuera de sintonía.

Fig.3. Doble interpretación de la característica de transferencia.

Superior: Tensión de salida del filtro en función del desfase.

Inferior: Desfase en función de la desviación de frecuencia.

Cuando el PLL está desintonizado, las dos componente

AF y BF de salida del comparador de fase se sitúan en la

banda atenuada del filtro, por lo que el valor medio de su

tensión de salida es nulo. Como consecuencia, la

frecuencia de la señal de salida se ajusta a la de libre

oscilación y, por tanto, la frecuencia de salida es

independiente de la de entrada.

3. Sintonía y desintonía del PLL

Para todos los resultados presentados en este apartado, se

utiliza un PLL con los datos expuestos en la tabla 1.

Amplitud de señales entrada y salida: ViM=VoM=5(V)

Constante de tiempo del filtro τ=10(ms).

Frecuencia de libre oscilación: fCO=1000(Hz)

Frecuencias límite de captura: fCS=1056(Hz) fCI=944(Hz)

Frecuencias límite de enganche: fLS=1200(Hz) fLI=800(Hz)

Tal proceso puede verse en las figuras 5, que muestran

resultados análogos a los del punto 2.1, correspondiendo

a dos casos de frecuencia de la señal de entrada (500 y

1500Hz) exterior al margen de captura.

4. Algunas consideraciones

Tabla 1. Datos utilizados para el PLL

El filtro pasa-bajo juega un doble papel en las prestaciones

del PLL. Por una parte, atenúa las componentes de alta

frecuencia en la salida del comparador de fase; por otra,

provee de una cierta memoria al circuito que asegura el

volver a capturar de la señal si el sistema sale de sintonía a

causa de un ruido transitorio, por ejemplo. Constituye, sin

duda, uno de los principales problemas del diseño [2].

Para la mejor comprensión de los resultados presentados,

conviene recordar que el espectro en frecuencia de la

tensión de salida del CF comprende dos componentes

cuyas frecuencias corresponden a ωo-ωi y ωo+ωi, según se

expuso en (1). Componentes que, en adelante, serán

abreviadas mediante BF y AF, respectivamente.

3.1. El PLL sintonizado.

Como se explicó en el apartado 1 de introducción, si el

PLL está en sintonía, la componente BF de salida del

3

62

Simulación realizada con TUTSIM v.6.0.

fi=1000 (Hz)

vi

vi vo

(V)

v

f

(mV)

vo

6

60

v i vo

(V)

v

f

(mV)

6

4

vo

60

vi

40

2

20

v

v

f

0

-20

-4

-6

10

15

20

2

20

25

vf

0

-2

5

40

f

0

0

4

vf

0

-2

-20

-40

-4

-40

-60

30

-6

98

t

(ms)

98,5

99

99,5

-60

100

t

(ms)

fi=950 (Hz)

vi

vi vo

(V)

v

f

(mV)

60

vo

6

v

f

(mV)

vi vo

(V)

6

vo

60

vi

4

40

4

40

2

20

2

20

0

0

0

0

v

v

f

f

-2

-20

-2

-4

-40

-4

-60

-6

-6

0

5

10

15

20

25

v

-40

98

30

t

(ms)

-20

f

98,5

99

99,5

-60

100

t

(ms)

fi=1050 (Hz)

vi

vo

vi vo

(V)

6

v

f

(mV)

60

vi vo

(V)

v

f

(mV)

6

4

40

v

v

f

0

0

-2

-20

-4

-6

5

10

15

20

40

v

20

25

60

vi

4

f

2

0

vo

f

2

20

0

0

-2

-20

-40

-4

-40

-60

-6

30

t

(ms)

98

98,5

99

99,5

Fig.4. PLL en sintonía. Tensiones de salida del filtro (vf), de entrada (vi) y salida (vo) del PLL en regímenes transitorio

(izquierda) y permanente (derecha).

63

-60

100

t

(ms)

fi=500 (Hz)

vi vo

(V)

6

vi

v

f

(mV)

vo

4

2

v

v

f

v

f

(mV)

30

vi vo

(V)

6

20

4

20

10

2

10

0

0

30

vo

vi

f

0

0

v

f

-2

-10

-2

-10

-4

-20

-4

-20

-30

-6

-6

0

5

10

97

15

t

(ms)

98

-30

100

99

t

(ms)

fi=1500 (Hz)

vi vo

(V)

6

vi

vo

4

2

v

0

v

f

(mV)

vi vo

(V)

30

6

20

4

10

2

v

f

(mV)

20

10

f

v

0

30

vo

vi

f

0

0

-2

-10

-2

-10

-4

-20

-4

-20

-30

15

t

(ms)

-6

-6

0

5

10

97

98

-30

100

t

(ms)

99

Fig.5. PLL fuera de sintonía. Tensiones de salida del filtro (vf), de entrada (vi) y salida (vo) del PLL en regímenes

transitorio (izquierda) y permanente (derecha).

5. Algunas aplicaciones del PLL.

vo

vi

(V)

A modo de ejemplo, se presentan algunas de las múltiples

aplicaciones de los circuitos de enganche de fase.

Aplicación 1. Una de las aplicaciones principales del PLL

es la detección y separación de componentes del espectro

de la señal de entrada contenidos en el margen de captura.

Por ejemplo, la tensión de entrada en el caso de la figura 6

es cuadrada con 5(V) de amplitud y frecuencia de 140(Hz)

y su séptimo armónico (980Hz y 910mV) cae dentro del

margen de captura controlando la frecuencia de la señal de

salida.

En los casos que el PLL no suministre tensión de salida

sinusoidal, triangular o cuadrada por ejemplo, el circuito

puede entrar en sintonía de una forma intempestiva o

nodeseada. Este efecto se produce para frecuencias de

entrada elevadas, al coincidir con algún armónico de la

señal de salida.

64

6

vi

vo

4

2

0

-2

-4

-6

80

85

90

95

t

(ms)

100

Fig.6. Sintonía del PLL con el séptimo armónico de una señal de

entrada cuadrada de 140 (Hz).

Aplicación 2. Constituye una aplicación interesante del

PLL el filtrado o reconstrucción de señales con altos

niveles de ruido. Por ejemplo, en la figura 7 muestra la

respuesta del circuito ante una señal de entrada de 1040

(Hz) altamente contaminada; puesto que la componente

6. Conclusiones

fundamental es la única situada dentro del margen de

captura, se produce una sintonía a su frecuencia.

Se ha explicado el funcionamiento del circuito analógico

en bucle de enganche de fase, obviando el alto grado

matemático que entraña [1-2].

v i vo

(V)

8

6

vi

Se han presentado numerosos resultados de simulación,

en condiciones de sintonía y desintonía, que avalan el

conjunto de programas desarrollado en Tutsim.

vo

4

2

Finalmente, se ha expuesto una perspectiva del amplio

conjunto de aplicaciones derivadas del empleo de los

circuitos PLL.

0

-2

-4

Referencias

-6

-8

96

97

98

99

Fig.7. El PLL ante una señal de entrada sinusoidal contaminada

de 1040 (Hz).

Aplicación 3. El fundamento de los sintetizadores de

frecuencia reside en la realimentación del circuito de un

PLL mediante un divisor de frecuencia (relación N), véase

la figura 8. Con ello se consigue la sintonía cumpliendo la

relación ϖ o = N ϖ i .

vi

CF

vd

PL

vf

VCO

ViM sen(ω

ωi t+θ

+θi )

[1]

Connelly J.A. Macromodeling with Spice. Prentice-Hall

International. 1992.

[2]

Pindado R. Electrónica analógica integrada. Introducción

al diseño mediante problemas. Marcombo. 1997.

[3]

http://www.web-ee.com/primers/primer_bottom.htm.

Artículos sobre PLL para receptores y transmisores de

HF.

[4]

http://www.radiolab.com.au Applied Radio Lbas.

Software gratuito de diseño y simulación.

[5]

www.osicom.com/notes/ddstutor.html

[6]

www.geocities.com/CapeCanaveral/5611/dds.html

[7]

www.ti.com/sc/docs/apps/logic/. Texas Instruments. Ver

digital_phase_locked_loops_plls_.html. Circuitos y notas

de aplicación.

[8]

www.chipcenter.com/onlinetools/ ChipCenter Questlik.

Notas de aplicación interactivas.

[9]

www.a-ten.com/alz/ecd.htm. Atlantis Enterprises. Amplia

referencia bibliográfica.

100 t

(ms)

vo

VoM sen(ω

ωot+θ

+θo)

Divisor de

frecuencia por N

Fig.8. Diagrama en bloques de un sintetizador de frecuencia

Aplicación 4. El PLL ofrece un amplio espectro de

aplicaciones en los campos de la desmodulación FM y la

multiplicación, división y síntesis de frecuencia. Una

aplicación típica es la modulación FSK (Frequency Shift

Keying) para la transmisión de datos mediante una

portadora que es desplazada entre dos frecuencias

preseleccionadas. El desplazamiento se consigue

controlando el VCO mediante la señal binaria de datos a

transmitir.

[10] http://www.analog.com/siteMap.html. Página de Analog

Devices. Visitar PLL Frequency Synthesizers.

[11] www.onsemi.com/pub/Collateral/MC14046B-D.PDF On

Semiconductor Hoja Técnica del circuito PLL MC 4046B.

65