Ejercicio 6

Anuncio

Ejercicio 6

1. Describir en VHDL un testbench para el sumador byteadder definido en el ejercicio 5

aplicando las siguientes especificaciones:

● El nombre del fichero serà tadder.vhd

● El nombre de la entidad será test_adder

● El nombre de la arquitectura es arbitrario

● Implementar un contador, un reloj de 100 MHz y un estímulo de reset

● El nombre de la señal de salida del contador será count

● Instanciar un sumador byteadder que añada 10 (“0A” en hexadecimal) a la salida del

contador

● El nombre de la señal de salida del sumador será sum

Se recomienda usar como plantilla el fichero tcounter.vhd.

2. Simular test_adder

3. Reportar las siguientes formas de onda para los primeros 500 ns de simulación:

● reloj

● reset

● salida del contador (con raíz decimal sin signo)

● salida del sumador (con raíz decimal sin signo)

4. Comprobar gráficamente que el reloj esté batiendo a 100 MHz

Nota: para cambiar la raíz de una señal visualizada en la ventana wave, seleccionar la señal

con el botón derecho y elegir la opción en el menu Radix (Figura 1).

Figura 1: Como cambiar la raíz de las señales visualizadas en ModelSim

Ejercicio 7

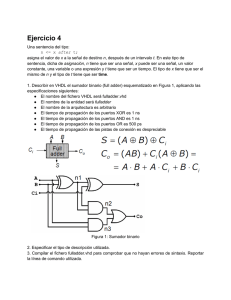

La sentencia assert en VHDL sigue la siguiente sintaxis:

assert <condición>

report “mensaje”

severity {note, warning, error, failure};

A través de esta sentencia es posible definir condiciones fuera de las cuales el simulador

debe reportar un mensaje (el ModelSim lo reporta en el transcript) y, opcionalmente, parar la

simulación. Por defecto, en ModelSim la simulación se para si el nivel de severidad es failure.

1. Añadir el siguiente proceso de verificación al testbench test_adder:

timing_check : process(clk)

begin

if clk'event and (clk = '1') then

assert unsigned(sum) = unsigned(count) + 10

report "Timing error detected"

severity error;

end if;

end process;

Para poder usar el tipo unsigned, hay que importar el package ieee.numeric_bit. Para eso

insertar las siguientes declaraciones al principio del fichero tadder.vhd:

library ieee;

use ieee.numeric_bit.all;

El proceso timing_check comprueba que en cada flanco de subida del reloj la salida del

sumador corresponda a la del contador más 10. Si no se cumple la condición, se deduce que la

salida del sumador no está todavía estable y se reportará el evento como “timing error” (Figura

2).

Figura 2: Error de temporización visualizado en ModelSim. El “slack” se define como

la diferencia entre el periodo del reloj y el retardo de preparación de datos. Un error de

temporización corresponde siempre a un slack negativo.

2. Simular una cuenta completa a 100 MHz y anotar en qué condiciones se verifican errores de

temporización.

3. Determinar la frecuencia de reloj máxima a la cual no se verifican errores de temporización.

Ejercicio 8

En VHDL es posible definir nuevos tipos de datos a través de la sentencia type. Por ejemplo,

con la sentencia

type bit_vector_8x is array (natural range <>) of bit_vector(8

downto 1);

es posible definir un vector de vectores de bit. Los contenidos de un vector de vectores pueden

ser accedidos de la siguiente forma:

signal a : bit_vector_8x(8 downto 1);

signal mi_bit : bit;

…

mi_bit <= a(i)(j);

1. Describir en VHDL un multiplicador matricial de 8 bits como esquematizado en Figura 3,

aplicando las siguientes especificaciones:

● El nombre del fichero será bytemult.vhd

● El nombre de la entidad será bytemult

● El nombre de la arquitectura es arbitrario

● La interfaz de salida/entrada será la siguiente

port (

x : in bit_vector(8 downto 1);

y : in bit_vector(8 downto 1);

z : out bit_vector(16 downto 1));

● Las señales de entrada del byteadder i serán a(i) y b(i), con a y b del tipo bit_vector_8x

● Las señales de salida del byteadder i serán s(i) y c(i), con s del tipo bit_vector_8x y c del

tipo bit_vector

● El tiempo de propagación de los puertos AND es de 1 ns

● Para la definición del multiplicador no se usarán constructos process

2. Determinar la frecuencia de reloj máxima a la cual se puede multiplicar la salida de un

contador binario por la constante 100 (“64” en hexadecimal). El experimento se hará creando

un testbench dedicado:

● El nombre del fichero será tmult.vhd

● El nombre de la entidad será test_mult

● El nombre de la arquitectura es arbitrario

● Implementar un contador, un reloj (cuya frecuencia se ajustará para no incurrir en

errores de timing) y un estímulo de reset

● El nombre de la señal de salida del contador será count

● Instanciar un multiplicador bytemult que multiplique 100 (“64” en hexadecimal) a la

salida del contador

● El nombre de la señal de salida del multiplicador será mult

Figura 3: Esquema de la arquitectura matricial del bytemult. Por coherencia con la numeración

de las señales a, b etc. el numero identificativo del primer sumador byteadder es 2. En este

esquema se numeran los bits de los vectores de 1 a 8, coherentemente con los ejercicios

anteriores, aunque en el multiplicador matricial presentado en clase se numeraban a partir del

bit 0. Por simplicidad se han omitido los sumadores del 4 al 7.