diseño de una unidad de punto flotante (fpu)

Anuncio

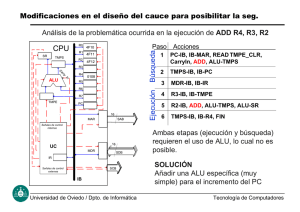

DISEÑO DE UNA UNIDAD DE PUNTO FLOTANTE (FPU) Autor: Víctor Rodríguez Ruiz Director: Sadot Alexandres Fernández Resumen El presente proyecto describe el desarrollo y la implementación de una unidad de punto flotante (FPU) embebida en una unidad aritmético lógica (ALU) de un microprocesador. Esta unidad desarrollada realizará las operaciones de suma, resta y multiplicación en coma flotante bajo el estándar IEEE-754 del mismo modo que las operaciones en punto fijo manteniendo el resto de operaciones de la ALU Se exponen de forma detallada los bloques y algoritmos diseñados para el correcto funcionamiento del conjunto así como su descripción en lenguaje VHDL. Las simulaciones realizadas para la comprobación de las operaciones se han emulado en FPGA de ALTERA. El trabajo presenta un análisis de los resultados obtenidos en las operaciones en punto flotante así como estudio de los errores. Abstract This project shows the development and implementation of an embedded floating point unit (FPU) on an arithmetic logic unit (ALU) of a microprocessor. This developed unit will perform the operations of addition, subtraction and multiplication floating point looking at the IEEE - 754 standard, replacing the corresponding fixed point, leaving unchanged the rest of the ALU operations. They are set forth in detail the blocks and algorithms designed for the proper functioning of the whole as well as its description in VHDL language. Simulations for checking operations have been emulated in ALTERA’s FPGA. The work presents an analysis of the results of floating point operations and study of errors.