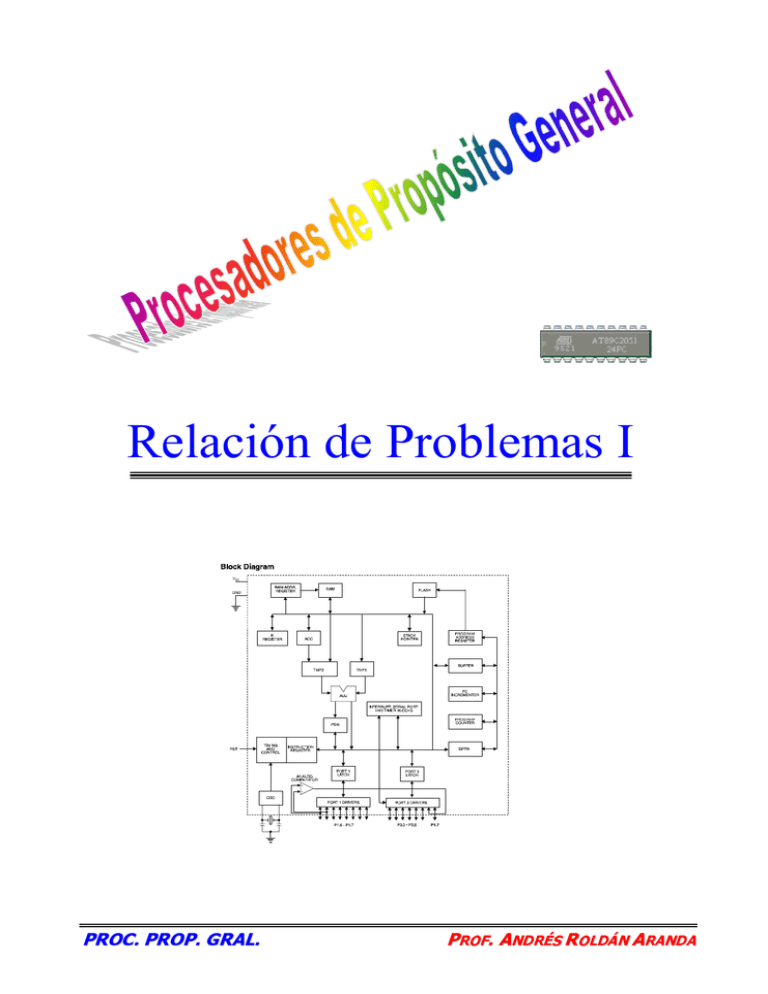

Relación de Problemas I

Anuncio

Relación de Problemas I 352& 3523 *5$/ 52) $1'5e6 52/'È1 $5$1'$ 3 352& 3523 *5$/ 1. ,QJ 7pF ,QI 6LVWHPDV Realizar el cálculo del tiempo que transcurre durante la ejecución del bloque de instrucciones sombreado, en función del contenido de los registros y del tiempo de ejecución de las instrucciones correspondientes al siguiente código, considerando que la frecuencia del reloj del microcontrolador es de 12 MHz. NAME RETARDO ; Rutina ejemplo de utilización de un retardo SoftWare INICIO: SAL0: SAL1: SAL2: MOV R0, MOV R1, MOV R2, DJNZ R2, #55H #85H #0FFH SAL2 DJNZ R1, SAL1 DJNZ R0, SAL0 ; Se carga el Registro R0 con #55H ; Se carga el Registro R1 con #85H ; Se carga el Registro R2 con #FFH ; Decrementa R2 y repite el bucle ; hasta que R2==0 ; Decrementa R1 y repite el bucle ; hasta que R1==0. Por cada lazo de R1, ; se ejecuta FFH veces el bucle R2 ; Decrementa R0 y repite el bucle ; hasta que R0==0. Se decrementa 85H ; veces R1 y 85H*FFH veces R2 END 2. Realizar la suma de dos números de 16 bits. El byte alto del primer operando se encuentra en la dirección D:71H y el byte bajo en la D:70H, del mismo modo, el byte alto del segundo operando se encuentra en la dirección D:73H y el byte bajo en la D:72H. El byte alto del resultado se situará en la posición D:75H y el bajo en la D:74H y en la D:76H el posible acarreo. 3. Realizar un código similar al anterior salvo que los datos de entrada y de salida se expresen en BCD (Decimal Codificado en Binario). 4. Convertir 11 números codificados en ASCII en Decimal. Los números están situados en las posiciones de memoria RAM Interna comprendidas entre la 60H – 6AH. Colocar los resultados en las posiciones D:40H4AH. 5. Realizar el ejercicio anterior modificando la rutina de conversión. En esta ocasión: • • 6. Conversión de caracteres ASCII a números hexadecimales. Conversión de números hexadecimales a caracteres ASCII. Se tiene una tabla de datos en la memoria externa de código, ROM, de la posición C:1000H – 1050H. Escribir un programa Realizar un programa para buscar el dato de mayor valor de la tabla y situarlo en la posición D:60H de la memoria RAM Interna. NOTA: Para realizar el acceso a la memoria externa de programa se deben utilizar las instrucciones: • • MOVC A, @A+DPTR MOVC A, @A+PC | A | A Õ ((A) + (DPTR)). Õ ((A) + (PC)). Ejemplo: Acceso sobre una tabla de 4 datos. ... 90H 91H 92H 93H ... MOV A, #01H CALL Dir. Rutina .... .... A0H A1H A2H A3H A4H A5H A6H ... INC A MOVC A,@A+PC RET DATO 1 DATO 2 DATO 3 DATO 4 ... MOV CALL A, TABLA TABLA: INC MOVC RET DATO1 DATO2 DATO3 DATO4 #01H A A,@A+PC MAPA MEMORIA CÓDIGO 352& 3523 *5$/ 3URI $QGUpV 5ROGiQ $UDQGD 352& 3523 *5$/ 7. Dada la siguiente tabla de direccionamientos explicar las diferencias entre ellos. <byte> <byte> <byte> <byte> 8. ,QJ 7pF ,QI 6LVWHPDV Direc @Ri Ri # data Direccionamiento directo. Direccionamiento indirecto a través de los registros R0 y R1. Direccionamiento por registro. Direccionamiento inmediato. Constante de 8 o 16 bits. Rellenar la tabla de operaciones aritméticas siguiendo el patrón propuesto en la primera línea. Nemónico ADD A, <byte> ADDC A, <byte> SUBB A, <byte> INC A INC <byte> INC DPTR DEC A DEC <byte> MUL AB DIV AB Operación A=A+ <byte> Dir Modos de direccionamiento Ind Reg Inm √ √ √ √ Ciclos de Ejecución 1 C Flags afectados OV AC √ √ √ A= INT [A/B] B= mod [A/B] DA A 9. Rellenar la tabla de operaciones lógicas siguiendo el patrón propuesto en la primera línea. Nemónico ANL A, <byte> ANL <byte>, A ANL<byte>,#data ORL A, <byte> ORL <byte>,a ORL <byte>,#data XRL A, <byte> XRL <byte>, A XRL <byte>,#data CLR A CPL A RL A RLC A RR A RRC A SWAP A Operación A=A & <byte> Dir Modos de direccionamiento Ind Reg Inm √ √ √ √ Ciclos de Ejecución 1 C Flags afectados OV AC 10. ¿ Qué utilidad puede tener la utilización de la instrucción MOV DPTR, #data(16 bits) ? 11. ¿ Qué diferencias hay entre las instrucciones MOVX A,@DPTR y MOVC A,@A+DPTR ? 12. Identificar y representar gráficamente las distintas partes de que consta la memoria de datos interna e indicar la misión que cumple en el sistema. 13. Indicar en qué zona o zonas de la memoria se escribe el dato implícito en las siguientes instrucciones. Hacer una representación gráfica del estado de la memoria tras la ejecución de todas las instrucciones. 1. 2. 3. 4. MOV 25H, #46H MOV R0, #25H Y MOV @R0, #46H MOV 85H, #3Ah MOV R1, #25 Y MOV @R1, #3AH 14. ¿ Cuántos bancos de registros tienen los microcontroladores genéricos de la familia MCS-51 ? ¿ Cuál es el banco por defecto y por qué ?. Indicar las instrucciones a ejecutiar para cambiar al banco Nº 3. 15. Explicar la función de la señal RESET e indicar cómo inicializa los siguientes registros: 352& 3523 *5$/ 3URI $QGUpV 5ROGiQ $UDQGD 352& 3523 *5$/ ,QJ 7pF ,QI 6LVWHPDV Registro 7 6 5 4 32 1 0 PC ACC B PSW SP DPTR PO P1 P2 P3 16. Escribir la instrucción que resuelva la condición de salto relativo cuando el flag FO overflow se halla activado. 17. Los saltos relativos están situados dentro del rango comprendido entre –128 y +127 byte. ¿ Cómo se procedería si el salto que se tuviera que realizar fuese de 300 bytes ? Ilustrar con un ejemplo el modo de proceder. 18. Establecer las diferencias entre las instrucciones JMP con los prefijos S,L y A. 19. ¿ Cuál es la diferencia entre las instrucciones RET y RETI ? 20. ¿ Qué chequea la CPU para realizar los saltos condicionales JZ y JNZ ?. Justificar la respuesta. 21. Señalar las diferencias entre las instrucciones: CJNE A, <byte>, #data, rel y CJNE <byte>, #data, rel. 22. Explicar el proceso de generación de código a partir de un “fichero.asm”. Comenta el contenido de los ficheros generados por el ensamblador y el linkador. 23. A partir del esquema eléctrico denominado ESTACIÓN DE CONTROL DE RIEGO responder a las siguientes preguntas: 1. 2. 3. 4. 5. 6. 7. 8. 9. ¿ Cuál debe ser la posición del interruptor que produce el RESET en el microcontrolador, S2, para que el circuito funcione correctamente y ejecute las instrucciones ? ¿ Cuál debe ser la posición del interruptor S1, para que el circuito ejecute las instrucciones contenidas en la memoria ROM interna ? ¿ Y para que lo haga con las instrucciones de la memoria ROM EXTERNA? Obtener el mapa de memoria de datos y de programa, detallando las posiciones donde reside el control de las líneas que comandan los diferentes LED, 7 Segmentos, Entradas y Salidas. Describir una rutina en ensamblador que encienda/apague cada uno de los LED de la ESTACION de D Riego. Describir una rutina que permita detectar y reconocer la pulsación de una tecla del teclado 4·4 conectado directamente al P1. Describir una rutina que permita representar 4 números BCD en cada uno de los 7 Segmentos contenidos en el sistema. Realizar un programa en ensamblador que represente en pantalla la tecla pulsada. A los caracteres #, *, F1, F2, F3, F4 se le asignarán los códigos BCD, A, B, C, D, E, F respectivamente. Realizar un programa en ensamblador que represente en pantalla las 4 últimas teclas pulsadas. Realizar una rutina que permita hacer sonar al ALTAVOZ con un tono de 1 KHz si se detecta un ‘1’ en la señal de entrada ERROR. Nota: Para excitar al altavoz y generar un tono de 1KHz se debe utilizar una rutina de retardo o una interrupción de tiempo que genere una secuencia como la representada en la figura: P3.0 Speaker 1 mS 352& 3523 *5$/ 3URI $QGUpV 5ROGiQ $UDQGD 352& 3523 *5$/ ,QJ 7pF ,QI 6LVWHPDV 10. La situación existente en las patillas INT0 e INT1 ¿ es correcta según las recomendaciones del fabricante ?¿ Cuál sería su correcto conexionado ? 352& 3523 *5$/ 3URI $QGUpV 5ROGiQ $UDQGD