Summary

Anuncio

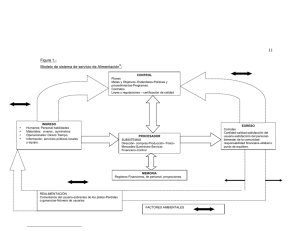

1 Summary Comparators The function of a comparator is to compare the magnitudes of two binary numbers to determine the relationship between them. In the simplest form, a comparator can test for equality using XNOR gates. Figure 6--15 Floyd, Digital Fundamentals, 10th ed Basic comparator operation. (Equality) © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Figure 6--16 Logic diagram for equality comparison of two 2-bit numbers © 2009 Pearson Education 2 Summary DM74LS85: 4-Bit Magnitude Comparator IC comparators provide outputs to indicate which of the numbers is larger or if they are equal. The bits are numbered starting at 0, rather than 1 as in the case of adders. Cascading inputs are provided to expand the comparator to larger numbers. A0 A1 A2 A3 Cascading inputs B0 B1 B2 B3 0 COMP A 3 A>B A>B A=B A=B A<B A<B 0 A 3 Outputs The IC shown is the 4-bit 74LS85. Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 3 Summary Comparators IC comparators can be expanded using the cascading inputs as shown. The lowest order comparator has a HIGH on the A = B input. LSBs A0 A1 A2 A3 +5.0 V B0 B1 B2 B3 Floyd, Digital Fundamentals, 10th ed MSBs 0 COMP A 3 A>B A>B A=B A=B A<B A<B 0 A 3 A4 A5 A6 A7 B4 B5 B6 B7 0 COMP A 3 A>B A>B A=B A=B A<B A<B 0 A Outputs 3 © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved © 2009 Pearson Education 4 Salidas bajo-activas: ‘realizan’ su función con un ‘0’: PEQQ_L output is asserted if all eight input-bit pairs are equal. PGTQ_L output is asserted if P[7–0] > Q[7–0]. © 2009 Pearson Education © 2009 Pearson Education 5 Summary Decoders Decodificar es convertir un código de entrada de n bits a un código de salida de m bits tal que n<=m<=2n. El decodificador más habitual aquel en el que m= 2n , de forma que cada código de entrada tiene asociada una salida, que será la unica activa cuando este código esté presente en la entrada. Decodificador de 1-a-2 Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Decodificador de 2-a-4 (1-de-4) Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 6 Decodificador de 2-a-4 con entrada de habilitación Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Decodificador de 4-a-16 (1-de-16) con salidas activas a nivel bajo Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 7 Decodificadores en cascada: decodificador de 5-a-32 usando dos de 4-a-16 (con ‘enable’ bajo-activo) Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Decodificador de 4-a-16 usando dos de 2-a-4 2x4 Dec D0 D1 D2 D3 2x4 Dec D4 D5 D6 D7 2x4 Dec D8 D9 D10 D11 2x4 Dec D12 D13 D14 D15 EN EN A0 A1 A2 A3 EN 2x4 Dec EN Floyd, Digital Fundamentals, 10th ed EN © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 8 Ejemplo de aplicación Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Summary Decoders X/Y A specific integrated circuit decoder is the 74HC154 (shown as a 4-to-16 decoder). It includes two active LOW chip select lines which must be at the active level to enable the outputs. These lines can be used to expand the decoder to larger inputs. 0 1 2 3 A0 A1 A2 A3 4 5 6 7 1 2 8 4 8 9 10 11 12 13 CS1 CS2 14 & 15 EN 74HC154 Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 9 74LS138: 1-OF-8 DECODER Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Uso del decodificador tal cual Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 10 Decodificador de 4-a-16 con dos 74LS138 Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Summary BCD/DEC BCD Decoders BCD-to-decimal decoders accept a binary A0 coded decimal input and activate one of ten A1 A2 possible decimal digit indications. A3 (15) (14) (13) (12) 0 1 2 3 4 5 6 7 8 9 1 2 4 8 Assume the inputs to the 74HC42 decoder are the sequence 0101, 0110, 0011, and 0010. Describe the output. (1) (2) (3) (4) (5) (6) (7) (9) (10) (11) 74HC42 All lines are HIGH except for one active output, which is LOW. The active outputs are 5, 6, 3, and 2 in that order. Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 11 Summary BCD Decoder/Driver (no imprimir los 0’s no significativos) Another useful decoder is the 74LS47. This is a BCD-toseven segment display with active LOW outputs. VCC LT provoca que se iluminen todos los segmentos. RBI provoca que se apagen todos los segmentos cuando hay un cero en la entrada BCD . (16) BCD/7-seg BI/RBO (7) (1) (2) BCD inputs (6) RBO se activa cuando hay un cero en la entrada BCD y está activa RBI. Floyd, Digital Fundamentals, 10th ed 8 (3) (5) LT RBI a b c d e f g 1 2 4 LT RBI (4) BI/RBO (13) (12) (11) (10) (9) (15) (14) Outputs to seven segment device (8) 74LS47 GND © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Summary BCD Decoder/Driver The 74LS47 features leading zero suppression, which blanks unnecessary leading zeros but keeps significant zeros as illustrated here. The BI/RBO output is connected to the RBI input of the next decoder. 0 0 0 0 0 RBI LT 8 4 2 1 74LS47 0 0 0 0 0 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO g f e d c b a BI/RBO Blanked Blanked Floyd, Digital Fundamentals, 10th ed 0 0 0 1 1 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO 1 0 0 0 0 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO Depending on the display type, current limiting resistors may be required. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 12 Summary BCD Decoder/Driver Trailing zero suppression blanks unnecessary trailing zeros to the right of the decimal point as illustrated here. The RBI input is connected to the BI/RBO output of the following decoder. 0 1 0 1 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO 0 1 1 1 RBI LT 0 0 0 0 8 4 2 1 RBI LT 74LS47 8 4 2 1 RBI LT 74LS47 8 4 2 1 74LS47 g f e d c b a BI/RBO g f e d c b a BI/RBO g f e d c b a BI/RBO 1 0 0 Decimal point Floyd, Digital Fundamentals, 10th ed 0 0 0 0 Blanked Blanked © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Summary Codificadores An encoder accepts an active logic level on one of its inputs and converts it to a coded output, such as BCD or binary. The decimal to BCD is an encoder with an input for each of the ten decimal digits and four outputs that represent the BCD code for the active digit. The basic logic diagram is shown. There is no zero input because the outputs are all LOW when the input is zero. Floyd, Digital Fundamentals, 10th ed 1 A0 2 3 4 5 6 7 8 A1 A2 A3 9 © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 13 Summary Encoders Show how the decimal-to-BCD encoder converts the decimal number 3 into a BCD 0011. The top two OR gates have ones as indicated with the red lines. Thus the output is 0111. 1 0 1 2 0 1 3 1 4 5 6 7 8 9 Floyd, Digital Fundamentals, 10th ed 0 0 0 0 0 0 0 0 A0 A1 A2 A3 © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Summary Codificador de 10-a-4 (decimal-BCD) con prioridad The 74HC147 is an example of an IC encoder. It is has ten active-LOW inputs and converts the active input to an V active-LOW BCD output. CC (16) This device is offers additional flexibility in that it is a priority encoder. This means that if more than one input is active, the one with the highest order decimal digit will be active. Decimal input (11) (12) (13) (1) (2) (3) (4) (5) (10) HPRI/BCD 1 2 3 4 5 6 7 8 9 74HC147 The next slide shows an application … Floyd, Digital Fundamentals, 10th ed 1 2 4 8 (9) (7) (6) (14) BCD output (8) GND © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 14 Summary VCC Uso Keyboard encoder R7 7 R8 8 R9 9 HPRI/BCD R4 4 R5 5 R1 1 6 R2 2 1 2 4 8 BCD complement of key press 74HC147 R3 3 R0 The zero line is not needed by the encoder, but may be used by other circuits to detect a key press. 0 Floyd, Digital Fundamentals, 10th ed 1 2 3 4 5 6 7 8 9 R6 © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 74LS148: Codificador de 8-a-3 con prioridad EI es la entrada de ‘enable’ (habilitación) EO es la salida de enable, se activa cuando el codificador está habilitado y ninguna de sus 8 entradas de valores está activa. Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved 15 Tabla de verdad Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved Decodificador de 16-a-4 usando codificadores 74LS148 Floyd, Digital Fundamentals, 10th ed © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved