Compuertas lógicas y diseño de circuitos lógicos

Anuncio

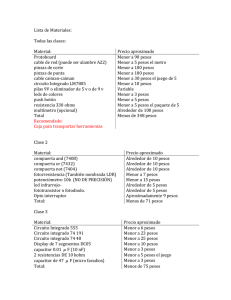

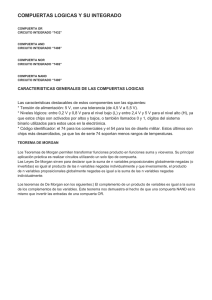

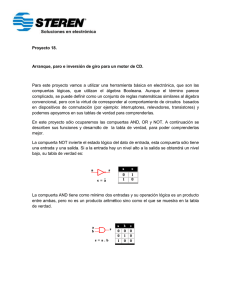

Unidad Compuertas lógicas y diseño de circuitos lógicos Introducción Los circuitos digitales binarios o circuitos lógicos se encuentran diseñados para operar solamente con dos estados diferentes, claramente diferenciados entre sí. Desde el punto de vista tecnológico es mucho más simple y confiable operar de esta forma. Dado que las señales de entrada y las señales de salida de un circuito digital sólo pueden presentar uno de dos estados posibles, dichas señales son susceptibles de ser representadas matemáticamente mediante una variable lógica y por lo tanto, utilizar el álgebra booleana como herramienta matemática al describir la relación entre las entradas y salidas del circuito. Otra herramienta para describir el funcionamiento de un circuito digital es la tabla de verdad, que se utiliza para mostrar los valores de salida que el circuito debe lograr para cada combinación de valores de las entradas. En cuanto a la implementación, describiremos el funcionamiento de las compuertas lógicas, que son circuitos electrónicos que realizan operaciones lógicas simples. Las compuertas lógicas constituyen los bloques funcionales básicos para la construcción de circuitos digitales más complejos. Debe tenerse en cuenta que en forma estricta el término “digital” no implica necesariamente que sea “binario”. Sin embargo, nos ocuparemos únicamente de sistemas digitales binarios y por tal razón tomaremos ambos términos como sinónimos durante el desarrollo de los temas que se exponen a partir de esta unidad. Circuitos digitales Figura 3.1 Diagrama en bloques de un circuito lógico digital de n señales de entrada y m señales de salida. La Figura 3.1 muestra el diagrama en bloques de un circuito digital genérico que de acuerdo a los valores de n señales de entrada produce los valores de m señales de salida. El funcionamiento del circuito digital consiste en generar, a partir de las señales de entrada, las señales de salida cuyos valores cumplan las relaciones planteadas como objetivo del circuito. Debido a que las señales de entrada y de salida de los circuitos digitales son señales que sólo pueden presentar dos valores distintos, se les denomina en forma general señales lógicas y por extensión, los circuitos digitales se conocen también como circuitos lógicos. 51 Representación de valores binarios 0 1 No Si Falso Verdadero Deshabilitado Habilitado Abierto Cerrado Apagado Encendido Voltaje alto Voltaje bajo Tabla 3.1 Representación de valores binarios mediante los valores lógicos 0 y 1. Cualquier sistema cuyo funcionamiento se encuentre basado en señales que adoptan solamente dos estados posibles puede ser descrito mediante variables binarias. A su vez, los valores que adoptan dichas variables binarias se pueden designar con distintos nombres, de acuerdo al tipo de sistema. Por ejemplo, al utilizar una variable binaria para describir el funcionamiento de una lámpara nos referiremos a los valores que toma la variable binaria con los términos “encendido-apagado”, ya que describen en forma coherente el estado de la lámpara. Otros sistemas utilizan otros nombres para designar los valores del estado, tales como abierto-cerrado, verdadero-falso, conduce-no conduce, activado-desactivado, etc. Como veremos a continuación, para simplificar esta diversidad se define una forma de representación con valores lógicos convencionales que permiten describir los estados de cualquier señal, variable o sistema. Por otra parte, los sistemas digitales se implementan con circuitos electrónicos, de manera tal que dichos circuitos deben utilizar una forma de representar eléctricamente las señales lógicas mediante niveles de tensión. Otra forma manera de representar las señales lógicas es mediante gráficas, que utilizaremos principalmente para describir la evolución temporal, es decir, los cambios que presenta una señal lógica a lo largo del tiempo y sus relaciones con otras señales lógicas del sistema. Representación de valores binarios mediante valores lógicos En el estudio de los circuitos digitales se utiliza la representación de valores binarios mediante valores lógicos, para simplificar la descripción de sus señales de entrada y salida. Esta representación consiste en asociar en forma convencional el 0 con uno de los valores binarios y el 1 con el otro valor. Cuando se utilizan con este fin, estos símbolos se denominan 0 lógico y 1 lógico, respectivamente. La Tabla 3.1 ejemplifica algunos casos comunes. Ejemplo Para apreciar en forma práctica el uso de valores lógicos, consideremos nuevamente el funcionamiento de una linterna. En la Figura 3.2 se muestra el circuito formado por una batería que suministra un valor de tensión Vcc y una llave o interruptor que al accionarse hacia la posición A ó B, controla el encendido de la lámpara, representada por la resistencia R. Figura 3.2 Circuito de una linterna eléctrica Como vimos anteriormente, cuando la llave se encuentra en la posición B, -llave abierta- la lámpara está apagada y el valor de tensión en el punto A es cero volts, ya que no hay caída de tensión en la resistencia R. Al accionar la llave hacia la posición A –llave cerrada-, la lámpara se enciende y el valor de tensión en el punto A pasa a ser +Vcc, ya que queda conectado al borne positivo de la fuente de alimentación. 52 Ejemplo (continuación) En este sencillo ejemplo, la posición de la llave –variable de entrada- es lo que define la emisión de luz en la lámpara –variable de salida- La representación de los valores de la variable de entrada mediante una variable lógica x, permite evaluar el estado de la variable de salida, f(x). El uso de los valores lógicos 0 y 1 describe la relación entre la entrada y la salida con la misma representación, como se resume en Tabla 3.2 ENTRADA (Estado de la llave) SALIDA (Estado de la lámpara) ENTRADA x SALIDA f(x) Abierta Apagada 0 0 Cerrada Encendida 1 1 Tabla 3.2 Representación del estado de la llave y de la lámpara mediante valores lógicos. Representación de valores binarios mediante niveles de tensión eléctrica La asignación de los niveles de tensión para representar los valores lógicos es convencional. Utilizar un valor de tensión BAJO para el 0 lógico y un valor de tensión ALTO para el 1 lógico, resulta más natural y se denomina lógica positiva. La asignación opuesta, conocida como lógica negativa, consiste en utilizar un valor de tensión BAJO para el 1 lógico y un valor de tensión ALTO para el 0 lógico. En electrónica digital, los valores binarios se representan eléctricamente mediante dos niveles de tensión distintos, que permita diferenciar fácilmente un valor de otro. En primer lugar, a los valores binarios se les asigna los valores lógicos 0 y 1. Luego se utiliza un nivel de tensión BAJO para representar el valor lógico 0 y un nivel de tensión ALTO para representar el valor lógico 1. Debido a esta asociación con los valores lógicos, los niveles ALTO y BAJO se denominan niveles lógicos de tensión. Es decir que, en los circuitos digitales electrónicos, las señales de entrada y de salida deben tomar los valores de tensión predefinidos que sirven para representar el 0 lógico y el 1 lógico. Por ejemplo, un valor de voltaje de 0 V podría representar el 0 lógico y +5 V podría representar el 1 lógico. Generación eléctrica de una señal digital Para representar eléctricamente una señal digital se necesita un dispositivo cuyo funcionamiento permita generar dos valores de tensión distintos. En términos de niveles lógicos nos referimos a estos valores de tensión como ALTO y BAJO, independientemente del valor de tensión en sí. Una forma simple de generar estos valores distintos es mediante una modificación del circuito divisor de tensión en el cual se reemplaza una de las resistencias por una llave o interruptor. Según se reemplace una u otra resistencia, se consigue una configuración de resistencia de pull up o resistencia de pull down. La Figura 3.3b muestra la configuración de resistencia de pull up. Observe que cuando la llave L se encuentra cerrada, Vs = 0V y cuando se encuentra abierta, la tensión de salida es Vs = Vcc. Por esta característica la resistencia Rt se denomina resistencia de pull up, porque “levanta” o “tira hacia arriba” el valor de la tensión de salida Vs cuando se abre la llave L. La Figura 3.3c muestra la configuración de resistencia de pull down. En este circuito, la llave L en posición cerrado produce Vs = Vcc (nivel ALTO). La llave L en posición abierto hace que Vs = 0 V (nivel BAJO). Por esta razón, la resistencia Rb se denomina resistencia de pull down, porque es la que “tira hacia abajo” el valor de la tensión de salida Vs cuando se abre la llave L. 53 Figura 3.3 Generación de una señal digital mediante circuitos con llave y resistencia de pull up o de pull down. Como los circuitos en configuración de pull up y pull down permiten obtener dos estados marcadamente diferenciados, estos circuitos también se denominan como circuitos generadores de un bit. Circuitos con pulsadores Los circuitos de pull up y pull down de la Figura 3.3 presentan dos estados “de reposo”, dado que la llave L puede quedar en cualquiera de las posiciones por tiempo indeterminado, ya sea abierto o cerrado. Para cambiar la llave de una posición a otra se requiere siempre una acción mecánica externa, pero cuando la acción mecánica desaparece, la llave queda en la posición a la cual fue cambiada y no modifica ese estado si no se actúa nuevamente sobre ella. Un dispositivo que cumple una función similar a la llave o interruptor es el pulsador. Un pulsador funciona como un interruptor eléctrico, pero presenta una posición de reposo única, de manera tal que al accionar el pulsador, el dispositivo cambia de posición al igual que la llave, pero al desaparecer la acción mecánica, el pulsador retorna por sí mismo a su posición anterior (posición normal o de reposo). Para ello, el pulsador contiene un muelle o resorte que es comprimido por la fuerza mecánica que actúa sobre él para sacarlo de su posición normal. Al cesar la acción externa, el muelle o resorte desplaza el contacto hacia su posición de reposo. Ejemplos cotidianos de este tipo de dispositivo son el pulsador de timbre comúnmente instalado en la entrada de las viviendas y las teclas de dispositivos digitales tales como calculadoras, controles remotos, teléfonos celulares, computadoras, etc. Según su posición de reposo, un pulsador puede ser normalmente cerrado (NC) o normalmente abierto (NA). En la Figura 3.4 se muestran los símbolos y funcionamiento de ambos tipos. La Figura 3.5 muestra como ejemplo un circuito con resistencia de pull up y un pulsador normalmente abierto. Cuando se acciona el pulsador, éste cambia de su posición normal (abierto) a posición cerrado y al desaparecer la fuerza de actuación, el pulsador retorna a su posición normal. Los valores de Vs para cada una de las posiciones del pulsador se deducen al igual que para el caso del circuito con llave, ya que eléctricamente tienen el mismo comportamiento. 54 Circuitos con pulsadores (continuación) Figura 3.4 Símbolos y funcionamiento de los tipos de pulsadores Figura 3.5 Circuito de resistencia de pull up con un pulsador NA Intervalos de tensión de niveles lógicos Figura 3.6 Conexión de una carga a la salida de un circuito con resistencia de pull up. Circulación de corriente en nivel ALTO. Las configuraciones con resistencia de pull up o de pull down permiten obtener los niveles de tensión ALTO y BAJO con valores bien diferenciados, como se muestra en la Figura 3.3. Sin embargo, los valores de salida Vs descritos ahí corresponden a los valores que presentarían tales circuitos en vacío. Normalmente la salida de un circuito o dispositivo electrónico digital no permanecerá en vacío, sino que será utilizada para manejar la entrada de otro dispositivo, es decir, tendrá un funcionamiento en estado de carga. Mostraremos a continuación cómo la carga y la circulación de corriente en el punto de interconexión puede modificar los valores ALTO y BAJO Considere, por ejemplo, el circuito con resistencia de pull up de la Figura 3.6 al cual se le ha conectado como carga un indicador luminoso compuesto por la asociación serie de una resistencia R1 y un diodo led D1. Esta asociación serie se conecta entre la salida Vs del circuito y masa. Con el circuito en vacío, al colocar la llave L en posición cerrado el circuito genera el nivel BAJO (Vs = 0V) y con L en la posición abierto el circuito genera el nivel ALTO (Vs = Vcc). Con el circuito cargado, la llave L en la posición cerrado genera Vs = 0V, igual que cuando el circuito esta en vacío. Pero al colocar la llave en posición abierto, existe una derivación de corriente I hacia la carga, y tenemos que: = 55 − . Es posible atenuar en parte el efecto de los factores que provocan variaciones en los valores de tensión presentes en un circuito agregando mejoras al diseño y utilizando componentes de mejor calidad. Sin embargo, tales factores son inevitables. Actualmente la fabricación de la mayoría de los circuitos integrados se basa en tecnología CMOS. Este valor es menor al que entrega como salida el circuito en vacío. O sea que, con el circuito cargado, el nivel ALTO no será Vcc, sino un valor menor, debido a la caída de tensión en Rt. Esta caída de tensión depende del valor de la resistencia de pull up y de la intensidad de la corriente I que consume la carga. Mientras el valor de Vs no descienda demasiado por debajo de Vcc, seguirá siendo útil para representar un nivel ALTO. Por otra parte, en la práctica, los valores de tensión eléctrica presentes en un circuito cualquiera pueden sufrir variaciones debido a factores tales como el ruido eléctrico, variación de valores nominales de los componentes, variaciones debido a cambios de temperatura, etc. En resumen, el estado de carga del circuito y las fluctuaciones de tensión que presentan los circuitos reales pueden afectar el valor de tensión de los niveles ALTO y BAJO. Por esta razón, el 0 y el 1 lógicos no se representan con valores exactos de tensión sino mediante intervalos de tensión. Es decir, los valores de tensión con los que se representan los niveles ALTO y BAJO no se restringen a los valores exactos Vcc y 0V, sino que se definen intervalos cercanos a estos límites, pero lo suficientemente distintos entre sí como para asegurar que siempre puedan distinguirse los niveles ALTO y BAJO que representan el 1 lógico y el 0 lógico, respectivamente. Los intervalos de tensión que representan los valores lógicos 0 y 1 en las señales de entrada dependen de la tecnología utilizada en la implementación de los circuitos digitales. Las tecnologías actuales de fabricación de circuitos integrados son TTL y CMOS. Estas tecnologías se diferencian principalmente por el tipo de transistores que utilizan. La tecnología TTL utiliza transistores bipolares, que son los que ya hemos descrito y la tecnología CMOS utiliza otro tipo de transistores, denominados de efecto de campo. Esto implica diferentes características entre ambas tecnologías en cuanto al consumo eléctrico, tensión de alimentación, velocidad de operación, etc. La Figura 3.7 muestra los intervalos de tensión que se utilizan en las tecnologías TTL y CMOS para representar valores lógicos de señales de entrada. Cada tecnología define también los intervalos que utilizan para representar valores lógicos de señales de salida. Figura 3.7 Intervalos de tensión para señales de entrada. a) Tecnología TTL. b) Tecnología CMOS. Los circuitos digitales de tecnología TTL funcionan con una tensión de alimentación de 5 V. Los valores lógicos de una señal de entrada se representan con los siguientes intervalos de tensión: El 0 lógico se representa con un valor de tensión entre 0 V y 0,8 V El 1 lógico se representa con un valor de tensión entre 2 V y 5 V Los valores de tensión entre 0,8 V y 2 V son indeterminados. Los circuitos basados en tecnología CMOS, utilizan tensiones de alimentación desde 3 V hasta 18 V. Si tomamos una tensión de alimentación de 5 V para comparar con los rangos TTL, los valores lógicos de una señal de entrada se representan con los siguientes intervalos de tensión: 56 El 0 lógico se representan con un valor de tensión entre 0 V y 1,5 V El 1 lógico se representa con un valor de tensión entre 3,5 V y 5 V Los valores de tensión entre 1,5 V y 3,5 V son indeterminados. Los valores de tensión ubicados en la región indeterminada pueden ser interpretados aleatoriamente como 1 o como 0, provocando un funcionamiento impredecible en el circuito. Por esta razón, las señales de entrada de circuitos digitales deben presentar valores de tensión en alguno de los intervalos definidos y no en la región indeterminada, a excepción de las transiciones entre un intervalo y otro. Representación gráfica de valores lógicos y niveles lógicos Una forma de representación muy utilizada en la descripción de sistemas digitales consiste en graficar el nivel lógico que adoptan las señales en función del tiempo. Estas gráficas se conocen como diagramas temporales, diagramas de sincronismo o diagramas de temporización y consisten en representaciones simplificadas de la evolución temporal de una señal lógica. Este tipo de diagramas utiliza solamente los niveles lógicos ALTO y BAJO en lugar de representar los valores exactos de tensión eléctrica. Otra simplificación adoptada generalmente consiste en representar los cambios de un nivel lógico a otro considerando que las transiciones ocurren de manera instantánea, dando lugar a formas de onda cuadrada. En la Figura 3.8 se muestra un ejemplo de diagrama temporal de una señal lógica designada como X. En el instante de tiempo inicial t0, la señal presenta nivel lógico BAJO, valor que se mantiene sin cambios hasta que la señal cambia al nivel lógico ALTO el instante de tiempo t1. En el instante de tiempo t2 la señal continúa presentando el nivel lógico ALTO, hasta que en el instante de tiempo t3, la señal cambia a nivel BAJO. Figura 3.8 Intervalos de tensión para los niveles lógicos para circuitos TTL y CMOS. El cambio de nivel BAJO a nivel ALTO se denomina flanco positivo o flanco de subida. El cambio de nivel ALTO a nivel BAJO se denomina flanco negativo o flanco de bajada. La secuencia de cambio BAJO-ALTO-BAJO con una duración en nivel ALTO relativamente corta, se denomina pulso positivo. La secuencia de cambio ALTO-BAJO-ALTO con una duración en nivel BAJO relativamente corta, se denomina pulso negativo. 57 Álgebra de Boole El conjunto de leyes y reglas de operación aplicables a las variables lógicas se denomina Álgebra de Boole en honor a George Boole, quien desarrolló el uso de herramientas matemáticas para la investigación lógica, mostrando con ello las bondades y el poder de las matemáticas aplicadas a la lógica y estableciendo un vínculo entre ambas ciencias. Definición Se denomina como Algebra de Boole a una estructura algebraica definida por: Un conjunto B de elementos. Un conjunto de operaciones lógicas cerradas definidas sobre B: 2 operaciones binarias Operación suma lógica Operación producto lógico 1 operación monoaria Operación complemento ó negación Operadores Los operadores del Algebra de Boole reciben los siguientes nombres y símbolos: Operador suma lógica: “+” (OR): La operación de suma lógica es una expresión algebraica que tiene dos o más operandos y el resultado de la operación es 1 lógico sólo si el valor de uno o más de los operandos es 1 lógico. Operador producto lógico: “.” (AND): La operación de producto lógico es una expresión algebraica que tiene dos o más operandos y el resultado de la operación es 1 lógico sólo si el valor de todos los operandos es 1 lógico. Operador complemento o negación: “¯ ” (NOT): La operación de complemento lógico es una operación que tiene un solo operando y el resultado de la operación es 1 lógico sólo si el valor del operando es 0 lógico y viceversa. Operación OR Operación AND Operación NOT 0+0=0 0+1=0 1+0=0 1+1=1 0. 0 = 1 0. 1 = 1 1. 0 = 1 1. 0 = 1 0=1 1=0 Tabla 3.3 Operaciones booleanas Postulados y Propiedades del Álgebra de Boole A modo de repaso y de referencia, la siguiente tabla resume los postulados y principales propiedades del Álgebra de Boole: 58 Operación OR Operación AND Propiedad conmutativa. Las operaciones son conmutativas a+b=b+a a ⋅b =b⋅a Propiedad distributiva. Las operaciones son distributivas entre sí a + (b ⋅ c ) = ( a + b ) ⋅ ( a + c ) a ⋅ (b + c ) = ( a ⋅ b ) + ( a ⋅ c ) Identidad. Las operaciones tienen elementos identidad diferentes dentro de B. Estos elementos son definidos como 0 para (+) y 1 para (·) a+0=a a ⋅1 = a Complemento. Para cada elemento, a del conjunto B, existe otro elemento ā denominado complemento, tal que se cumple: a + a =1 a⋅a =0 Elementos nulos. Para cualquier elemento a, se verifica: a +1=1 a⋅0=0 Asociatividad ( a + b ) + c = a + (b + c ) ( a ⋅ b ) ⋅ c = a ⋅ (b ⋅ c ) Idempotencia a+a=a a⋅a=a Involución (a ) = a Absorción a + ( a ⋅ b) = a a ⋅ ( a + b) = a Para cada par de elementos, se verifica: a + (a ⋅ b) = a + b a ⋅ (a + b) = a ⋅ b Leyes de De Morgan. Para cada par de elementos, a y b, se verifica: (a + b) = a ⋅ b (a ⋅ b) = a + b Leyes de De Morgan generalizadas. Para cualquier conjunto de elementos se verifica: ( x0 + x1 + ... + xn ) = x0 ⋅ x1 ⋅ ... ⋅ xn ( x 0 ⋅ x1 ⋅ ... ⋅ x n ) = x 0 + x1 + ... ⋅ + x n Tabla 3.4 Propiedades del Álgebra de Boole Expresiones booleanas La Figura 3.9 muestra el diagrama de una función lógica f de n variables. La función f (E1, E2,… , En) establece una relación entre las variables de entrada que genera como resultado la variable de salida S = f (E1, E2, … , En). Las entradas E1, E2, …, En son variables lógicas independientes y la salida S toma un valor lógico dependiendo de los valores de las variables de entrada. Para definir el valor de la salida S, la función lógica relaciona las variables de entrada E1, E2, …, En, por medio de los operadores booleanos: producto lógico, suma lógica y complemento, es decir, que toda función lógica puede ser representada por una expresión algebraica booleana. Figura 3.9 Función lógica de n entradas. 59 Ejemplo Determinar el valor de la función lógica representada por la siguiente expresión booleana: f (E1, E2, E3) = (E1 . E2) + (E3 . E1) Solución: Los valores de la salida S se obtienen evaluando la función lógica f (E1, E2, E3). La evaluación de la función lógica para encontrar el valor de la salida S consiste en reemplazar los valores de las variables de entrada en la expresión booleana de la función lógica. S = f (E1, E2, E3) = (E1 . E2) + (E3 . E1) Si E1 = 0, E2 = 1 y E3 = 1: S = f (E1,E2,E3) = (E1 . E2) + (E3 . E1) S = f (0,1,1) = (0 . 1) + (1 . 1) S = f (0,1,1) = (0) + (1) S = f (0,1,1) = 1 La función queda totalmente definida encontrando los valores que toma para cada una de las 2n combinaciones posibles que pueden presentar las n variables de entrada. Formas canónicas Dentro de las expresiones algebraicas booleanas, hay algunas que son de especial interés, las cuales se definen a continuación: Se denomina término producto al producto lógico de un número dado de variables o constantes. Se denomina término suma a la suma lógica de un número dado de variables o constantes. Se define expresión algebraica disyuntiva a la expresión de la función como suma de términos producto. Se dice que la función se encuentra expresada en forma normal disyuntiva o como suma de productos. Expresión algebraica disyuntiva: f ( A, B, C ) = A.B + A.B .C Se define como minterm al término producto en el que aparecen todas las variables de la función, una sola vez, ya sea en forma directa o complementada. Por lo tanto, un minterm es un caso especial de término producto. Por ejemplo, , , = ̅. . ̅ es un minterm. Se define expresión algebraica conjuntiva a la expresión de la función como producto de términos suma. Se dice que la función se encuentra expresada en forma normal conjuntiva o como producto de sumas. Por ejemplo: Expresión algebraica conjuntiva: f ( A, B.C ) = ( A + B + C ).( A + B) Se define como maxterm al término suma en el que aparecen todas las variables de la función, una sola vez, ya sea en forma directa o complementada. Por lo tanto, un maxterm es un caso especial de término suma. Por ejemplo, , , = ̅ + + ̅ es un maxterm. Expresión canónica disyuntiva A la expresión algebraica disyuntiva en la que todos los términos producto que aparecen son minterm, se le denomina expresión canónica disyuntiva. 60 Se verifican las siguientes propiedades: Dada la lista completa de minterm de n variables, asignando arbitrariamente valores 1 o 0 a cada variable, se verifica que un único minterm tomará el valor 1. n La fórmula compuesta por los 2 minterm tomará el valor 1. La fórmula canónica disyuntiva o de minterm es única. Para una función lógica, se cumple que f ( x1 , x2 ,..., xn ) = x1 ⋅ f (1, x2 ,..., xn ) + x1 ⋅ f (0, x2 ,..., xn ) Toda función puede expresarse como suma de minterms. Por ejemplo dada la fórmula disyuntiva , , = . + , se puede pasar a la fórmula canónica disyuntiva aplicando los postulados y propiedades del algebra de Boole. Ejemplo Dada la función , , = . + , encontrar su expresión canónica disyuntiva (suma de minterms). Solución: Comparando la forma del término A.B, con la definición de minterm, se observa que solamente falta la variable C. Para agregar este literal faltante sin modificar la igualdad, podemos utilizar las propiedades del álgebra de Boole. En este caso, como el elemento identidad del producto es la constante 1, podemos escribir: A.B = A.B .1. Pero como + ̅ = 1 por la propiedad del complemento, ̅ reemplazando queda: . = . . 1 = . . + . En forma similar, al segundo término de la función le faltan las variables A y B para formar un minterm, pero podemos multiplicar por + ̅ y + sin alterar la igualdad. Entonces: , , = . + , , = . . + ̅ + + ̅ . + . Aplicando distributiva, obtenemos: , , = . . + . . ̅ + . . + . . + ̅. . + ̅. . Como puede observarse, luego de aplicar propiedad distributiva, cada término de la expresión es un minterm, pero el primer término producto es igual al tercero. Así, luego de aplicar la propiedad de idempotencia, la expresión canónica disyuntiva de la función f será: , , = . . + . . ̅ + . . + ̅. . + ̅. . Expresión canónica conjuntiva A la expresión algebraica conjuntiva escrita mediante maxterm se le denomina fórmula canónica conjuntiva. Se verifican las siguientes propiedades Dada la lista completa de maxterms de n variables, asignando arbitrariamente 1 o 0 a cada variable, se verifica que un único maxterm tomará el valor 0. n La fórmula compuesta por los 2 maxterms tomará el valor 0. La fórmula canónica conjuntiva o de maxterm es única. Para una función lógica, se cumple que f ( x1 , x2 ,..., xn ) = [ x1 + f (0, x2 ,..., xn )] ⋅ [ x1 + f (1, x2 ,..., xn )] Toda función puede expresarse como producto de maxterms. Por ejemplo dada la fórmula disyuntiva , , = . + , se puede pasar a la fórmula canónica conjuntiva aplicando los postulados y propiedades del algebra de Boole. 61 Ejemplo , , Dada la función maxterms). = . + , encontrar su expresión canónica conjuntiva (producto de Solución: Analizando la expresión, vemos que se trata de una forma disyuntiva no canónica. En este ejemplo, conviene aplicar la propiedad distributiva para transformar la expresión a una forma conjuntiva. Así: , , = . + = + . = + . + Esta expresión se encuentra en forma conjuntiva, pero no es canónica. Para serlo, al término (C + A) le falta la variable B y al término (C + B) le falta la variable A. Para agregar los literales faltantes sin modificar la igualdad, podemos utilizar las propiedades del álgebra de Boole. En este caso, como el elemento identidad de la suma es la constante 0, podemos escribir: (C + A) = (C + A + 0). Pero como . = 0 por la propiedad del complemento, reemplazando y aplicando propiedad distributiva queda: + = + + = + + . + + . En forma similar, al término (C + B) le falta la variable A para formar un maxterm, pero podemos ̅ sin alterar la igualdad. sumarle El proceso completo sería: , , , , , , , , = . + = + . = + + = + + . + + = + + + + . ̅ + + + + ̅ Como puede observarse, luego de aplicar propiedad distributiva, cada término de la expresión es un maxterm, pero el primer término suma es igual al tercero. Por lo tanto, luego de reducir aplicando propiedad de idempotencia queda: , , = + + + + . + + ̅ Finalmente, luego de reordenar los literales en cada término suma, la expresión canónica conjuntiva de la función f será: , , = + + + + . ̅+ + Tablas de verdad Una tabla de verdad describe el valor de una función para cada una de las combinaciones posibles de valores lógicos de las variables. Cada fila de la tabla de verdad contiene la combinación de valores lógicos de las variables de la función y el correspondiente valor de la función para esa combinación. Es decir que la tabla de verdad muestra explícitamente todos los casos posibles de entrada y sus respectivos resultados (salida). Dada una función lógica de n variables, existen 2 combinaciones posibles de sus valores, de modo que la tabla de verdad de dicha función tiene 2 filas. En la Figura 3.10a se muestra la tabla de verdad de una función lógica de dos variables, designada como F1. La tabla de verdad muestra los valores que tomará la función F1 de acuerdo a la combinación de valores lógicos de las variables. Cada fila de la tabla muestra una de las combinaciones posibles y el valor de F1 para dicha combinación. La Figura 3.10 muestra también la tabla de verdad para una función de tres variables y la tabla de verdad para una función de cuatro variables. 62 B 0 0 1 1 A 0 1 0 1 F1 0 1 0 0 C 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 A 0 1 0 1 0 1 0 1 F2 1 1 0 1 1 1 0 1 D 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 (a) C 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 A 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 F3 0 1 1 0 0 1 1 1 1 0 0 0 1 0 1 0 (b) (c) Figura 3.10 Ejemplos de tablas de verdad. a) Función lógica de dos variables b) Función lógica de tres variables. c) Función lógica de cuatro variables Relación entre tablas de verdad y expresiones booleanas Las tablas de verdad y las expresiones booleanas son formas de representar una función lógica. Se puede encontrar la tabla de verdad de una función lógica a partir de la expresión booleana de dicha función lógica. Para ello se debe evaluar la expresión booleana para cada una de las combinaciones posibles de valores de entrada. En forma similar, dada la tabla de verdad de una función lógica, se puede encontrar la expresión booleana correspondiente. Ejemplo Dada la siguiente tabla de verdad de una función de tres variables, hallar la expresión booleana correspondiente Esta tabla de verdad expresa que la función F(A,B,C) toma el valor lógico 1 cuando: A = 0; B = 1 y C = 0 ó también cuando: A = 1; B = 0 y C = 0 A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 F(A,B,C) 0 0 1 0 1 0 0 0 Esto se interpreta de la siguiente manera: F = 1 cuando A = 0 y B = 1 y C = 0, es decir: F = A ⋅ B ⋅ C = 0 ⋅ 1 ⋅ 0 = 1 ⋅ 1 ⋅ 1 = 1 ó (+) cuando A = 1 y B = 0 y C = 0 es decir F = A ⋅ B ⋅ C = 1 ⋅ 0 ⋅ 0 = 1 ⋅ 1 ⋅ 1 = 1 Luego: F = A⋅ B ⋅C + A⋅ B ⋅C 63 Tabla de verdad, minterms y maxterms Figura 3.11 Lista completa de minterms y maxterms distintos que pueden formarse con tres variables: A, B y C. Por definición, un minterm es un término producto en el cual figuran todas las variables de la función una sola vez, ya sea en forma directa o complementada. La Figura 3.11 muestra la lista completa de los ocho minterms distintos que pueden formarse con tres variables. En general, dada una función de n variables, es posible formar 2 minterms distintos. Así, al considerar la lista completa de minterms distintos hay una relación directa con las filas de la tabla de verdad, la cual contiene las 2 combinaciones posibles de los valores de las variables de entrada, de manera tal que cada fila de la tabla identificará a un único minterm. Por otra parte, dada una combinación cualquiera de valores de las variables, al evaluar la lista completa de minterms distintos con esos valores, sólo uno de ellos será igual a 1. Por ejemplo, si analizamos la combinación de valores = 0, = 1y = 1, el único minterm cuyo resultado vale 1 es el minterm ̅ . Cualquier otro minterm dará como resultado cero para esa combinación de valores. Al analizar los maxterm, encontramos el comportamiento dual. Un maxterm es, por definición, un término suma en el cual aparecen todas las variables de la función una sola vez, en forma directa o complementada. Por esta razón, dada una función de n variables, es posible formar 2 maxterms distintos. La Figura 3.11 muestra los ocho maxterms distintos que pueden formarse con tres variables. Debido a que con n variables es posible formar 2 maxterms distintos y una función de n variables tiene 2 combinaciones posibles de los valores de las variables de entrada, podemos relacionar cada fila de la tabla de verdad con un único maxterm. Si tomamos una combinación cualquiera de valores de las variables, al evaluar la lista completa de maxterms distintos con esa combinación de valores, sólo uno de ellos tomará el valor 0. Por ejemplo, al evaluar los maxterms con la combinación de valores = 0, = 1y = 1, el único de ellos cuyo resultado vale 0 es el maxterm + + ̅ . Cualquier otro maxterm dará como resultado uno para esa combinación de valores. La asociación de un minterm con una fila de la tabla se obtiene al igualar a uno la expresión del minterm y deduciendo los valores de las variables que cumplen la igualdad. Por ejemplo, analicemos el minterm ̅ . La expresión del minterm igualada a uno es: ̅ =1 La igualdad sólo se cumple cuando = 0, = 1 = 1, ya que en ese caso ̅ = 0.1. 1 = 1 La combinación de valores = 0, = 1 = 1 corresponde a la cuarta fila de la tabla. Análogamente, igualando a cero la expresión del maxterm, puede deducirse el valor que debe tomar cada variable para cumplir la igualdad y ubicar esa combinación entre las fila de la tabla. Por ejemplo, al analizar el maxterm + + ̅ , tenemos que: La expresión del maxterm igualada a cero es:: + + ̅ = 0 La igualdad sólo se cumple cuando = 0, = 1 = 1, ya que en ese caso + + ̅ = 0 + 1 + 1 = 0 La combinación de valores = 0, = 1 = 1 corresponde a la cuarta fila de la tabla. La Figura 3.12 muestra las combinaciones de valores de tres variables y los minterms y maxterms relacionados a cada combinación de valores. 64 Figura 3.12 Expresión y notación de minterms y maxterms para una tabla de verdad de tres variables Observe que la Figura 3.12 muestra la notación de los minterms como mi y los maxterms como Mi , donde i es un subíndice cuyo valor se corresponde con el número binario formado con los valores lógicos de las variables. Debe tenerse en cuenta que la tabla muestra combinaciones de valores lógicos 0 y 1 de las variables, pero los símbolos 0 y 1 también se utilizan en el sistema de numeración de base dos. Esta coincidencia permite asociar una combinación de valores lógicos con un número binario. Tabla de verdad y expresiones equivalentes Una función es unívocamente representada por su tabla de verdad. Se dice que dos o más expresiones algebraicas son equivalentes (F1 = F2) si ambas tienen la misma tabla de verdad, es decir, describen la misma función lógica. Por ejemplo, evaluando las expresiones de las siguientes funciones F1, F2 y F3 encontrará que poseen la misma tabla de verdad. A 0 0 1 1 B 0 1 0 1 F1 ( A, B ) = AB + A( B + A ) F(A,B) 0 1 1 0 F2 ( A, B) = A B + AB F3 ( A, B ) = ( A + B )( A + B ) Como se puede observar, es posible que existan muchas expresiones algebraicas que describan a la misma función lógica. Esta equivalencia se evidencia en la tabla de verdad. Relación entre la tabla de verdad y las expresiones canónicas De las expresiones equivalentes de una función, existen dos de ellas que pueden obtenerse en forma directa de la tabla de verdad: la expresión canónica disyuntiva y la expresión canónica conjuntiva. A primera vista, las expresiones canónicas pueden parecer expresiones más complejas, ya que estas expresiones se caracterizan porque en cada uno de los términos aparecen todas las variables de la función. Sin embargo, esta complejidad es solo aparente y por el contrario, presentan la ventaja de ser obtenibles a partir de la tabla de verdad de una manera muy sencilla, como veremos a continuación. 65 La expresión canónica disyuntiva se encuentra en forma de suma de productos. Como cada término es un minterm, también se denomina suma de minterms o expansión en minterms. Esto permite utilizar una notación compacta para representar la función, en base a la notación mi de los minterms que la componen. Ejemplo A 0 0 0 0 1 1 1 1 Dada la siguiente tabla de verdad de una función de tres variables, hallar la forma canónica disyuntiva. Para encontrar la forma canónica disyuntiva, se toman las filas de la tabla de verdad donde la función vale 1. Como cada fila referencia un minterm, la forma canónica se construye sumando los minterms encontrados. La tabla de verdad muestra que la función F(A,B,C) toma el valor lógico 1 cuando: = 0, = 0 = 1 → minterm ̅ = 0, = 1 = 0 → minterm ̅ = 1, = 0 = 0 → minterm = 1, = 1 = 1 → minterm B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 F(A,B,C) 0 1 1 0 1 0 0 1 ̅ ̅ Luego: " , , = ̅ + ̅ ̅+ ̅+ En notación compacta: " , , = #$ + #% + #& + #' Análogamente, la expresión canónica conjuntiva se encuentra en forma de producto de sumas. Cada término es un maxterm y por tal razón también se conoce como producto de maxterms o expansión en maxterms. Referenciando cada maxterm de la función con la notación Mi puede representarse la expresión de la función mediante una notación compacta. Ejemplo A 0 0 0 0 1 1 1 1 Dada la siguiente tabla de verdad de una función de tres variables, hallar la forma canónica conjuntiva. La forma canónica conjuntiva, se construye tomando las filas de la tabla de verdad donde la función vale 0. Como cada fila referencia un maxterm, se construye la expresión realizando el producto de los maxterms encontrados. La tabla de verdad muestra que la función F(A,B,C) toma el valor lógico 0 cuando: = 0, = 0 = 0 → maxterm + + = 0, = 1 = 1 → maxterm + + ̅ = 1, = 0 = 1 → maxterm ̅+ + = 1, = 1 = 0 → maxterm ̅+ + + + + + ̅ Luego: " , , = En notación compacta: " , , = *+ + *, + *- + *. 66 ̅+ + B 0 0 1 1 0 0 1 1 ̅+ C 0 1 0 1 0 1 0 1 + F(A,B,C) 0 1 1 0 1 0 0 1 Funciones incompletas o incompletamente especificadas Hasta ahora hemos tratado con funciones que se encuentran definidas para todas las combinaciones posibles de los valores de las variables, pero puede ocurrir que una función lógica no se encuentre definida para todas las combinaciones. Esto suele pasar cuando las variables de la función no son independientes entre sí o cuando no puedan producirse todas las combinaciones. A este tipo de funciones se les denomina funciones incompletas o incompletamente especificadas. En la tabla de verdad, el valor de la función para aquellas combinaciones de entrada que no tienen un valor de salida definido se indica con “-” o con “x”. Ejemplo Sea la función incompleta expresada por la siguiente tabla de verdad: A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 F(A,B,C) 0 1 1 0 1 - Las combinaciones de valores de entrada para las cuales la función no está especificada son: A = 0, B = 1, C = 1 A = 1, B = 1, C = 0 A = 1, B = 1, C = 1 Se puede asignar cualquier valor lógico a la función cuando de acuerdo al problema esas combinaciones de entrada no se presentarán o el valor de la función en esos casos no será tenido en cuenta. Algebraicamente, las funciones incompletamente especificadas pueden ser expresadas mediante la unión de dos funciones diferentes: Una función completa f, que contempla únicamente los 0 ó 1 de las combinaciones para las cuales la función está definida. En el caso anterior sería f = m1 + m2 + m5 = M3·M7. Y otra función, denominada función inespecificación Φ, que contempla todas las combinaciones para las cuales la función no está definida. En el caso anterior sería Φ= m3 + m6 + m7 = M0·M1·M4. Es decir F = f + Φ Al momento de crear la implementación de dicha función, hay que tener en cuenta que: La función f debe ser completamente implementada. La función Φ no tiene porqué ser completamente implementada. Ésta puede que no sea implementada, que sea implementada sólo parcialmente o que esté completamente implementada. En el caso de funciones incompletamente especificadas, se cumple que la fórmula de minterm o de maxterm no es única, ya que pueden existir tantas expresiones como combinaciones de sus inespecificaciones. Veremos más adelante cómo se pueden emplear las inespecificaciones para minimizar la expresión lógica de la función. 67 Compuertas lógicas Como vimos en la unidad anterior, los transistores son componentes electrónicos que pueden ser utilizados como elementos de conmutación para operar en uno de dos estados posibles: en corte o en saturación. Esta característica de funcionamiento de los transistores se utiliza para formar circuitos electrónicos que realizan operaciones lógicas simples, denominadas compuertas lógicas o simplemente compuertas. De esta manera, las compuertas sirven como bloques fundamentales de cualquier dispositivo lógico, de manera tal que los circuitos lógicos son un conjunto de compuertas lógicas interconectadas para realizar alguna tarea específica. Los circuitos electrónicos que implementan las compuertas lógicas pueden construirse mediante diodos, transistores y resistencias conectados de tal forma que la salida del circuito es el resultado de la operación lógica aplicada a las entradas. En estos circuitos, las entradas y salidas son señales eléctricas de tensión cuyo valor representa uno de los valores lógicos. Compuertas lógicas básicas Figura 3.13 Símbolos tradicionales de las compuertas lógicas básicas. Una compuerta lógica básica es aquella que implementa una operación booleana básica. Se designan con los mismos nombres de la operación que implementan y se identifican mediante símbolos especiales. En la Figura 3.13 se muestran los símbolos tradicionales utilizados para representar las compuertas básicas. En el diseño de circuitos digitales estas compuertas básicas se combinan para formar los circuitos lógicos que implementan las funciones lógicas más complejas. La compuerta OR La compuerta OR es un circuito que tiene dos o más entradas y cuya salida es igual a la suma lógica de las entradas. La Figura 3.14 muestra el símbolo lógico, la tabla de verdad y la expresión booleana para una compuerta OR de dos entradas. A 0 0 1 1 (a) B 0 1 0 1 S=A+B 0 1 1 1 (c) (b) Figura 3.14 a) Símbolo lógico y expresión booleana para la compuerta OR de dos entradas. b) Tabla de verdad de la operación OR. c) Ejemplo de diagrama temporal de la compuerta OR. Tanto las entradas como la salida de la compuerta son niveles lógicos de voltaje. La compuerta OR opera de tal forma que su salida es ALTO (valor lógico 1) si cualquiera de sus entradas están en ALTO. La salida será BAJO (valor lógico 0) sólo si todas las entradas están en BAJO. Esta característica se muestra en la tabla de verdad y en el diagrama temporal de ejemplo mostrado en la Figura 3.14c. 68 La expresión booleana S = A + B indica que la salida S es la combinación OR (suma lógica) de sus entradas. Este principio general se puede ampliar a más de dos entradas, como se muestra en la Figura 3.15. De nuevo, la tabla de verdad muestra que la salida será 1 siempre que una o más entradas sean 1 y que la salida será 0 sólo cuando todas las entradas sean 0. Figura 3.15 Compuerta OR de tres entradas A B C 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 S=A+B+ C 0 1 1 1 1 1 1 1 La compuerta AND La compuerta AND es un circuito con dos o más entradas que opera de tal forma que la salida es igual al producto lógico de las entradas. En la Figura 3.16 se muestra el símbolo lógico, la tabla de verdad y la expresión booleana para una compuerta AND de dos entradas. A 0 0 1 1 (a) B 0 1 0 1 S = A.B 0 0 0 1 (c) (b) Figura 3.16 a) Símbolo lógico y expresión booleana para la compuerta AND de dos entradas. b) Tabla de verdad de la operación AND. c) Ejemplo de diagrama temporal.de la compuerta AND. Tal como muestra la tabla de verdad de la Figura 3.16, la salida de la compuerta AND es 1 sólo cuando todas sus entradas son 1 y la salida será 0 cuando una o más entradas sean 0. La expresión booleana S = A.B indica que la salida S se obtiene realizando la operación AND (producto lógico) entre las entradas. Esta característica puede extenderse a más de dos entradas, como se muestra en la Figura 3.17, en la cual se corrobora que la salida será 0 cuando una o más entradas sean 0 y que la salida será 1 sólo cuando todas las entradas sean 1. 69 A 0 0 0 0 1 1 1 1 Figura 3.17 Compuerta AND de tres entradas B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 S = A.B.C 0 0 0 0 0 0 0 1 La compuerta NOT La compuerta NOT es un circuito que tiene una sola entrada y cuya salida se obtiene realizando la operación NOT al valor de entrada. En la Figura 3.18 se muestra el símbolo lógico, la tabla de verdad y la expresión booleana para una compuerta NOT. A 0 1 (a) S=Ā 1 0 (b) (c) Figura 3.18 a) Símbolo lógico y expresión booleana para la compuerta NOT o INVERSOR. b) Tabla de verdad de la operación NOT. c) Ejemplo de diagrama temporal de la compuerta NOT o INVERSOR. Tal como muestra la tabla de verdad de la Figura 3.18, la salida de la compuerta NOT es siempre el opuesto de la entrada, es decir, cuando la entrada es 0 la salida es 1 y viceversa. Por ello, es muy común el uso del término INVERSOR para referirse a esta compuerta. La expresión booleana / = ̅ indica que la salida se obtiene realizando la operación NOT (complemento) sobre la entrada. Esta operación se realiza siempre sobre una sola entrada, como se muestra en la Figura 3.18. Funciones lógicas y circuitos lógicos Figura 3.19 Función lógica y su implementación con un circuito digital o circuito lógico. En la Figura 3.19a el diagrama representa una función lógica de n entradas y en la Figura 3.19b se muestra un circuito digital de n entradas y salida única. El valor de la salida S del circuito digital queda determinado mediante la aplicación de un conjunto de reglas lógicas sobre las entradas. Estas reglas definen el comportamiento o lógica del circuito y determina la forma en que un circuito digital responde a las entradas. 70 El conjunto de reglas que relaciona las entradas con la salida se representa mediante una función lógica, cuyas variables representan las señales de entrada del circuito digital. La función lógica se describe mediante una expresión algebraica, en la cual los operadores del álgebra booleana relacionan las variables intervinientes. Así, la función lógica representa la relación entrada-salida del circuito digital. En el otro sentido, también puede decirse que el circuito digital es la implementación física del conjunto de reglas descrito por la función lógica. Implementación de funciones lógicas mediante circuitos lógicos con compuertas básicas Una función lógica se representa mediante expresiones booleanas y las compuertas lógicas básicas implementan las operaciones booleanas. Puede observarse entonces que existe una correspondencia directa entre la expresión booleana de una función lógica y los circuitos lógicos a nivel de compuertas básicas, como se muestra en el siguiente ejemplo. Ejemplo Implementar la siguiente función lógica mediante compuertas básicas: , , = + . Solución: Para implementar la función lógica, se deben identificar las operaciones booleanas de la expresión algebraica y relacionarlas con la compuerta básica correspondiente. La expresión de la función muestra el orden de precedencia con que deben realizarse las operaciones. En este caso, primero debe realizarse la suma lógica de + . Esta suma lógica se implementa con una compuerta OR cuyas entradas son A y B. La operación de complemento se realiza con un INVERSOR, cuya entrada será la salida de la compuerta OR, esto es + para luego obtener su complemento + . Finalmente el producto lógico se implementa con una compuerta AND que tiene, en una de sus entradas la salida del INVERSOR y en la otra, la variable construyendo así la expresión completa de f Figura 3.20 Implementación de una función lógica mediante compuertas básicas. Como las compuertas básicas implementan las operaciones definidas en el algebra de Boole, el conjunto de compuertas AND, OR y NOT es funcionalmente completo y permite implementar cualquier función lógica. Es decir que, a partir de estas compuertas elementales pueden construirse circuitos lógicos, tales como contadores, comparadores, sumadores y combinaciones más complejas. 71 Representación de circuitos lógicos mediante funciones lógicas Los circuitos lógicos se construyen mediante la interconexión de compuertas lógicas, cada una de las cuales implementa una operación booleana. Por esta razón, dado un circuito lógico a nivel de compuertas, siempre se pueden obtener las expresiones booleanas individuales de las compuertas y formar la función lógica correspondiente. Ejemplo El circuito lógico de la Figura 3.21 recibe en sus terminales de entrada las señales A, B y C. En el terminal de salida S se encuentra conectado un diodo led que se enciende cuando la salida S del circuito se pone en valor ALTO y permanece apagado siempre que la salida S esté en BAJO. Encuentre la función lógica correspondiente. Figura 3.21 Circuito lógico de tres entradas cuya salida S en valor ALTO enciende el diodo led. Solución: Siguiendo el circuito desde las entradas hacia la salida, se pueden ir obteniendo las expresiones booleanas de las compuertas que intervienen: La compuerta AND1 tiene conectada a una de sus entradas la señal de salida de INV1, o sea ̅, mientras que la otra entrada de AND1 es , por lo cual la salida de la compuerta AND 1 es ̅. . Una de las entradas de AND4 es la salida de AND1 y la otra entrada es , por lo tanto la salida de la compuerta AND4 es ̅. . . La compuerta AND2, tiene como una de sus entradas la señal . La otra entrada de AND2 es la salida de la compuerta inversora INV2, o sea, . Por lo tanto, la salida de AND2 es . . Una de las entradas de AND5 es la salida de AND2, mientras que la otra entrada es , por lo tanto la salida de la compuerta AND5 es . . Las entradas de AND3 son y , por lo tanto su salida es el producto lógico . . 72 Ejemplo (continuación) Una de las entradas de AND6 es la salida de AND3. La otra entrada de AND6 es la salida de INV3, o sea, ̅ . Por lo tanto, la salida de la compuerta AND6 es . . ̅ . La compuerta OR1 realiza la suma lógica de las salidas de AND4 y AND5, obteniendo ̅. . + . . Una de las entradas de OR2 es la salida de OR1. Como la otra entrada de OR2 es la salida de AND6, la salida de la compuerta OR2, es decir ̅. . + . . + . . ̅ Otra forma de obtener la función lógica es ir escribiendo sobre el diagrama del circuito las expresiones booleanas de las compuertas, completando las expresiones para cada compuerta, desde las entradas hacia a salida, como se muestra a continuación: El circuito lógico de la Figura 3.22 recibe en sus terminales de entrada las señales A, B y C. En el terminal de salida S se encuentra conectado un diodo led que se enciende cuando la salida S del circuito se pone en valor ALTO y permanece apagado siempre que la salida S esté en BAJO. Para encontrar la función lógica correspondiente se pueden ir escribiendo las expresiones booleanas a la salida de cada compuerta, comenzando desde las entradas y siguiendo progresivamente hacia la salida, como se muestra en la siguiente figura: Figura 3.22 Formación de la expresión booleana de la salida S. Otras compuertas Además de las compuertas básicas, que implementan electrónicamente el comportamiento de los operadores del algebra de Boole, existen compuertas que implementan funciones simples y útiles en la implementación de circuitos lógicos, tales como la suma lógica negada y el producto lógico negado. 73 La compuerta NOR La compuerta NOR es un circuito que tiene dos o más entradas y su salida es igual al complemento de la suma lógica de las entradas es decir, opera en forma equivalente a una compuerta OR seguida de un INVERSOR, como se muestra en la Figura 3.23: Figura 3.23 Circuito equivalente de la compuerta NOR El símbolo de la compuerta NOR es similar al de la compuerta OR. De hecho, la única diferencia es el círculo pequeño en la salida de la compuerta NOR. Este círculo pequeño denota la operación de complemento que el INVERSOR realiza a la salida de la compuerta OR en el circuito equivalente. Esta diferencia también se puede apreciar al comparar las expresiones booleanas de las compuertas OR y NOR. A continuación se muestra el símbolo lógico, la tabla de verdad y la expresión booleana para una compuerta NOR de dos entradas. Figura 3.24 Compuerta NOR a) Tabla de verdad de la operación NOR. c) Símbolo lógico y expresión booleana para la compuerta NOR de dos entradas. A 0 0 1 1 B 0 1 0 1 x=A+B 1 0 0 0 (b) (a) La compuerta NOR opera de tal forma que su salida es el opuesto de la salida de la compuerta OR al considerar las mismas condiciones de entrada. Es decir, la salida de la compuerta NOR es BAJO si cualquiera de sus entradas está en ALTO. La salida será ALTO sólo si todas las entradas están en BAJO. Esta característica se muestra en la tabla de verdad de la Figura 3.24. La expresión booleana x = A + B indica que la salida de la compuerta NOR es el complemento de la combinación OR de sus entradas. Este principio general se puede ampliar a más de dos entradas. La compuerta NAND La compuerta NAND es un circuito que tiene dos o más entradas y su salida es igual al complemento del producto lógico de las entradas es decir, opera en forma equivalente a una compuerta AND seguida de un INVERSOR, como se muestra en la Figura 3.25: 74 Figura 3.25 Circuito equivalente de la compuerta NAND El símbolo de la compuerta NAND es similar al de la compuerta AND, excepto por el círculo pequeño que posee la compuerta NAND en la salida. Este círculo pequeño denota la operación de complemento que el INVERSOR realiza a la salida de la compuerta AND en el circuito equivalente. Esta diferencia también surge al comparar las expresiones booleanas de las compuertas AND y NAND. A continuación se muestra el símbolo lógico, la tabla de verdad y la expresión booleana para una compuerta NAND de dos entradas. Figura 3.26 Compuerta NAND a) Tabla de verdad de la operación NAND. c) Símbolo lógico y expresión booleana para la compuerta NAND de dos entradas. A 0 0 1 1 B 0 1 0 1 x = A.B 1 1 1 0 (b) (a) La tabla de verdad de la Figura 3.26 muestra que la compuerta NAND opera de tal forma que su salida es el opuesto de la salida de la compuerta AND al considerar las mismas condiciones de entrada. Es decir, la salida de la compuerta NAND es ALTO si cualquiera de sus entradas está en ALTO. La salida será BAJA sólo si todas las entradas están en ALTO. La expresión booleana x = A ⋅ B indica que la salida de la compuerta NAND es el complemento de la combinación AND de sus entradas. Este principio general se puede ampliar a más de dos entradas. Universalidad de las compuertas NOR y NAND Las expresiones booleanas representan funciones lógicas combinando variables y constantes booleanas mediante las operaciones básicas OR, AND y NOT. Por esta razón, cualquier función lógica puede a su vez ser implementada en un circuito lógico que utiliza combinaciones de compuertas OR, AND e INVERSORES que llevan a cabo las operaciones booleanas básicas. La compuerta NAND se puede utilizar para lograr el comportamiento de cualquiera de las demás compuertas básicas, por esta razón la compuerta NAND es una compuerta universal y mediante su uso se puede implementar cualquier función lógica. Esta característica hace que en el mercado de circuitos integrados exista una disponibilidad mayor de compuertas NAND que los otros tipos de compuertas. La compuerta NOR es también una compuerta universal porque se puede utilizar para lograr el comportamiento de cualquiera de las compuertas básicas. Es decir, cualquier función lógica se puede implementar basándose únicamente en compuertas NOR. 75 Implementación de funciones lógicas mediante compuertas NAND La Figura 3.27 muestra la forma en que las compuertas NAND se pueden utilizar para sustituir las compuertas básicas. Del análisis de las expresiones booleanas surge la validez de los circuitos equivalentes. Figura 3.27 Implementación de compuertas básicas mediante compuertas NAND. La implementación de circuitos lógicos mediante compuertas NAND se puede realizar en base a la implementación de operaciones básicas mediante compuertas NAND. En la práctica, esta implementación no se realiza por sustitución directa, sino que se manipula la expresión booleana de la función lógica para obtener una función equivalente que presente la forma de productos negados, que suele denominarse lógica NAND. Ejemplo Implementar la función lógica / = ̅. . + . . + . . ̅ mediante compuertas NAND. Solución: La función se encuentra en forma disyuntiva (suma de términos producto). A partir de esta forma, el método consiste en aplicar doble negación a la expresión completa y luego aplicar el teorema de De Morgan, como se muestra a continuación: / = ̅. . + . . + . . ̅ Aplicando doble negación: ̅. . + . . + . . ̅ /̿ = 11111111111111111111111111111111 (no se modifica la expresión, pues /̿ = /) Aplicando el teorema de De Morgan a la negación inferior: / = ̅. . . . . . . . ̅ Analizando esta expresión equivalente se observa que se encuentra en la forma de productos negados. La implementación de la función lógica consiste en utilizar una compuerta NAND por cada variable negada y por cada producto negado presente en la expresión equivalente, como se muestra a continuación: 76 Ejemplo (continuación) Figura 3.28 Implementación de la función lógica mediante compuertas NAND. Implementación de funciones lógicas mediante compuertas NOR En la Figura 3.29 se muestra la forma en que las compuertas NOR se pueden utilizar para sustituir las compuertas básicas. Del análisis de las expresiones booleanas surge la validez de los circuitos equivalentes 77 Figura 3.29 Implementación de compuertas básicas mediante compuertas NOR. Implementar circuitos lógicos mediante compuertas NOR consiste en realizar las operaciones básicas mediante compuertas NOR. En la práctica, se busca expresar la función lógica mediante una función equivalente que presente la forma de sumas negadas, que suele denominarse lógica NOR. Ejemplo Implementar la función lógica / = ̅. . + . . + . . ̅ mediante compuertas NOR. Solución: La función se encuentra en forma disyuntiva (suma de términos producto). A partir de esta forma, el método consiste en aplicar doble negación a la expresión completa y luego aplicar el teorema de De Morgan, como se muestra a continuación: /= . . + . . + . . Aplicando doble negación: /̿ = 11111111111111111111111111111111 . . + . . + . . (no se modifica la expresión, pues /̿ = /) Aplicando el teorema de De Morgan a la negación inferior: / = ̅. . . . . . . . ̅ Aplicando el teorema de De Morgan a los términos producto negados: / = + + ̅ . ̅ + + ̅ . ̅ + + Aplicando el teorema de De Morgan nuevamente: / = + + ̅ + ̅ + + ̅ + ̅ + + Analizando esta expresión equivalente, se observa que los términos producto se han transformado en sumas negadas por aplicación del teorema de De Morgan. Sin embargo, la suma entre estas sumas negadas no se encuentra negada, como requiere la forma NOR. Por esta razón se debe volver a aplicar doble negación a la expresión completa: /̅ = + + ̅ + ̅ + + ̅ + ̅ + + 78 Ejemplo (continuación) La implementación de la función lógica consiste en utilizar una compuerta NOR por cada variable negada y por cada suma negada presente en la expresión equivalente, como se muestra a continuación: Figura 3.30 Implementación de la función lógica mediante compuertas NOR. Simplificación de funciones lógicas Cualquiera sea la implementación que se realice de una función lógica, su costo estará en relación directa a su complejidad. Como hemos visto, las funciones lógicas pueden presentar expresiones equivalentes, cada una de ellas con mayor o menor número de términos. Por esta razón, a fin de alcanzar un diseño óptimo, suele ser recomendable simplificar o reducir las funciones previamente a su implementación. La minimización de términos de una expresión booleana, consiste en hallar una expresión booleana equivalente que sea más sencilla, es decir, que tenga, si es posible, menos términos que la expresión original y que cada término tenga la menor cantidad de variables. Esto se consigue mediante la detección y absorción de términos de alguna de las siguientes formas: A + A = 1; A + 1 = 1; 79 A⋅ A = 0 ; A⋅0 = 0 Ejemplo Sea simplificar la expresión de la función F ( A, B, C ) = A ⋅ C + B ⋅ C + A ⋅ C + A ⋅ B Para implementar la función original se requieren 4 compuertas AND de 2 entradas, una OR de 4 entradas y dos inversores. Figura 3.31 Implementación de la función lógica sin reducir. F ( A, B, C ) = A ⋅ C + B ⋅ C + A ⋅ C + A ⋅ B Sacando factor común C en los términos 1º y 3º (propiedad distributiva): F ( A, B, C ) = ( A + A) ⋅ C + B ⋅ C + A ⋅ B = 1 ⋅ C + B ⋅ C + A ⋅ B = C + B ⋅ C + A ⋅ B Haciendo lo mismo ahora con los 2 primeros términos: F ( A, B, C ) = C ⋅ (1 + B ) + A ⋅ B = C ⋅ 1 + A ⋅ B = C + A ⋅ B La implementación de la función una vez reducida, requiere sólo 1 compuerta AND de 2 entradas, una OR de dos entradas y 2 inversores. Figura 3.32 Implementación de la función lógica simplificada. Con la simplificación se busca lograr: 1. Menor número de variables. 2. Menor número de términos (ya que, por lo general, un término suele corresponderse con una compuerta lógica). 3. Menor valor asociado. Este valor sigue la siguiente fórmula: nº variables + nº términos – nº términos con un solo literal –1 El primer criterio (el número de variables) nos va a dar idea del número de entradas que debe tener cada compuerta lógica del primer nivel. Es decir, en el caso de suma de productos, nos indicará el número de entradas de cada 80 compuerta AND. En el caso de producto de sumas, nos indicará el número de entradas de cada compuerta OR. El segundo criterio nos va a dar idea del número aproximado de compuertas del primer nivel. Por último, el tercer criterio nos va a dar idea del número de términos que no serán implementados con compuertas (cada término con un solo literal será implementado con un solo cable). Métodos para la simplificación de funciones lógicas La simplificación no resulta, en general, tan evidente como en el ejemplo anterior. Se recurre entonces a métodos de simplificación de funciones lógicas. Los más usados son: Simplificación algebraica. Consiste en la aplicación de los teoremas y propiedades del algebra de Boole. Es un método por inspección y por ello se convierte en un proceso de prueba y error, ya que no siempre es obvio determinar cuál de los teoremas es conveniente aplicar para obtener el resultado más simple. Tiene como desventaja que la aplicación del método no garantiza por sí misma que la expresión equivalente obtenida sea la más simple. Mapas de Karnaugh. Es un método gráfico que permite obtener la expresión equivalente más simple de una expresión algebraica booleana. Su uso práctico se limita a funciones de hasta seis variables. Métodos tabulares. Es un método que aplica los mismos principios que el de mapas de Karnaugh, pero su forma tabular permite aplicar algoritmos numéricos y su implementación mediante programas informáticos. Su ventaja es la de permitir trabajar con funciones de más de 6 variables. Nos limitaremos al uso de mapas de Karnaugh como método de simplificación Mapas de Karnaugh El método de simplificación de mapas de Karnaugh es un método que consiste en representar gráficamente las adyacencias lógicas que hacen posible la detección de términos a absorber. Se dice que dos términos tienen adyacencia lógica o son lógicamente adyacentes cuando difieren en una sola variable, de manera tal que esa variable aparece en forma directa en uno de los términos y en forma complementada en el otro término. Cuando dos términos presentan esta característica, es posible realizar una simplificación entre ambos, como se muestra en la Figura 3.33 La Figura 3.33 muestra el concepto de adyacencia lógica utilizando una función de ejemplo F expresada en forma canónica disyuntiva y el proceso de simplificación algebraica que permite reducir los términos adyacentes. ̅+ " , , = ̅ ̅+ 1º y 2º término: ̅ ̅ y ̅ y ̅ 2º y 3º término: 1º y 3º término: ̅ ̅ y ̅ ̅ ̅ nosonadyacentesporquedi9ierenenlasvariablesAyB nosonadyacentesporquedi9ierenenlasvariablesA, ByC sonadyacentesporquesólodi9ierenenlavariableC 81 Simplificación: Reordenando términos: " , , = ̅ ̅+ ̅ " , , = ̅ ̅+ " , , = ̅ + ̅ + ̅ + ̅ Figura 3.33 Simplificación de términos adyacentes. El mapa de Karnaugh consiste en utilizar celdas o casillas dispuestas gráficamente de manera tal que entre celdas vecinas, en forma horizontal o vertical, exista adyacencia lógica. Esto significa que entre una celda y otra sólo cambia una variable y agrupando celdas adyacentes obtenemos términos adyacentes que pueden reducirse a una expresión con una variable menos, como se muestra en la Figura 3.33. B B A BA B 0 C 1 B 00 A 0 C 0 A 1 C 1 B 01 A a) 2 variables AB DC 00 BA B B D 11 DC 10 00 01 B A 11 10 A C C C B D 00 BA A A A DC D 01 11 10 00 A 01 B A 11 10 A C C B C D 00 BA Mapa para E = 0 c) 4 variables ABCD 10 b) 3 variables ABC D 01 11 D 01 11 10 00 A 01 A 11 10 A C C C Mapa para E = 1 d) 5 variables ABCDE Figura 3.34 Mapas de Karnaugh según el número de variables. Dada una función lógica, la representación gráfica del mapa correspondiente asocia las celdas del mapa con las filas de la tabla de verdad de la función lógica. El mapa presenta las siguientes características: Existen tantas celdas como filas tiene la tabla de verdad de la función a representar. O sea, para funciones de n variables resultan mapas de 2n celdas. Cada celda del mapa se corresponde con una fila de la tabla y contiene el valor de la función para esa combinación de valores de las variables (generalmente suelen colocarse los 1’s y obviarse los 0’s). Los términos que difieren sólo en una variable (adyacencia lógica) resultan físicamente adyacentes en la tabla. Esta relación de adyacencia física, se entiende horizontal y/o verticalmente (no diagonal). En las representaciones de 5 y 6 variables, las vecindades se determinan superponiendo mapas para 4 variables. No se utilizan, en general, para más de 6 variables. 82 De acuerdo a estas consideraciones, resultarán mapas de 4 celdas si se opera con 2 variables; de 8 celdas para 3 variables y de 16 celdas para 4 variables. Para representar funciones de 5 variables se trazan 2 mapas de 4 variables que se consideran superpuestos. La disposición de las celdas del mapa se realiza de forma tal que las celdas contiguas representen minterms que difieran solamente en una variable. Esto se representa mediante encabezados de filas y de columnas en el mapa, como se muestra en la Figura 3.34. Llenado de un mapa El llenado del mapa consiste en transcribir en las celdas correspondientes los unos, las inespecificaciones y si fuese necesario los ceros, de la tabla de verdad de la función a minimizar. La correspondencia de cada una de las filas de la tabla con las celdas del mapa se produce de acuerdo a la ubicación de las variables de referencia del mapa. Figura 3.35 Ejemplo de llenado de un mapa. Encirculamientos Este paso consiste en agrupar términos que tienen adyacencia lógica. Para ello, se observan en el mapa los 1's y sus eventuales vecindades para detectar grupos formados por 2,4 u 8 celdas vecinas. Los unos que tengan un solo adyacente, se encircularán juntos y esto indica que absorben 1 variable. Los grupos de 4 unos vecinos absorben 2 variables; los grupos de 8 unos vecinos absorben 3 variables; etc. El método consiste en realizar los encirculamientos más grandes posibles El proceso concluye cuando se han encirculado todos los unos. El hecho de que un "1" haya sido incluido en más de un encirculamiento, significa que ese minterm fue utilizado más de una vez para hacer reducciones, lo cual es correcto (equivale a haber usado la propiedad de que A + A + ... + A = A). Puede ocurrir que el mapa presente unos aislados (sin vecinos).Esto significa que ese término no se puede asociar con otro para realizar alguna absorción. 83 (a) (b) (c) Figura 3.36 a) y b) Encirculamientos del mapa c) Resultado de los encirculamientos realizados. Aunque lo más habitual sea realizar los encirculamientos de los unos del mapa de Karnaugh, también es posible volcar en el mapa los ceros de la tabla y hacer los encirculamientos entre ellos. En este caso, se debe tener en cuenta que al leer los encirculamientos de los ceros se estará obteniendo " . Lectura de un mapa El último paso consiste en leer todos los encirculamientos en términos de las variables lógicas, obteniendo así la expresión de la función lógica en su forma simplificada. La lectura de los encirculamientos realiza el proceso de absorción de variables en forma gráfica. Para aclarar esto, considere como ejemplo el primer encirculamiento de cuatro unos mostrado en la Figura 3.36. El equivalente analítico de leer dicho encirculamiento es el siguiente: Sacando factor común y Como + = 1; resulta: Sacado factor común : Como ̅ + = 1,resulta: : @ABCDBEFG#CHAIJK @ABCDBEFG#CHAIJK @ABCDBEFG#CHAIJK @ABCDBEFG#CHAIJK @ABCDBEFG#CHAIJK = ̅ + ̅ + ̅ = + + = ̅ + ̅+ = = + + Para realizar la lectura de los encirculamientos, se toma como referencia las zonas de las variables dispuestas en el mapa. Si el encirculamiento se encuentra totalmente contenido en la zona perteneciente a una variable, ya sea directa o negada, esa variable forma parte de la expresión. Si el encirculamiento ocupa zonas donde una variable esta en forma directa pero también ocupa zonas donde dicha variable se encuentra negada, esa variable queda absorbida. La utilidad del mapa es que estas absorciones se evidencian gráficamente. Finalmente, la expresión simplificada de la función lógica, se obtiene realizando la suma lógica de los encirculamientos del mapa. Figura 3.37 Proceso de lectura de un mapa: 84 Ejemplo Minimizar mediante el mapa de Karnaugh la función dada por la siguiente tabla de verdad: D 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 C 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 A 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 F 1 0 1 1 1 1 1 0 1 0 1 0 0 1 0 0 Como puede observarse en el mapa, no hay 1's aislados. Los términos 0011 y 1101 tienen un vecino cada uno, que son respectivamente los minterms 0010 y 0101. Esto define los 2 primeros encirculamientos. Luego seguimos con los términos 0100 y 0110 que son vecinos entre sí -considerando la vecindad entre la columna de la derecha y la de la izquierda como si el mapa se cerrara en forma de cilindro vertical- y además con casillas de la fila superior, admitiendo un encirculamiento máximo de 4 elementos y absorbiendo 2 variables. Para terminar, nos falta encircular los 1's de las esquinas, que al considerar las vecindades entre la columna de la izquierda y la de la derecha que acabamos de indicar y entre la fila superior y la inferior (cilindro horizontal), nos permite reunirlos juntos en otro encirculamiento de 4 elementos (se absorben también aquí 2 variables). N ̅+ ̅ ̅+ Finalmente la función simplificada será: " = M N ̅ +M Funciones con términos indiferentes Como se mencionó anteriormente, algunas funciones presentan la particularidad de que ciertas combinaciones de sus variables de entrada nunca se pueden presentar, por lo que reciben el nombre de funciones incompletamente especificadas o funciones con términos indiferentes. No tiene sentido entonces hablar del valor de la función para estas combinaciones, ya que nunca se van a presentar (o no deberían presentarse). En los mapas y tablas, se les hace una marca distintiva (generalmente una “x”). Estos valores no especificados de la función pueden considerarse como unos o ceros, según convenga para obtener la expresión mínima. 85 Ejemplo Minimizar la expresión de la función indicada en el mapa de Karnaugh de la figura 3.31 En a) se han marcado los encirculamientos tomando en cuenta sólo los “1’s”, lo cual equivale a suponer “0” los valores no especificados. La expresión mínima para F en estas condiciones resulta de leer los tres N N ̅ encirculamientos: " = M +M +M (a) Figura 3.38 (b) Mapa con inespecificaciones a) Encirculamiento de los unos del mapa b) Encirculamiento utilizando adecuadamente los valores no especificados: En cambio si se utilizan los valores no especificados (x) de manera conveniente, se pueden realizar los N encirculamientos marcados en b), con lo cual la expresión de F resulta más compacta: " = +M Esto significa haber considerado como “1’s” los valores no especificados incluidos en los encirculamientos y como “0’s” los restantes. Si se llegaran a presentar las combinaciones prohibidas de los valores de entrada, los valores no especificados tomados como “0’s” no activarán la función F (F = 0) y los tomados como “1’s” sí la activarán (F = 1). Diseño de circuitos lógicos Una vez que se encuentra definido el comportamiento y funcionalidad que debe resolver un circuito lógico, el diseño consiste en la implementación de la función lógica que describe las reglas a aplicar sobre las entradas para obtener la salida deseada. A este efecto, se propone una metodología de diseño en base a los conceptos hasta aquí vertidos, siguiendo los siguientes pasos: 1. Obtener la tabla de verdad. Como se ha mostrado en los apartados previos, la tabla de verdad es una forma de representación de la función lógica. Puede obtenerse a partir de la descripción de las condiciones a cumplir o en caso de disponer de una expresión booleana, evaluando dicha expresión para las combinaciones posibles de las variables de entrada. 2. Minimización de la función lógica. Como criterio de optimización de diseño, se debe buscar la implementación de la expresión mínima de la función. Utilizaremos el método de mapas de Karnaugh para obtener la expresión mínima. 86 3. Implementación a nivel de compuertas. Según la complejidad de la función lógica, la implementación puede realizarse mediante compuertas lógicas que conformen un conjunto completo (compuertas universales). Cabe mencionar que otras alternativas para el diseño de circuitos lógicos (que no serán tratadas aquí), incluyen el uso de simuladores, emuladores y lenguajes de descripción de componentes de hardware. Concepto eléctrico de Entrada y Salida de un circuito Hemos descrito las entradas y salidas de los circuitos digitales como señales eléctricas de tensión o voltaje que representan valores lógicos. Describiremos a continuación aspectos a tener en cuenta en el análisis de circuitos lógicos desde el punto de vista eléctrico. En la Figura 3.39 se muestra el bloque funcional representativo de un circuito o dispositivo electrónico digital cualquiera con una entrada y una salida, en donde se indican los terminales de alimentación del circuito y los terminales de entrada y salida del mismo. Figura 3.39 Bloque funcional representativo de un dispositivo eléctrico / electrónico cualquiera: El terminal GND es el terminal de masa o tierra del circuito. Es el punto de referencia de potencial eléctrico al que se le asigna el nivel de tensión cero y al cual se conecta el borne negativo de la fuente de alimentación. El terminal de alimentación del circuito, Vcc, es el terminal por donde se aplica la tensión de alimentación al circuito, es decir, en el cual se conecta el borne positivo de la fuente de alimentación. Dado que estas conexiones son un requisito práctico para el funcionamiento del circuito, por simplicidad se suele omitir la representación de estos terminales en los diagramas circuitales. En el bloque funcional, Ve representa la señal eléctrica aplicada en la entrada y Vs la señal eléctrica generada o volcada por el circuito sobre su salida. Se define como entrada de un circuito o dispositivo electrónico a aquel terminal por donde el circuito está preparado para “recibir” una señal eléctrica de entrada. Esta señal eléctrica de entrada es la diferencia de potencial o voltaje Ve aplicado entre dicho terminal de entrada y la masa o tierra del circuito. En el diagrama funcional se identifica el terminal de entrada con una flecha de sentido entrante al circuito o al bloque funcional representativo del mismo. De la misma manera, se define como salida de un circuito o dispositivo electrónico al terminal por donde el circuito “vuelca o coloca”, a modo de un generador eléctrico o fuente de alimentación, una señal eléctrica de salida. Esta señal eléctrica de salida es la diferencia de potencial o voltaje Vs generado entre dicho terminal de salida y la masa o tierra del circuito (ver Figura 3.39). En un diagrama funcional se puede identificar al terminal de salida con una flecha de sentido saliente del circuito o bloque funcional representativo del mismo. La 87 señal de salida de un circuito puede usarse como la señal de entrada a otro circuito, estableciendo una conexión eléctrica entre ambos. Es importante aclarar que las flechas identificatorias de los terminales de entrada y de salida mostradas en el diagrama de la Figura 3.39 se grafican a los fines de resaltar la función de dichos terminales en el circuito. Estas flechas no indican el sentido de circulación de corriente en los terminales, sino que simbolizan su carácter de entrada o salida. Como veremos más adelante, la circulación de corriente puede ser saliente o entrante, independientemente de que se trate de un terminal de entrada o de salida, Con esto se pretende dejar en claro que las entradas y salidas de un dispositivo no son corrientes propiamente dichas sino que son valores de voltaje o tensión presentes en los respectivos terminales. En el caso de circuitos lógicos, las entradas y salidas serán señales eléctricas digitales binarias que materializan “ceros” y “unos” a través de dos intervalos de tensión bien diferenciados (ver Figura 3.7). También se debe tener en cuenta que el bloque funcional de la Figura 3.39 representa un circuito con una sola entrada y una sola salida, pero en general, un circuito puede tener varias entradas y varias salidas. Ejemplo Sea el circuito lógico mostrado en la Figura 3.40, compuesto por una compuerta inversora. Se muestra el terminal de alimentación Vcc y el terminal GND (masa del circuito), los cuales deben conectarse a los bornes positivo y negativo de la fuente de alimentación, respectivamente. (a) (b) Figura 3.40 a) Terminales de un circuito lógico b) Diagrama temporal En el terminal de entrada, se aplica al circuito la señal Ve, una señal eléctrica digital que toma un valor de tensión de 0 volts en nivel BAJO y 5 volts en nivel ALTO. El diagrama temporal muestra un ejemplo de los valores que toma esta señal digital de entrada. En el terminal de salida, el circuito vuelca los valores de la señal eléctrica Vs, que es una señal eléctrica digital cuyo valor depende de los valores de la señal de entrada. En este caso, por tratarse de un circuito compuesto por un INVERSOR, la señal de salida Vs será el complemento booleano de la señal de entrada Ve, tal como se muestra en el diagrama temporal. 88