Guión

Anuncio

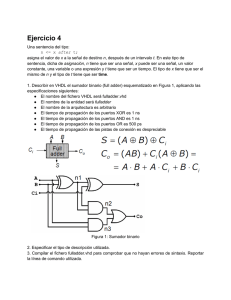

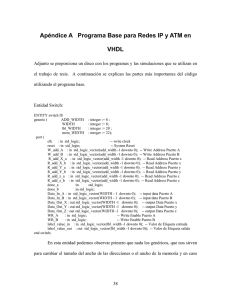

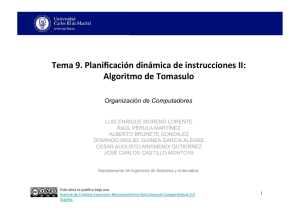

Fundamentos de los Computadores Guión de la práctica 3. Fecha de entrega: ● Grupo A: 03/Dic ● Grupo B: 02/Dic ● Grupo C: 28/Nov Objetivo de la práctica En esta práctica se modelarán en VHDL dos componentes más del ARC (banco de registros y contador de programa). Como se indica en la página de normas, la práctica se entregará dejándola en el servidor de la Escuela. IMPORTANTE: Los nombres de los archivos que se entregarán deben ser del estilo: • • P3X.VHD para el modelo pedido en el ejercicio. P3X_TB.VHD para su banco de pruebas –testbench–. Donde X es la letra del ejercicio. Por ejemplo, para el ejercicio a) se entregarán dos archivos, P3A.VHD y P3A_TB.VHD. Se deberán usar los nombres especificados para las entidades y sus entradas/salidas. Ejercicios a) (OBLIGATORIO) Implementar el banco de registros de ARC. Este microprocesador tiene 32 registros de propósito general, de 32 bits, de los cuales el primero (r0) está siempre a 0. Este banco permite el acceso simultáneo a tres registros, que se denominarán Rd, Rs1 y Rs2. El acceso a Rd será de lectura/escritura, mientras que a Rs1 y Rs2 se accederá sólo para lectura. La escritura será síncrona, en flanco de subida y habilitada con la señal WE, mientras que la lectura será siempre combinacional. Entidad: REGS. Entradas: CLK, WE, RD_IN(31 downto 0), RD_ADDR(4 downto 0), RS1_ADDR(4 downto 0) y RS2_ADDR(4 downto 0). Salidas: RD_OUT(31 downto 0), RS1(31 downto 0) y RS2(31 downto 0). b) (OBLIGATORIO) Construir el bloque de contador de programa de ARC. Este microprocesador tiene tres tipos de saltos: cortos (22 bits, branch), largos (30 bits, call) y direccionados por registro (32 bits, jump). Puesto que los saltos pueden ser hacia delante o hacia detrás, la magnitud a saltar debe considerarse como un número en complemento a 2, y debe hacerse una extensión a 32 bits con signo antes de sumarla al valor actual del contador de programa.. Además, tanto los saltos cortos (branch) como los largos (call) deben multiplicarse por 4 antes de sumarse. La actualización del contador de programa se hará siempre síncronamente, en flanco de subida, siempre que la señal UPDATE esté activada. Si no se especifica ningún salto, el contador de programa avanzará a la siguiente instrucción (se le sumará 4, puesto que las instrucciones son de 32 bits). El reset, que será asíncrono, llevará el contador de programa a la posición 0. Entidad: REGS_PC. Entradas: CLK, nRST, SHORT_DISP(21 downto 0), LONG_DISP(29 downto 0), JUMP_ADDR(31 downto 0), BRANCH, CALL, JUMP y UPDATE. Salida: PC(31 downto 0). La siguiente figura detalla este funcionamiento: SHORT_DISP x 4 SXT BRANCH 4 MUX LONG_DISP x 4 SXT CALL MUX + JUMP_ADDR JUMP UPDATE CLK CE MUX PC nRST c) (OPTATIVO) Implementar el autómata de moore dado por el diagrama de estados adjunto. Es un circuito secuencial que funciona en flanco de subida del reloj y tiene un reset asíncrono activo a nivel alto. Al producirse el reset el autómata se sitúa en el estado 0. Tiene una única entrada de un bit y la salida es de dos bits. Se pide implementar este autómata así como un banco de pruebas para comprobar su funcionamiento. Los detalles se encuentran en la plantilla suministrada. La implementación se debe realizar utilizando dos procesos. Uno que almacena el estado y realiza las transiciones y otro combinacional que calcula las salidas asociadas a cada estado.