Problemas 03-04 - Arquitectura de Computadores y Automática

Anuncio

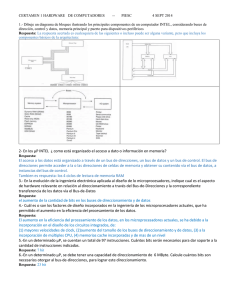

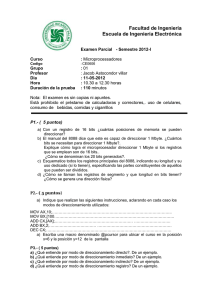

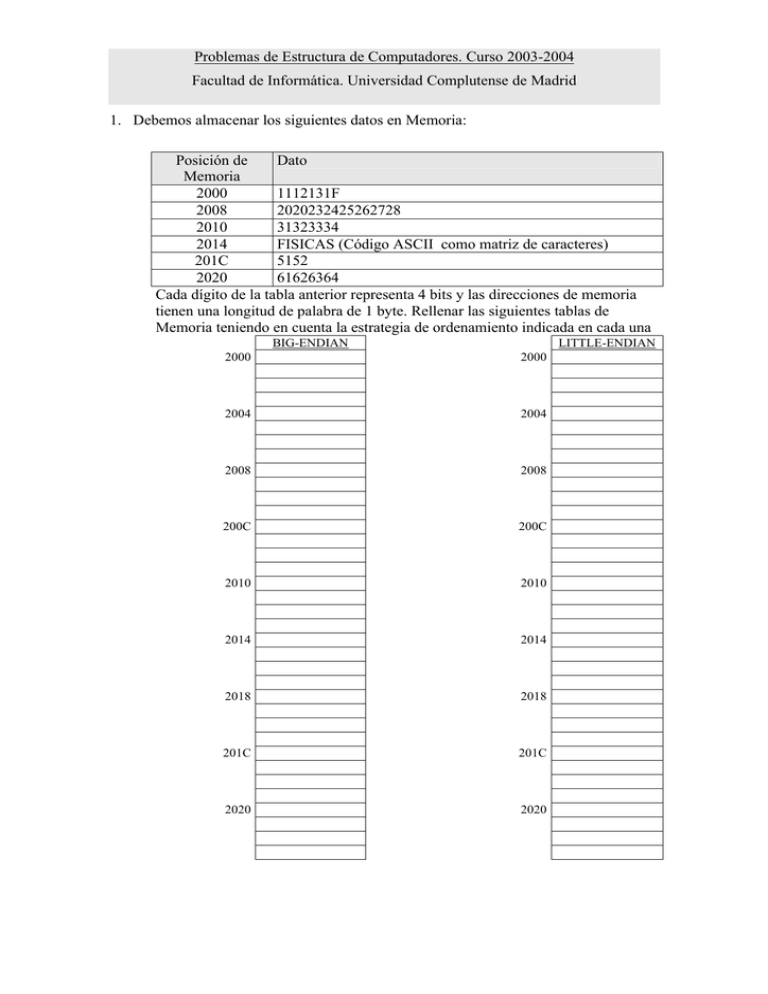

Problemas de Estructura de Computadores. Curso 2003-2004 Facultad de Informática. Universidad Complutense de Madrid 1. Debemos almacenar los siguientes datos en Memoria: Posición de Dato Memoria 2000 1112131F 2008 2020232425262728 2010 31323334 2014 FISICAS (Código ASCII como matriz de caracteres) 201C 5152 2020 61626364 Cada dígito de la tabla anterior representa 4 bits y las direcciones de memoria tienen una longitud de palabra de 1 byte. Rellenar las siguientes tablas de Memoria teniendo en cuenta la estrategia de ordenamiento indicada en cada una BIG-ENDIAN LITTLE-ENDIAN 2000 2000 2004 2004 2008 2008 200C 200C 2010 2010 2014 2014 2018 2018 201C 201C 2020 2020 Problemas de Estructura de Computadores. Curso 2003-2004 Facultad de Informática. Universidad Complutense de Madrid 2. Suponiendo instrucciones con un solo operando y teniendo en cuenta el modo de direccionamiento indicado, rellenar la siguiente tabla suponiendo que el contenido de la memoria es el del ejercicio anterior con ordenación del tipo “Big-Endian” y tamaño de operando doble palabra. Modo de direccionamiento Inmediato Absoluto Directo a Registro Indirecto con Registro Indirecto con Memoria Registro Base Instrucción Valor del Operando Dirección efectiva (Hex) del Operando (Hex) OPCODE 2008 OPCODE 2008 OPCODE OPCODE 0000 OPCODE OPCODE +3(01) (R4) 2020 Disponemos de un banco de 6 registros con el siguiente contenido Registro R0 R1 R2 R3 R4 R5 Contenido 2014 2009 2010 4325 201C 2712 3. Se desea diseñar un repertorio de instrucciones con el menor número de bits posible. La memoria puede direccionar hasta 28 palabras. Se permite aunque no es obligatorio que el código de operación sea variable. El banco de registros tiene 9 posiciones. El conjunto de instrucciones está compuesto de: a. 20 instrucciones de 3 operandos que permiten direccionamiento directo e indirecto de registro b. 150 instrucciones de 2 operandos que permiten direccionamiento absoluto e indirecto de memoria. c. 30 instrucciones de 1 operando con direccionamiento absoluto d. 26 instrucciones de 0 operandos Rellenar la siguiente tabla con el número de bits necesarios para cada tipo de instrucción: Tipo de OPCODE Operando1 Operando 2 Operando 3 Total Instrucción Modo Valor Modo Valor Valor Modo 3 operandos 2 operandos 1 operando 0 operandos Máximo Problemas de Estructura de Computadores. Curso 2003-2004 Facultad de Informática. Universidad Complutense de Madrid 4. Sabiendo que la palabra de memoria tiene 32 bit y que el repertorio de instrucciones tiene 16 instrucciones diferentes, ¿Cuál es la máxima memoria direccionable? a) Tengo dos operandos con acceso directo a memoria (DM) b) 1 operando con acceso directo (DR) a un banco de 32 registros y un operando con DM c) 3 Operandos con DM d) 1 solo operando DM 5. Sabiendo que la palabra de memoria tiene 28 bits y que el repertorio de instrucciones tiene 12 instrucciones diferentes, la instrucción tiene dos operandos con un modo de direccionamiento directo a memoria. ¿Cuál es la máxima memoria direccionable? ¿qué tamaño debe tener el registro contador de programa? ¿Se te ocurre algún método para conseguir direccionar más memoria sin modificar los modos de direccionamiento ni el tamaño de la palabra de memoria. 6. Sabiendo que una memoria tiene un bus de direcciones de 8 bits, un banco de 8 registros y dieciséis operaciones diferentes. ¿Cuál será la longitud del registro de instrucciones? a) suponiendo que las instrucciones tienen dos operandos cuyo modo de direccionamiento es directo a memoria. b) suponiendo que la instrucción tiene tres operandos con modos de direccionamiento directo a memoria c) suponiendo que uno de los modos de direccionamiento es directo a registro y tres operandos. d) suponiendo que existen 7 modos de direccionamiento diferentes para dos operandos. 7. Suponemos una memoria de con un bus de direcciones de 16 bits y un banco de registros de 16 registros. Los modos de direccionamiento utilizados van a ser tres directo a memoria, directo a registro, inmediato de 8 bits. Las operaciones con sus correspondientes modos de direccionamiento van a ser las siguientes: suma dr,dr suma dr,dm suma dm,dr suma dm,dm move #in,dr bcne dm bcgt,dm ¿Cual es la longitud máxima de la instrucción? Encontrar todos los formatos de las instrucciones. Problemas de Estructura de Computadores. Curso 2003-2004 Facultad de Informática. Universidad Complutense de Madrid 8. Determinar la longitud del formato de las instrucciones de un procesador sabiendo que el formato tiene tres campos: Código de Operación, Operando Fuente y Operando Destino, el procesador dispone de un repertorio de ocho instrucciones, el único modo de direccionamiento de los operandos es el directo absoluto y la Memoria Principal dispone de 512 posiciones. 9. Se desean comparar 2 Máquinas ESCOCIA y GALES, para ello debemos calcular distintos parámetros. La Maquina ESCOCIA funciona a 1,6 MHz , tiene un tamaño de palabra de memoria de 64 bits, tiene 64 registros de propósito general, tiene 3 tipos de Instrucciones I, R y J con código de operación fijo. Las 20 instrucciones de tipo I tardan 2 ciclos en ejecutarse y se ejecutan en el 30 % de las ocasiones, tienen 3 operandos con modos de direccionamiento Directo a Registro los 2 primeros e Inmediato el tercero, las 20 instrucciones de tipo R tardan 4 ciclos en ejecutarse y se ejecutan en el 50 % de las ocasiones, tienen 3 operandos con modos de direccionamiento Directo a Registro los 2 primeros e Indirecto con registro base y desplazamiento el tercero. Las 24 instrucciones de tipo J tardan 5 ciclos en ejecutarse y se ejecutan en el 20 % de las ocasiones, tienen 1 operandos con modo de direccionamiento Directo a Memoria. La máquina GALES por su parte funciona a 1MHz, tiene un bus de direcciones de memoria de 30 bits, Tiene 8 registros de propósito general, y tiene 7 tipos de Instrucciones con código de operación fijo y según las características de la siguiente tabla: Tipo Cantidad Modo Op1 A 20 DR B 128 C Modo Op2 Modo Op3 Ciclos Porcentaje DR ----- 2 20% DR DR DM 4 48% 20 DR DM ----- 3 5% D 4 IR INM 8 BITS ----- 2 12% E 20 DM DM ----- 5 4% F 44 DM INM 8 BITS ----- 5 6% G 20 IR DR DM 5 5% Calcular para ambas máquinas a) El formato de las instrucciones b) Tamaño de la memoria c) Tamaño de la palabra de memoria d) Rendimiento máximo e) CPI f) Tiempo de CPU 10 g) Tipo de Arquitectura CISC o RISC (Justifícalo) Problemas de Estructura de Computadores. Curso 2003-2004 Facultad de Informática. Universidad Complutense de Madrid 10. Un programa consta de 140 instrucciones de las cuales 70 tardan en ejecutarse cuatro ciclos, 35 tardan cinco ciclos, 20 tardan tres ciclos y las 15 restantes tardan, siete ciclos. Calcular el CPI promedio para dicho programa. Si el procesador funciona a una frecuencia de 2.0 GHz, averiguar el tiempo que se tarda en ejecutar el programa. 11. Se dispone de los siguientes datos respecto a dos potentes procesadores y una determinada tarea de aplicación: Power PC a 1.8 GHz de frecuencia y 700 MIPS de potencia. Pentium 4: 1.6 GHz de frecuencia y 850 MIPS. Calcular el CPI de cada procesador. 12. Un computador tiene un rendimiento de 3 MFLOPS normalizados al ejecutar una determinada tarea con cálculo intensivo en coma flotante. Si la operación de multiplicación equivale a cuatro operaciones en coma flotante sencillas y la de exponenciación se equipara con 8, calcular el tiempo que se tarda en realizar la tarea sabiendo que consta de las siguientes operaciones en coma flotante: 4000 sumas, 1500 multiplicaciones y 2200 operaciones de de exponenciación. 13. Se dispone de un computador dotado del procesador Power PC a 1.8 GHz y otro con el Pentium 4 a 1.6 GHz . Se sabe que el CPI del primero es de 5,5 y el del segundo de 7 para un determinado programa escrito en lenguaje de alto nivel. El programa que traduce dicho programa a instrucciones máquina del Power PC lo convierte en nueve millones de dichas instrucciones, mientras el que realiza la misma traducción a instrucciones máquina del Pentium lo convierte en 7.200.000 instrucciones. ¿Cuál de los computadores ejecutará más rápidamente la tarea? 14. Diseñar el formato de las instrucciones de un computador sabiendo que e repertorio de instrucciones consta de 20 instrucciones, sólo admite el modo de direccionamiento por registro y el banco de registros consta de ocho registros diferentes, en el formato de la instrucción se especifican tres campos: El primero, para el código de operación; el segundo, para el registro que contiene el operando fuente y el último, el correspondiente al operando destino. 15. Si en el computador del ejercicio 14 se encuentra una instrucción cuyo formato es: 00110001 101 y sabiendo que el código de operación para la instrucción de SUMA es 00110 y que todos los registros contienen el valor 02 H inicialmente. Interpretar la instrucción. ¿Qué registros cambian su contenido después de ejecutar dicha instrucción?. Si se repite dos veces la misma instrucción, ¿cuál es su resultado?. 16. Se desea comparar los anchos de banda máximos de un bus síncrono y otro asíncrono. El Bus síncrono tiene un tiempo de ciclo de reloj de 50ns, y cada transacción del bus requiere 1 ciclo de reloj. El bus asíncrono requiere 40ns para el protocolo de handshaking. Para ambos la sección de datos tiene una anchura de 32 bits. Encuentre el ancho de banda de ambos buses cuando realizan lecturas de una memoria de 200ns. Suponga que siempre se lee una palabra. 17. Dibujar el cronograma de un protocolo asíncrono para leer una palabra de memoria y recibirla en un dispositivo de Entrada / Salida (E/S). Problemas de Estructura de Computadores. Curso 2003-2004 Facultad de Informática. Universidad Complutense de Madrid 18. Encontrar el ancho de banda mantenido y la latencia para la lectura de 256 palabras en el caso de transferencias de bloques de 16 palabras. Calcular también el número de transacciones de bus por segundo, en cada uno de los dos casos, considerando una transacción o ciclo de bus como la transmisión de la dirección seguida de los datos. Suponga que tenemos un sistema con las siguientes características : Un sistema de memoria y de bus que soporta acceso a bloques de entre 4 y 16 palabras de 32 bits, Un bus síncrono de 64 bits a 200MHz en el que una transferencia de 64 bits requiere un ciclo y el envío de la dirección a memoria también requiere 1 ciclo. Se necesitan dos ciclos entre 2 operaciones de Bus (suponga que el bus está libre antes de cada acceso y el tiempo de acceso a memoria para las 4 primeras palabras es de 200ns, cada grupo adicional de palabras se lee en 20ns. Considere que la transferencia de datos leídos más recientemente por el bus puede solaparse con la lectura de las 4 palabras siguientes. 19. Suponer un sistema de arbitraje de 4 dispositivos Master conectados a un bus con prioridad decreciente (Prioridad (M1) >M2>M3>M4). Considere un tiempo de respuesta de 25ns (tdecodificación + tsetup + tskew). Se produce la siguiente secuencia: M4 pide el bus en t = 100 ns y lo utiliza durante 50 ns, M2 lo pide en t=200 ns por 50 ns, M3 en t = 330 ns y por 200ns y finalmente M1 pide el control del bus en t = 400ns hasta un nuevo evento. Dibujar el cronograma del sistema para a) Un arbitraje daisyChain, b) Protocolo de 3 hilos y c) Protocolo de 4 hilos. 20. Se desea controlar una impresora paralela a través de la PIA mediante E/S programada por respuesta. a) Indicar el proceso de transmisión especificando que señales de control se deben activar en cada uno de los pasos. b) Escribir el programa en ensamblador. 21. Se desea controlar una impresora serie conectada al MC6800 mediante un interfaz ACIA. a) Indicar el proceso de transmisión especificando que señales de control se deben activar en cada uno de los pasos y b) Escribir el programa en ensamblador. 22. Especificar el valor que se debe enviar al registro de control de una tarjeta ACIA para realizar una operación de E/S programada con espera de respuesta con las siguientes características: Frecuencia de transmisión la indicada por la CPU, recepción y transmisión con interrupciones, formato en código ASCII (7 bits), control de error par y un bit de stop. 23. Diseñar un registro de control de un interfaz serie que permita: a) Especificar 4 frecuencias de transmisión (*1, /16, /32, /64), b) Reset del interfaz, c)Transmisión y recepción ambas con o sin interrupciones, d) Formato de los datos : 7 u 8 bits, par, impar, sin paridad y1 ó 2 bits de stop. 24. Encontrar el ancho de banda mantenido y la latencia para la lectura de 256 palabras en el caso de transferencias de bloques de 16 palabras. Calcular también el número de transacciones de bus por segundo, en cada uno de los dos casos, considerando una transacción o ciclo de bus como la transmisión de la dirección seguida de los datos. Problemas de Estructura de Computadores. Curso 2003-2004 Facultad de Informática. Universidad Complutense de Madrid 25. Sea una memoria principal de 1 mega de tamaño con unos tiempos de acceso de 100ns y dividida en bloques de 2 palabras. Sabiendo que el sistema tiene una memoria cache asociativa por conjuntos de 28 con un grado de asociatividad de 4 y un tiempo de acceso de 10 ns, calcular a) nº de bits del bus de direcciones, b) nº de bloques por conjunto de la memoria cache, c) formato de las direcciones de memoria cache, d) mejora del rendimiento del sistema si la tasa de fallos es del 25% y d)Para poder implementar memoria virtual suponemos que el procesador genera direcciones de 64 bits. ¿Cuál es el formato de la dirección virtual si quisiéramos implementar una cache virtual parcial 26. Sea una memoria principal de 264 y una memoria cache de 26 .Sabiendo que la memoria principal tiene unos tiempos de acceso de 150 ns la memoria cache unos tiempos de acceso de 8 ns , sabiendo que la MP se divide en 262 bloques. Calcular: a) Formato de la dirección cache para la política de emplazamiento directo formato para la política de emplazamiento asociativo b) Formato para la política de emplazamiento asociativa por conjunto sabiendo que es una memoria cache de 4 vías. c) Tiempo de trabajo de la cache sabiendo que la tasa de fallos es del 20% d) Sabiendo que el tamaño de dirección virtual es el mismo que de dirección real y que una página es de 29 palabras. Formato de la dirección virtual. e) ¿Cuántas páginas puede tener un proceso activo? f) Suponiendo que el sistema operativo reserva 258 posiciones de memoria para virtualizar las memoria, ¿Cuántos procesos activos puede haber simultáneamente en el sistema. 27. Sea una memoria cache que tiene unos tiempos de acceso de 25ns una memoria principal con tiempos de acceso de 200ns y que el tiempo promedio de acceso a una posición de memoria secundaria es de 1 millón de ns y el tiempo de acceso al dato de 30ns. Sabiendo que las páginas son de 512 posiciones de memoria y los bloques de 8 posiciones y que de cada 50 accesos a memoria cache 40 son aciertos y de cada 100 accesos a memoria principal 3 son fallos calcular a) rendimiento de la de cache b) rendimiento de la memoria virtual c) rendimiento total de la jerarquía de memoria 28. ¿Cuál será el tamaño de dirección virtual si queremos páginas de 256 palabras y un máximo de 256 páginas por proceso activo?. Cuanta memoria debería reservar el sistema operativo para poder tener 16 procesos activos. ¿Máximo y mínimo número de conjuntos que puede tener una memoria cache asociativa por conjuntos que permite utilizar direcciones virtuales parciales?. Problemas de Estructura de Computadores. Curso 2003-2004 Facultad de Informática. Universidad Complutense de Madrid 29. Sea una memoria cache virtual solapada de 210 posiciones de memoria y grado de asociatividad 8. Sabiendo que la memoria principal se divide en bloque de 4 palabras y que el bus de direcciones virtuales y direcciones reales tiene el mismo tamaño.¿Cuántas páginas tiene un proceso virtual y cuantas palabras una pagina y cuantos bloques una página?. 30. Supongamos un sistema con las siguientes características: • Memoria cache de 4 marcos de bloque de 4 palabras de 1 byte, inicialmente vacía con re-emplazamiento LRU (en los casos en que sea necesario) • Memoria principal de 1KB dividida en dos páginas. • Memoria Virtual Paginada • Memoria secundaria de 8KB Se solicitan los accesos a las siguientes direcciones de una memoria de 1KB : 1, 4, 8, 5, 20, 17, 19, 56, 9, 11, 4, 43. Rellene las siguientes tablas para a) emplazamiento directo, b) Emplazamiento asociativo por conjuntos y c) Emplazamiento asociativo. Pos 1 4 8 5 20 17 19 56 9 11 4 43 B NB NM NM Ejemplo: Número de Marco NM 00 01 10 11 Ref. Directo (Fallo o acierto) Cont Ref: 1 0-3 Asociativo (Fallo o acierto) F Fallo o Acierto al referenciar la posición de memoria 1 Contenido después de la Referencia 1 Asociativo por conjuntos de 2 marcos (Fallo o acierto) 1 4 8 5 20 17 19 56 9 11 4 43 Contenidos de la cache al finalizar todas las referencias. Tipo de fallo Problemas de Estructura de Computadores. Curso 2003-2004 Facultad de Informática. Universidad Complutense de Madrid 31. Para el sistema de memoria del problema 30, calcular el formato de las direcciones físicas y virtuales, número de páginas de la memoria secundaria. ¿Como se implementaría LRU para la cache asociativa?. Anchura de los buses de direcciones de MC, MP y MS. 32. sabiendo que tienes una memoria con un bus de salida, un bus de entrada, un bus de control, un banco de 8 registros un bus de entrada y un bus de salida, un registro de instrucciones y sabiendo que una instrucción aritmético lógica es de la forma: op A,B, a) implementar el camino de datos que correspondiente suponiendo que A y B utilizan un modo de direccionamiento directo a registro. Suponer secuenciamiento implícito. b) Nº de ciclos para una operación. c) Indica las señales de control necesarias para controlar este camino de datos 33. Repetir el ejercicio 32 pero suponiendo un banco de registros con dos puertos paralelos. Compara el número de ciclos y la complejidad del hardware. 34. Repetir el ejercicio 32 pero suponga que el primer operando utiliza un modo de direccionamiento absoluto a memoria y el segundo absoluto a registro. Compara el número de ciclos y la complejidad del hardware. 35. Repetir el ejercicio 32 pero suponga que pero tanto el primer operando como el segundo puede utilizar un direccionamiento absoluto de memoria y de registro pudiéndose dar las cuatro combinaciones posibles de modos de direccionamiento. Comparar el número de ciclos y la complejidad del hardware. 36. Suponer un camino de datos con una memoria que tiene un bus de entrada y uno de salida y una UAL, un registro de instrucciones y secuenciamiento implícito. Implementar el camino de datos suponiendo que la instrucción tiene dos operandos cada uno de los cuales se pueden direccionar o bien con el modo relativo al contador de programa, o bien con el absoluto a memoria 37. Suponer que al problema 36 le añadimos un banco de registros de un único puerto y que se puede realizar también el direccionamiento absoluto a registro para los dos operandos. 38. Encontrar el camino de datos de un sistema sabiendo que la palabra de memoria tiene 32 bit y que el repertorio de instrucciones tiene 16 instrucciones diferentes, la instrucción tiene dos operando con un modo de direccionamiento directo a memoria. Delimita claramente donde están las fronteras de los chips que la implementan y que efectos tiene sobre el rendimiento. Marca claramente el tamaño de los buses y las señales que lo controlan. 39. Encontrar el camino de datos de un sistema sabiendo que la memoria tiene un bus de direcciones de 8 bits, que dispone de un banco de 8 registros y procesa dieciséis operaciones diferentes. Delimita claramente donde están las fronteras de los chips que la implementan y que efectos tiene sobre el rendimiento. Marca claramente el tamaño de los buses y las señales que lo controlan. Suponer que la instrucción tiene tres operandos con modos de direccionamiento directo a memoria.