Descarga PDF - Departamento de Arquitectura y Tecnología de

Anuncio

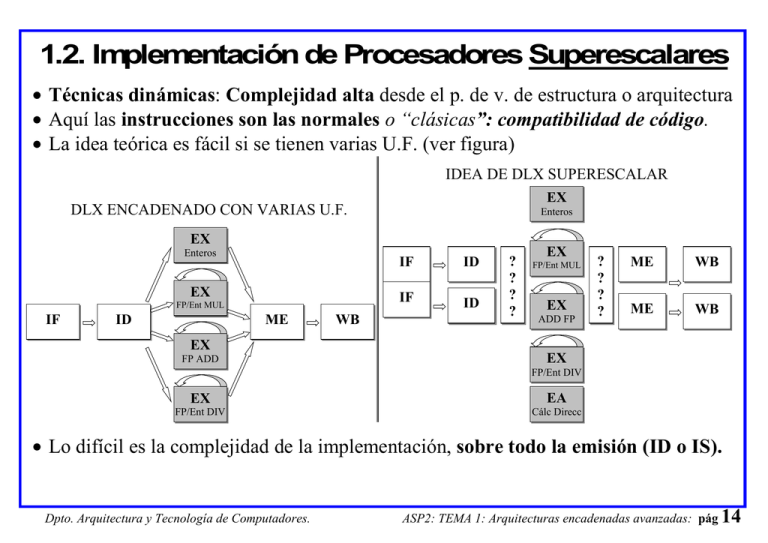

1.2. Implementación de Procesadores Superescalares • Técnicas dinámicas: Complejidad alta desde el p. de v. de estructura o arquitectura • Aquí las instrucciones son las normales o “clásicas”: compatibilidad de código. • La idea teórica es fácil si se tienen varias U.F. (ver figura) IDEA DE DLX SUPERESCALAR EX DLX ENCADENADO CON VARIAS U.F. Enteros EX Enteros EX FP/Ent MUL IF ID ME EX FP ADD WB IF ID IF ID ? ? ? ? EX FP/Ent MUL EX ADD FP ? ? ? ? ME WB ME WB EX FP/Ent DIV EX EA FP/Ent DIV Cálc Direcc • Lo difícil es la complejidad de la implementación, sobre todo la emisión (ID o IS). Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 14 • La fase de emisión juega un papel fundamental, y suele ser la más compleja y la que se alarga más al montar la superescalaridad: > Hay que detectar muchas más RAW en ella (de m instr) > Hay que decidir que instruc se pueden emitir (en función de las U.F. disponibles) > Hay que leer muchos registros a la vez (2m lecturas +m escrit. en la fase WB) > etc. • ⇒ Algunas máquinas (sobre todo primigenias, principios de los 90 y de sistemas empotrados), no disponen de planificación dinámica. En general, en estos procesadores, las m instrucciones deben cumplir ciertas reglas de emisión (fase ID) para que se emitan todas, (de lo contrario se emite un número menor que m). • Si una se bloquea toda la cadena sería muy caro en cuanto a prestaciones: 1 ciclo de bloqueo se nota mucho más que en un encadenado. Ej.: Encadenado CPI = 1 + CPIbloq . Si CPIbloq = 0.2 ⇒ A=1.2 Superescalar CPI= 1/m +CPIbloq. Si m=4, CPIbloq=0.2 ⇒ A=(0.25+0.2)/0.25 =1.8 • Tb existirán bloqueos de sólo algunas instrucciones de las m posibles. Ej: Superescalar m=4, donde en cada ciclo se consiguen ejecutar sólo 3 de las 4 instrucciones: IPC=3, CPI= 1/3 ⇒ A=CPI/CPIideal = 4/3 = 1.33 EJERCICIO: dibujar croquis del cronograma de estos casos. EJERCICIO: Calcular A si: en ciclos pares se ejec. m instr, pero en los impares sólo 1. Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 15 • Idem con las penalidades de fallo de caché, de fallo de predicción de BTB, etc. Influyen mucho en las prestaciones • La tendencia en máquinas de propósito general es sofisticar al máximo para evitar cualquier bloqueo y reducir penalidades. De ahí que en estas máquinas los superescalares con planif dinámica se hayan impuesto. • Los sistemas empotrados suelen llevar superescalares menos agresivos (o VLIW): > Menos transistores ⇒ menos consumo. > Aplicaciones específicas (y generalm. en ROM) ⇒ más fácil optimizar y sintonizar. • Todas poseen EMISIÓN DINÁMICA: el procesador (ID) decide en tiempo de ejecución qué instrucciones pueden emitirse a la vez y cuales no (en los VLIW la emisión es estática, o casi estática cuando se apoya en ciertos bits del compilador: el compilador debe preparar las instrucciones a emitir para que no haya riesgos estructurales y rellena con NOP para evitarlos). • Según la Emisión (Issue) y Planificación (Scheduling), siguientes modelos. Esto tampoco no es una clasificación rígida, sino modelos. Existen en la realidad muchos casos intermedios (cada procesador tiene sus peculiaridades, dependiendo de las tuberías que posee). Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 16 Emisión Dinámica Rígida (para que se emitan las m Planificación Estática (suponemos todos los bypasses). Instr. se encauzan por tuberías Dinámica (similar Algoritmo Tomasulo) Flexible (se emitirán las m instr., deben estar en cierto orden instr., sin importar el orden en en el código) que estén en el código) El procesador no tiene hw para El procesador sí conduce cada reconducir cada instr a su tubería instr a su tubería. Suelen existir reglas de emisión No tiene sentido Superescalar planif. dinámica • En los superescalares de planificación estática, suelen existir en la fase ID “reglas de emisión”. En ellos cada una de las m fases ID puede bloquearse por éstas (no ocurría en el DLX, excepto en las RAW de los saltos). “ESPECTRO” de máquinas con ILP TÉCNICAS DINÁMICAS TÉCNICAS ESTÁTICAS Superescalar con Superescalar con Superescalar sin Superescalar sin VLIW planificación planificación planificación dinámica, planificación puro dinámica, sin dinámica, pero con emisión dinámica (pero dinámica y reglas de emisión reglas de emisión reglas de emisión) emisión estática Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 17 Proc. Superescalares con Planificación estática • Recordar : IF ID EX MEM WB para procesadores sin planif dinámica. • CONCEPTO: EMISIÓN depende de TUBERÍAS (cadenas) • Trabajaremos con un caso simple de grado m=2, donde las dos tuberías o cadenas son casi totalmente independientes (muchos de los primeros superescalares eran así): o 1 Tubería FP o 1 Tubería INT + Acceso a Memoria o La única relación entre ambas tuberías, son los Ld/St para FP. • Ejemplos simples para éste: o si las instrucciones vienen por parejas INT/FP: se emiten 2 instr en ese ciclo o si todas las instrucciones son INT (programa entero) se emiten 1 instr/ciclo o Los bloqueos de emisión suelen afectar a todas las tuberías (suponemos que la fase ID no se ha completado y no se ha decodificado totalmente la instr.: no se sabe cuál es y por tanto, no se puede continuar emitiendo otras) o Los bloqueos de datos afectan por separado a cada tubería (son casi independientes) excepto en los Ld/St para FP. • Para evitar cualquier bloqueo por dependencia (un bloqueo es muy caro) vamos a suponer que sólo se producen los bloqueos estrictamente necesarios. Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 18 • En lugar de: FP MUL F1,F2,F3 IF ID M1 M2 M3 MEM WBF INT SF 0(R4),F1 IF ID EX - MEM WBI FP ADDF F0,F4,F5 IF ID A1 A2 MEM WBF INT XOR R5,R1,R2 IF ID EX MEM WBI • Ahora las dos cadenas o tuberías se montan lo más independientemente posibles, y por tanto quedaría así (los bloqueos de una no afectan a la otra). FP MUL F1,F2,F3 IF ID M1 M2 M3 MEM WBF INT SF 0(R4),F1 IF ID EX - MEM WBI FP ADDF F0,F4,F5 IF ID A1 A2 - (*) MEM WBF INT XOR R5,R1,R2 IF ID EX MEM WBI • Se han resaltado las fases que realmente usan recursos estructurales (U.F./acc. a caché datos, puertos de los fich registros); nótese que sólo se bloquea por la RAW la segunda tubería o cadena. NOTA: el ciclo de bloqueo de la primera tubería marcado con (*), sería más correcto dibujar en WBF, puesto que MEM no hace nada para FP. • Recordar. no permitimos emisión fuera de orden (out of order issue) ⇒ Si se bloquea ID, se deben bloquear todas las instr. posteriores. Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 19 Implementación (Superescalares Planif. estática) • IF: Políticas de búsqueda: ventana de instrucciones > Un superescalar de grado m puede lanzar o emitir hasta m instrucciones por ciclo, de forma que la caché debe ser capaz de atender esta demanda. Aumentar el ancho del bus de datos del caché sólo supone invertir más (chip mayor o de tecnología más precisa). Recordar que lo que no se puede rebajar son los tiempos de latencia (¡¡no se puede sobrepasar la velocidad de la luz!!) > El conjunto de instrucciones leídas en IF y susceptibles de entrar en las cadenas se le denomina ventana de instrucciones. Dos tipos de implementaciones: - Ventana fija: hasta que no se han lanzado o emitido todas las instrucciones de la ventana en su cadena correspondiente, no se puede acceder a caché a por otras m instrucciones (el búfer que recoge las instrucciones es fijo; está unido al bus). - Ventana deslizante: A medida que las instrucciones se van emitiendo a su correspondiente tubería, nuevas instrucciones son leídas de la caché para rellenar las posiciones inferiores de la ventana. Debe existir un registro (búfer) de desplazamiento. Más complejidad de IF, pero actualmente (para superesc. planif estática) es habitual que IF u otra fase “prepare” las m instr. siguientes para ID. Prestaciones mucho mayores sin gran complejidad. (unidad o búfer de prebúsqueda, prefetch buffer). Problema si las m instrucciones están en dos líneas distintas de caché Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 20 • ID > Se distribuyen (emisión) las instrucciones en la fase ID por tuberías (cadenas) con los bypasses necesarios entre ellas. > Suele haber reglas de emisión o emparejamiento. Ejemplos de reglas de emisión: - No tener RAW ni WAW (Pentium y otros). Nosotros supondremos que el bloqueo se producirá en la fase que necesita el dato. - Ir en cierto orden (ej: 1º entera/Ld/St/Salto y 2º flotante, HP 7100) o estar balanceadas en ciertos porcentajes (ej: Una entera/Ld/St/Salto y otra flotante, en cualquier orden). Hw simple porque la primera “tubería” es entera y la segunda es flotante: usan recursos distintos, excepto instrucc. Ld/St de FP. - Aquí la planificación estática o “scheduling” (del compilador) puede jugar un papel importante e intentar agrupar instrucciones sin dependencias y que cumplan los criterios. En general podemos hablar de dos modelos de emisión para los de planif estática: ♦ Emisión rígida: Superescalar de planificación estática y emisión rígida. Las instrucciones son emitidas desde la ventana de instrucciones (buffer de instrucciones de la fase IF) en el mismo orden en que llegaron, de manera que si una instrucción no es para la tubería (cadena) que le corresponde por su posición en la ventana, en el siguiente ciclo repetirá su etapa ID pero para otra cadena. Si tiene ventana fija: idea similar a VLIW pero con emisión dinámica. Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 21 (ej: 1º entera/Ld/St/Salto y 2º flotante, HP 7100, Alpha 21064) Sólo han de replicarse las IF, ID, y más puertos en WB. MEM se deja igual (se permite un único acc. a mem.). En EX se aprovechan las mismas U.F. Ej: El procesador Pentium (1992) fue un superescalar sin planif dinámica, construido alrededor de dos tuberías “casi” genéricas, capaces de ejecutar dos instrucciones en paralelo. Las tuberías son denominadas como U y V, y al proceso de emisión de dos instrucciones en paralelo se le llama emparejamiento. La tubería U puede ejecutar cualquier instrucción de la arquitectura Intel (tubería genérica), mientras que la tubería V puede ejecutar sólo las instrucciones simples (similares a las de un RISC, ver tabla 1). Cuando dos instrucciones se emparejan, la instrucción emitida en la tubería V es siempre la siguiente instrucción, (secuencialmente hablando según el código original) a la emitida en la tubería U. Las dos instrucciones no pueden tener dependencia RAW, ni WAW, y deben de cumplir ciertas restricciones (relacionadas con instr. CISC). Los saltos sólo pueden ser emparejados si van en la tubería V (se permite el emparejamiento de las instrucciones de comparación CMP o TEST, que escriben sobre una bandera (bit de estado), con un salto condicional (Jcc, cc=NE, EQ, GE, LE, NZ, etc.), que lea esa misma bandera). EJERCICIO: ¿Qué tipo es? Está claro que el Pentium debe tener replicada la unidad entera (dos U.F. ALU INT, una en cada tubería). Además la decodificación de las instrucc. CISC es compleja y sólo dispone de un decodificador para ellas. Vamos a suponer que siempre se emite al menos una instrucción por ciclo (si no, sería peor que un encadenado) Emisión rígida no resulta eficiente cuando el compilador no hace una buena planificación estática al ordenar instrucciones según las cadenas. Presentará bloqueos debidos a dependencias estructurales cuando la instrucción o instrucciones no estén en el mismo orden que las cadenas. Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 22 ♦ Emisión flexible: Superescalar de planificación estática y emisión flexible. Una instrucción de la ventana de instrucciones puede entrar en cualquier cadena que esté libre y admita dicha instrucción. Esta cualidad necesita de más complejidad en la cadena, que englobaremos en una nueva etapa SW (swap) donde las instrucciones son redirigidas a la cadena correspondiente. Esta etapa será para nosotros posterior a ID (IF ID SW EX MEM WB). Cuando una instrucción no pueda entrar en ninguna cadena tendrá que esperar al siguiente ciclo. > Como vemos poco a poco se va complicando la fase ID/SW (o IS), que es quizás el principal cuello de botella de los superescalares. • EX Vamos a suponer que en la fase EX van todas las U.F. (Si queremos independizar la ALU INT de los accesos a memoria, sólo hace falta añadir un sumador para calcular la dirección de acceso (EA, Effective Address). • MEM: Vamos a suponer sólo un acceso a la vez (estos superesc. son sencillos) • WB: Habrá que escribir en el fichero INT y FP a la vez. Si los Ld/St de FP están en la primera tubería, necesitan acceder al Fich de Reg FP en WB o ID. Contención en el fichero de registros por múltiples accesos. Si además el resultado del LD es usado por la instrucción FP tendremos un riesgo RAW. O esta contención es un riesgo estructural (que podría bloquear) o se duplican los puertos del fichero de registros. Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 23 > A pesar de ser emisión flexible, sigue bloqueándose cuando las parejas o el balanceo de instrucciones no es el adecuado. Ej.(se ha puesto un subíndice en los decodificadores para aclarar más la ejecución) Int Int Int FP FP FP ID - ID - ID ID ID - ID Int FP Int FP Int FP ID ID SW SW ID ID SW SW ID ID SW SW IPC= 6 instr/5 ciclos IPC= 6 instr/3 ciclos = 2 En proc reales, ID serían varias subetapas, y los bloqueos estarían en una de ellas. Habría que duplicar la U.F. INT como en el Pentium (el % instr. INT es mayor que el de FP), para evitar esto. Pero entonces... > Para m mayor y para evitar esto, interesa más la Planificación dinámica. Además las técnicas dinámicas aseguran la compatibilidad siempre. EJEMPLOS DE CASOS EMISIÓN Y VENTANA DE INSTR. Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 24 Ejemplo 2: Superescalar planif. estática • Supongamos un DLX superescalar de grado 2 (sin planificación dinámica) con las siguientes reglas de emisión: o 1 tubería de operación INT/salto/Acceso a memoria o 1 tubería de FP Notar que la detección de dependencias de datos (p. ej. RAW) la hace el hardware, pero los bloqueos hardware detienen la tubería. Sería interesante que el compilador reordenara las instrucciones para atenerse a las reglas de emisión y para evitar dependencias de datos. Supongamos (similar al DLX, duración EX FP=4 ciclos). Las UF están totalmente segmentadas (esto es habitual hoy día). Instrucción que Instrucción Latencia genera un dato que lo usa FP ALU otra FP ALU 3 FP ALU Store (FP) 2 Load (FP) FP ALU 1 Load (FP) Store (FP) 0 • Se pide: Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 25 a) Estudiar los conflictos estructurales b)Dibujar un cronograma y hallar el IPC, y el número de ciclos por elemento del vector procesado c) Desenrollar el código dado en 5 iteraciones y reordenar en función de las reglas de emisión y las dependencias. d)Comparar prestaciones y tamaño de código con el no desenrollado (notar que al desenrollar, el número de ciclos por elemento es la medida que interesa). e) ¿Influye en el IPC la restricción en el orden de la pareja a emitir (emisión rígida/flexible)? Proponer un código donde influya. Suponer BTB que siempre acierta. Suponer que ID/SW es una sola fase ID. for (i=N-1; i>0; i++) x[i] = x[i] +s; //N es divisible por P // F2←s ; R1 ← &x[N-1] Loop: LD F0, 0(R1) ADDD F4, F0, F2 SD 0(R1), F4 SUBI R1, R1, 8 BNEZ R1, Loop Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 26