07_Input Output

Anuncio

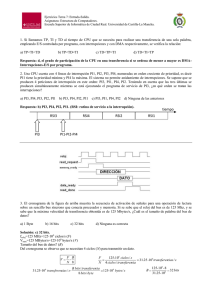

Entradas Salidas Velocidades Típicas de transferencia en Dispositivos I/O Entradas/Salidas: Problemas • Amplia variedad de periféricos —Entrega de diferentes cantidades de datos —Diferentes velocidades —Variedad de formatos • Todos más lentos que CPU y RAM • =>Necesidad de Módulos de I/O Entradas salidas: Criterios • Como acceder: ¿Aislada o mapeada? • Como ejecutar: Programada, Manejada por Interrupciones o DMA? Asignación de I/O • I/O Asignada en Memoria — Dispositivos y memoria comparten espacio de direccionamiento — Se maneja igual que operaciones sobre memoria (r,w) — Se usan las mismas instrucciones que para transferir datos de o a memoria • I/O Aislada — Espacio de direccionamiento separados — Son necesarias líneas para seleccionar I/O o memoria — Comandos especiales para I/O – Conjunto Limitado Decodificación de Direcciones (1) Ubicación de la EPROM, RAM, y PIO en un espacio de direccionamiento de 64 KB Decodificación de Direcciones (2) Full address decoding. Módulos de I/O: • Interfaz al CPU y Memoria • Interfaz a uno o mas periféricos Modelo Genérico de Módulo I/O Dispositivos Externos • Interrelación con seres Humanos —Pantalla, Teclado, Impresora • Relación con otras máquinas —Monitoreo y control • Comunicación —Modem —Tarjeta de Red - Network Interface Card (NIC) Dispositivo Externo: Diagrama de Bloques Módulo I/O: Función • • • • Control & Temporización Comunicación con el CPU Comunicación con el Dispositivo Almacenamiento temporal de datos (buffer) • Detección de errores Transacción I/O: Pasos • CPU chequea status en el módulo I/O del dispositivo • El módulo I/O returna el status • Si está listo, CPU solicita transferencia de datos • El módulo I/O obtiene datos del dispositivo • El módulo I/O transfiere datos al CPU • Variaciones para salida, DMA, etc. El módulo I/O: Diagrama Técnicas de Entrada Salida • Programada • Manejada por Interrupciones • Acceso Directo a Memoria Técnicas para Ingreso de un Bloque de Datos I/O Programada • CPU tiene control directo sobre I/O —sensar status —Comandos Read/write —Transferir datos • CPU espera al módulo I/O para completar la operación • Gasta tiempo de CPU I/O Programada - detalles • • • • CPU solicita operación I/O Módulo I/O ejecuta operación Módulo I/O establece bits de status CPU chequea bits de status periodicamente • Módulo I/O no informa al CPU directamente • Módulo I/O no interrumpe al CPU • CPU puede esperar o regresar mas tarde I/O Programada: Comandos • CPU emite dirección —Identifica modulo (& dispositivo if >1 por módulo) • CPU emite comando —Control – Dice al módulo que hacer – ej. girar disco —Probar - chequear status – ej. encendido? Error? —Leer/Escribir – El Módulo transfiere datos via el buffer desde o hacia el dispositivo I/O Programada: Asignada en Memoria y Aislada I/O Manejada por Interrupciones • Qué es una Interrupción? Es una llamada a subrutina iniciada por Hardware Fuentes: • Timer — Generado por un temporizador interno del procesador — Usado en multitarea • I/O — De un módulo de I/O • Falla de Hardware — ej. Error de paridad de memoria • Ejecución de un Programa — ej. división por cero I/O Manejada por Interrupciones Operación Básica • El CPU emite un comando de lectura • El módulo I/O obtiene datos del periférico mientras el CPU trabaja • El módulo I/O interrumpe el CPU • El CPU solicita los datos • El módulo I/O transfiere los datos Transferencia de Control via Interrupciones Ciclo de interrupción • Añadido al ciclo de instrucción • El Procesador chequea por interrupción • Si no hay Interrupción pendiente busca la siguiente instrucción • Si hay una interrupción pendiente: —Suspender ejecución del programa actual —guardar contexto —PC apunta al inicio de la rutina de atención —Completar el Procesamiento de la interrupción —Restablecer el contexto y continuar el programa interrumpido Ciclo de instrucción (con interrupciones) - Diagrama de Estados Cambios en Memoria y Registros En una Interrupción Desde el Punto de vista del CPU: • Emite un comando de lectura • Trabaja en otra cosa • Verifica interrupciones al finalizar cada ciclo de instrucción • Si es interrumpido:—Almacenar contexto de ejecución (registros) —Procesa la interrupción – Busca los datos & almacena Identificando el Modulo que Interrumpe (1) • Diferentes lineas para cada modulo —PC —Limita el número de dispositivos • Encuesta por Software —El CPU interroga por turno a cada módulo —lento Identificando el Modulo que Interrumpe (2) • Daisy Chain o Encuesta por Hardware —Reconocimiento de la Interrupción devuelta por una cadena —Módulo responsable coloca el vector en el bus —CPU usa el vector para identificar rutina de servicio • Arbitraje del Bus —Módulo debe solicitar el bus antes de interrumpir y colocar su vector —ej. PCI & SCSI Arbitraje de Bus (1) (a) Arbitraje centralizado, un nivel, Daisy Chain (b) Arbitraje centralizado, dos niveles, Daisy Chain Arbitraje de Bus (2) Arbitraje de bus descentralizado. Interrupciones Multiples: Manejo Secuencial Interrupciones Multiples: Anidadas Interrupciones Multiples: secuencia temporal Interrupciones Multiples: estrategias • Desabilitar Interrupciones —Mientras el Procesador procesa una interrupción, ignora otras —Otras interrupciones permanencen pendientes hasta finalizar el procesamiento de una interrupción —Son atendidas secuencialmente • Definir prioridades —Interrupciones de baja prioridad pueden ser interrumpidas por otras de mayor prioridad —Cuando el procesador termina de procesar la interrupción de alta prioridad, retorna a la interrupción previa. Ejemplo – Bus PC • 80x86 posee una línea de interrupción • Sistemas basados en el 8086 usan un controlador de interrupciones 8259A • 8259A tiene 8 líneas de interrupción Secuencia de Eventos • • • • • 8259A: acepta interrupciones 8259A: determina prioridad 8259A: señaliza al 8086 (sube línea INTR) CPU: Reconoce interrupción (IntA) 8259A: Coloca el vector adecuado en las líneas de datos • CPU: procesa interrupción Controlador de Interrupciones 82C59A Interfaz programable de periféricos Intel 82C55A Interfaz Teclado/Pantalla con el 82C55A Acceso Directo a Memoria • Entrada Salida programada y con interrupciones requiere participación activa del CPU —Velocidad de Transferencia es limitada —El CPU está atado • Respuesta: DMA Funciamiento del DMA • Requiere un módulo Adicional (hardware) conectado al bus • DMA recibe el control del sistema cedido por el procesador Diagrama Módulo DMA Típico Operación del DMA • CPU al controlador DMA: —Read/Write —Dirección de dispositivo —Dirección inicial del bloque de datos —Cantidad de datos a ser transferidos • CPU: trabaja en otra cosa • Controlador de DMA: —Prepara la transferencia —Interrumpe cuando termina la preparación Transferencia DMA: Robo de ciclos • Controlador DMA se apodera del bus por un ciclo • Transferencia de una palabra de datos • No es una interrupción —CPU no cambia de contexto • CPU suspendido justo antes de acceder al bus — antes de buscar operando, datos o escribir datos • Disminuye la velocidad del CPU pero no tanto como otros esquemas Puntos de acceso de DMA e Interrupciones en el Ciclo de Instrucción DMA: Configuraciones (1) • Bus único • Cada transferencia usa el bus dos veces —I/O a DMA luego DMA a memoria • El CPU es suspendido dos veces DMA: Configuraciones (2) • Bus único, Controlador Integrado a E/S • Cada transferencia usa el bus una vez —DMA a memoria • El CPU es suspendido una vez DMA: Configuraciones (3) • Buses separados para E/S • El Bus soporta todos los dispositivos habilitados para DMA • Each transferencia usa el bus una vez — DMA a memoria • CPU es suspendido una vez Diagrama Módulo DMA Típico Controlador DMA Intel 8237A • • • Interfaz para la familia 80x86 y la RAM Cuando el módulo DMA necesita el bus, señaliza HOLD al procesador CPU responde HLDA (hold acknowledge) — DMA puede usar el bus • Ej. transferir datos desde memoria al disco 1. Los dispositivos pueden solicitar servicio DMA, levantando DREQ (DMA request) 2. El DMA coloca alto HRQ (hold request), 3. CPU finaliza el ciclo de bus actual y coloca en alto HDLA (hold acknowledge). HOLD permanece alto durante la operación DMA 4. El DMA activa DACK (DMA acknowledge), indicando al dispositivo que inicie la transferencia 5. El DMA inicia la transferencia colocando la dirección del primer byte en el bus de direcciones y activando MEMR; entonces activa IOW para escribir al periferico. El DMA decrementa el contador e incrementa el apuntador de direcciones. Se repite hasta que el contador llega a cero. 6. El DMA desactiva HRQ, devolviendo el bus al CPU Uso del Bus de Sistema: DMA 8237 Fly-By • Mientras el DMA accede al bus, el procesador se detiene • Si el Procesador usa el bus, el módulo DMA duerme — Conocido como controlador DMA “fly-by” • Los datos no pasan a través ni son almacenados en el chip DMA — DMA Solamente entre un puerto I/O y memoria — No entre dos puertos I/O o dos localidades de memoria • Memoria a Memoria via registro • Chip 8237 contiene cuatro canales DMA — Programados independientemente — Solo uno activo a la vez — Enumerados 0, 1, 2, y 3 Buses • There are a number of possible interconnection systems • Single and multiple BUS structures are most common • e.g. Control/Address/Data bus (PC) • e.g. Unibus (DEC-PDP) Que es un Bus? • Un camino que comunica dos o mas dispositivos • Generalmente en “broadcast” • A menudo se agrupan lineas —P. ej. Un bus de datos de 32 bits corresponde a 32 líneas de un bit Bus de datos • Transporta datos —Ojo: en este nivel no hay diferencia entre “dato” e “instrucción” • El ancho suele ser una pieza clave en el rendimiento: —8, 16, 32, 64 bit Bus de Direcciones • Identifica la fuente o el destino de los datos • P. ej. El CPU necesita leer una instrucción (dato) en una posición de memoria • El ancho del Bus determina la capacidad máxima de memoria de el sistema —P. ej. Mic1 tiene bus de direcciones de 32 bits=> 4G capacidad de direccionamiento Bus de Control • Información de Control, Estado y temporización —read/write —Interrupt request —Señales de reloj Esquema de interconexion de Buses Arquitectura de Bus Tradicional (ISA) (con cache) Bus de alto rendimento Chipset 780G ATI Chipset G33 de Intel Controlador de memoria integrado Tipos de Buses • Dedicado —Separa datos & lineas de dirección • Multiplexado —Líneas compartidas —Ventaja: menos líneas —Desventajas: – Control + complejo – Desmejora el rendimiento PCI: Diagrama de temporización de lectura PCI: Arbitraje de Bus PCI: Arbitraje de Bus