MIA-Unidades 5 y 6 ()

Anuncio

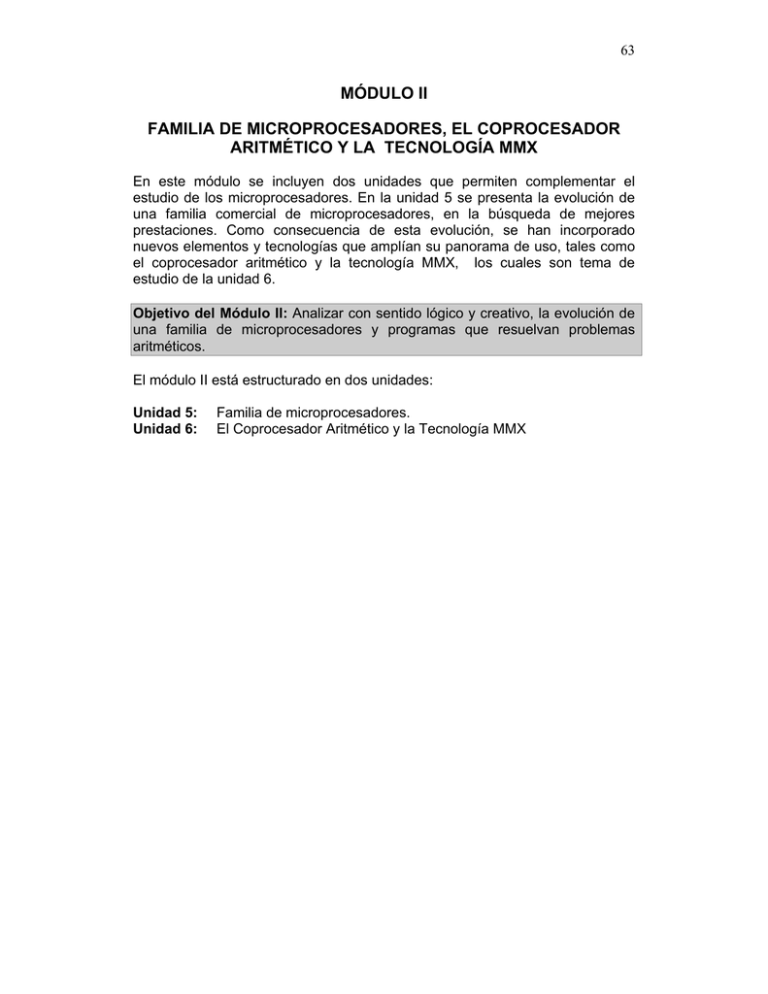

63 MÓDULO II FAMILIA DE MICROPROCESADORES, EL COPROCESADOR ARITMÉTICO Y LA TECNOLOGÍA MMX En este módulo se incluyen dos unidades que permiten complementar el estudio de los microprocesadores. En la unidad 5 se presenta la evolución de una familia comercial de microprocesadores, en la búsqueda de mejores prestaciones. Como consecuencia de esta evolución, se han incorporado nuevos elementos y tecnologías que amplían su panorama de uso, tales como el coprocesador aritmético y la tecnología MMX, los cuales son tema de estudio de la unidad 6. Objetivo del Módulo II: Analizar con sentido lógico y creativo, la evolución de una familia de microprocesadores y programas que resuelvan problemas aritméticos. El módulo II está estructurado en dos unidades: Unidad 5: Unidad 6: Familia de microprocesadores. El Coprocesador Aritmético y la Tecnología MMX 64 UNIDAD 5 Familia de Microprocesadores La historia de los microprocesadores (procesadores) ha pasado por diferentes situaciones, siguiendo la lógica evolución de este mundo. Desde aquel primer procesador 4004 del año 1971 hasta el Itanium producido en el 2001. Según la opinión de expertos, para el año 2011 se utilizará procesadores cuyo reloj irá a una velocidad de 10 GHz (10.000 MHz), contendrá mil millones de transistores y será capaz de procesar cerca de 100 mil millones de instrucciones por segundo. El factor responsable del gran aumento de la velocidad del microprocesador es la disminución del tamaño de los componentes del microprocesador; esto reduce la distancia entre componentes, y, por tanto, aumenta la velocidad. Sin embargo, la verdadera ganancia en velocidad en los últimos años se debe a la organización del microprocesador, incluyendo el uso de técnicas para obtener mejores prestaciones de servicio. La unidad 5, presenta la evolución de la Familia de Microprocesadores Intel, profundizando en las mejoras de hardware y software que han desarrollado los diseñadores sobre los miembros de esta familia en la búsqueda de un mejor desempeño. Mediante el conocimiento obtenido, se podrá describir importantes conceptos de diseño que han conducido al desarrollo de computadores más potentes. Objetivo de la Unidad 5: Analizar la evolución de la arquitectura y/o funcionamiento de microprocesadores comerciales, para la descripción de mejoras en sus prestaciones de servicio. Contenido de la Unidad 5: El contenido de la unidad contempla el estudio de los siguientes temas: Los microprocesadores 80186, 80188 y 80286. Los microprocesadores 80386 y 80486. Los microprocesadores Pentium y Pentium Pro. El microprocesador Pentium II 65 Actividades recomendadas para el estudio del contenido de la unidad 5. 1.- Examine la tabla 5.1, en ella puede identificar las lecturas de los temas contentivos de la unidad 5: TÍTULO Los microprocesadores 80186, 80188 y 80286. MATERIAL DE REFERENCIA CONTENIDO Arquitectura de los 80186 / 80188. Programación de las mejoras de los 80186 / El texto Los 80188. Microprocesadores Ejemplo de interfaz con el Intel, B. B. Brey. 80C188EB. CAPITULO 16 Introducción al 80286. Introducción al microprocesador 80386. Registros especiales del 80386 Administración de la memoria del 80386. Los microprocesadores 80386 y 80486. Acceso al modo protegido El texto Los Microprocesadores Modo 8086 virtual. Intel, B. B. Brey. Modo 8086 virtual. 17 Mecanismo de paginación de memoria. Introducción al procesador 80486. Introducción al procesador Pentium. Registros especiales del Pentium. Administración de la Los memoria del Pentium. El texto Los microprocesadores Pentium y Pentium Microprocesadores Nuevas instrucciones del Pentium. Intel, B. B. Brey. Pro. Introducción al microprocesador Pentium Pro. Características especiales del Pentium Pro. Tabla 5.1 18 66 TÍTULO MATERIAL DE REFERENCIA CONTENIDO Introducción al texto Los microprocesador El microprocesador El Pentium II. Microprocesadores Pentium II. Intel, B. B. Brey. Cambios al software del Pentium II. CAPITULO 19 Tabla 5.1 Continuación 2.- Una vez leído el contendido indicado en la tabla 5.1, usted estará en capacidad de responder lo siguiente: 2.1 ¿Cuál fue el primer microprocesador Intel de 32 bits? 2.2 ¿Cuántos períodos del reloj encontramos en un ciclo de bus de los 80186/80188? 2.3 ¿Cuántos bytes de memoria virtual direcciona la administración de memoria del microprocesador 80386? unidad de 2.4 Describa brevemente cómo funciona el sistema de memoria cache. 2.5 ¿A cuánta memoria puede acceder el microprocesador Pentium? 2.6 ¿Cuántas caches encontramos en el Pentium y cuáles son sus tamaños? 2.7 ¿Cuál es la diferencia entre la cache de nivel 2 en el Pentium Pro y la del Pentium II? 67 3.- Estudie la tabla 5.2 mostrada a continuación, la cual resume las especificaciones técnicas de los microprocesadores Intel: Fecha de Velocidad Ancho Número de Memoria Memoria presentación de reloj de bus transistores direccionable virtual Breve descripción 4004 15/11/71 108 KHz. 4 bits 2.300 (10 micras) 640 byte Primer chip con manipulación aritmética 8008 1/4/72 108 KHz. 8 bits 3.500 16 KBytes Manipulación Datos/texto 8080 1/4/74 2 MHz. 8 bits 6.000 64 KBytes 10 veces las (6 micras) prestaciones del 8008 1 MegaByte 10 veces las prestaciones del 8080 5 MHz. 29.000 8086 8/6/78 8 MHz. 16 bits (3 micras) 10 MHz. Idéntico al 8086 excepto en su bus externo de 8 bits 5 MHz. 8088 1/6/79 8 bits 29.000 8 MHz. 8 MHz. 134.000 80286 1/2/82 10 MHz. 16 Bits De 3 a 6 veces las prestaciones del 8086 16 Megabytes 1 Gigabyte 4 Gigabytes Primer chip x86 capaz de 64 manejar juegos Terabytes de datos de 32 bits (1.5 micras) 12 MHz. 16 MHz. Microprocesador 275.000 20 MHz. 17/10/85 Intel 386 DX® 32 Bits 25 MHz. (1 micra) 33 MHz. Microprocesador 275.000 16 MHz. 16/6/88 Intel 386 SX® 16 Bits 20 MHz. Bus capaz de direccionar 16 bits procesando Terabytes 32bits a bajo coste 64 4 gigabytes (1 micra) 25 MHz. Microprocesador 10/4/89 33 MHz. Intel 486 DX® (1 micra, 0.8 32 Bits micras en 50 4 Gigabytes MHz.) 64 Cache de nivel 1 en el chip Terabytes 50 MHz. 16 MHz. Microprocesador 22/4/91 Intel 486 SX® 1.185.000 20 MHz. 32 Bits 25 MHz. 33 MHz. 4 Gigabytes (0.8 micras) Idéntico en diseño al Intel 486DX, pero sin Terabytes coprocesador matemático 64 68 Fecha de Velocidad Ancho Número de Memoria Memoria presentación de reloj de bus transistores direccionable virtual Breve descripción 60 MHz. 66 MHz. 75 MHz. 90 MHz. Procesador 3,1 millones 100 MHz. 22/3/93 Pentium® 32 Bits 120 MHz. Arquitectura escalable. Hasta 5 veces las prestaciones Terabytes del 486 DX a 33 MHz. 64 4 Gigabytes (0.8 micras) 133 MHz. 150 MHz. 166 MHz. 200 MHz. 150 MHz. 5,5 millones Procesador 27/3/95 180 MHz. 4 Gigabytes 64 Bits PentiumPro® (0.32 micras) 200 MHz. 233 MHz. 7,5 millones Procesador 7/5/97 266 MHz. PentiumII® (0.32 micras) 300 MHz. S.E.C., MMX, Doble Bus Indep., Terabytes Ejecución Dinámica 64 4 Gigabytes 64 Bits Arquitectura de ejecución dinámica con procesador de Terabytes altas prestaciones 64 Tabla 5.2. Especificaciones técnicas de los microprocesadores Intel Fuente: http://www.duiops.net/hardware/micros/microshis.htm 4.- En el siguiente ejemplo se muestra el número de caches que se utilizan en los microprocesadores: Ejemplo 5.1: Número de caches en los microprocesadores. Cuando se introdujeron originalmente las caches, un sistema tenía normalmente solo una cache. Más recientemente, se ha convertido en una norma el uso de múltiples caches. El uso de de las memorias caches en los sistemas microprocesadores mejora la velocidad de proceso y sus prestaciones. Habitualmente se dimensionan caches de uno o dos niveles, aunque también hay sistemas con tres niveles. Los modernos microprocesadores tienen: • Caches on-chip (cache de nivel 1, L1): Proporcionan las mejores prestaciones. 69 • Cache off-chip módulo externo (constituye el nivel 2, L2): Tiene tiempos de acceso memores que la memoria principal. Las caches L2. Suelen ser de 512 KBytes o menos. Caches de mayores tamaños no son rentables. 5.- En el ejemplo 5.2, se muestra el número de caches presentes en los microprocesadores de la familia Intel. Ejemplo 5.2: Número de caches en los microprocesadores de la familia Intel. • • • • • 80386: Sin cache on-chip 80486: 8 KBytes de cache unificada. Lineas (bloques) de 16 bytes y organización asociativa en cuatro vías. Pentium (todas las versiones): Dos caches L1 on-chip. Cache partida de 16 KBytes, 8KBytes para datos y 8 KBytes para instrucciones. Pentium III: Se añade una cache L3 en la tarjeta (off-chip). Pentium 4: - Caches L1 de 8 KBytes, líneas (bloques) de 64 bytes, asociativa de 4 vías. - Caches L2: Unificada. Alimenta a las dos cache L1. - 256 KBytes, líneas de 128 bytes, asociativa de 8 vías. - Cache L3 on-chip. Atención: Los microprocesadores Pentium III y Pentium 4, no son objeto de estudio del curso Microprocesadores. . 6.- El ejemplo 5.3, presenta la evolución de la estructura de la cache, en la evolución de los microprocesadores de Intel. Ejemplo 5.3: Evolución de la estructura cache en los microprocesadores Intel. La evolución de la estructura cache se observa claramente en la evolución de los microprocesadores Intel. El 80386 no tiene cache on-chip. El 80486 incluye una sola cache on-chip de 8 KBytes, utilizando un tamaño de línea de 16 bytes y una organización asociativa por conjunto (la memoria cache se divide en conjuntos de n bloques, así al bloque i-ésimo de memoria principal le corresponde el conjunto i módulo (k/n) donde k es el número de bloques de memoria cache) de cuatro vías. En la figura 5.1, se presenta el diagrama de bloques del 80486, en el cual se aprecia la ubicación de la cache. 70 Figura 5.1. Diagrama de bloques del 80486. Fuente: http://www.duiops.net/hardware/micros/microshis.htm El Pentium II incluye dos caches on-chip, una para datos otra para instrucciones. Cada cache es de 8 KBytes, utilizando un tamaño de línea de 32 bytes y una organización asociativa por conjunto de dos vías. Incluye además una cache L2 que alimenta a las dos cache L1. La cache L2 es asociativa por conjunto de cuatro vías, y con tamaños que oscilan entre 256 Kbytes y 1 Mbyte. La figura 5.2 proporciona una visión simplificada de la estructura del Pentium II, resaltando la ubicación de las tres caches. 71 Bus del sistema Caché L2 (256K-1M) Unidad de interfaz del bus Caché de instrucciones L1 (8-16K) Captar Unidad de Captación y decodificación de instrucciones Cache de datos L1 (8-16K) Cargar Unidad de envío y ejecución Memorizar Unidad de retirada Depósito de instrucciones (buffer de reorden-ROB) Figura 5.2. Diagrama de bloques del Pentium II 7.- En el ejemplo 5.4 pone en evidencia la evolución de la arquitectura superescalar en los microprocesadores Intel, y describe la arquitectura superescalar del Pentium II. Ejemplo 5.4: Arquitectura superescalar del microprocesador Pentium II. El microprocesador 80486 no disponía de elementos superescalares, el Pentium original tenía unas características superescalares modestas, que consistían en la utilización de dos unidades de ejecución de enteros independientes. El Pentium Pro introdujo un diseño completamente superescalar. Por su parte, el Pentium II tiene básicamente la misma organización superescalar que el Pentium Pro. En la figura 5.2 mostrada anteriormente, se presenta el diagrama de bloques del Pentium II. Los elementos esenciales de la organización superescalar son: la unidad de captación y decodificación de instrucciones, la unidad de envío y ejecución, y la unidad de retiro. Se describe a continuación la operación de cada una de ellas: 72 Operación de la unidad de captación y decodificación. La figura 5.3 es un esquema simplificado de la unidad de captación y decodificación del Pentium II. La operación de captación consta de tres etapas encauzadas: Desde la cache de instrucciones Camino de 32 bytes IFU1 Buffer de instrucciones (contiene una línea) Siguiente IP 16 bytes Decodificador de longitud de instrucciones IFU2 Predicción dinámica de saltos 16 bytes Etapa de alineación para los decodificadores IFU3 16 bytes ID1 Decodificador 0 (complejas) Decodificador 1 (sencillas) Decodificador 2 (sencillas) Secuenciador de instrucciones de microcódigo 6 x 118 bits ID2 Cola de instrucciones decodificadas 3 x 118 bits 3 x 118 bits RAT Predicción estática de sºaltos Asignador de registros Al ROB Figura 5.3. Unidad de captación/decodificación del Pentium II Etapa IFU1 Capta instrucciones desde la cache de instrucciones, una línea (32 bytes) cada vez. La unidad <<Siguiente IP>> proporciona la dirección de la siguiente instrucción a captar, y se capta en el buffer IFU1 la línea de cache que contiene la instrucción. Esta operación no se calcula sencillamente incrementando el puntero, porque podría haber un salto o una interrupción pendiente que moviese el puntero a una posición diferente. Después el contenido del buffer IFU1 pasa IFU2 (16 bytes cada vez). Etapa IFU2 73 Esta unidad lleva a cabo dos operaciones en paralelo. IFU2 examina los bytes para determinar los límites de las instrucciones; esta es una operación necesaria, debido a que las instrucciones del Pentium son de longitud variable. Si alguna de las instrucciones es de salto, la unidad pasa la dirección de memoria correspondiente a la unidad de predicción dinámica de saltos. IFU2 pasa después el bloque de 16 bytes a IFU3, que es responsable de alinear las instrucciones para presentarlas al decodificador apropiado. Etapa IFU3 Para comprender el funcionamiento de esta etapa, es necesario describir la primera etapa de la unidad de decodificación de instrucciones, ID1. Esta etapa es capaz de manejar tres instrucciones en paralelo. ID1 traduce cada instrucción en de una a cuatro microoperaciones cada una de 118 bits. ID1 contiene tres decodificadores. El primero de ellos puede manejar instrucciones que se traduzcan hasta en cuatro microoperaciones. El segundo y el tercer decodificador maneja instrucciones sencillas que correspondan a una única microoperación (instrucciones registro a registro e instrucciones de carga). Si más de una instrucción es compleja, las instrucciones deben introducirse en ID1 en etapas, de tal modo que el segundo y tercer decodificador no se les dé una instrucción compleja. Las instrucciones que requieren más de cuatro microoperaciones, se transfieren al secuenciador de instrucciones de microcódigo (MIS, microcode instruction sequencer), el cual funciona como unidad microprogramada. La salida de ID1 o MIS se introduce en la segunda etapa de decodificación, ID2, es un bloque de hasta seis microoperaciones a la vez. En este punto, hay una segunda ocasión para predecir saltos. Las microoperaciones encoladas en ID2 pasan a través de una fase de renombramiento de registro (RAT, register allocator). El RAT transforma las referencias a lo 16 registros de la arquitectura. Después el RAT introduce las microoperaciones revisadas al buffer de reordenación (ROB, reorder buffer). Las microoperaciones entran al ROB en orden; después son enviadas desde el ROB a la unidad de envío/ejecución sin orden. Operación unidad de envío/ejecución La figura 5.4 es un esquema simplificado de la unidad de envío/ejecución del Pentium II. La central de reservas (RS, reservation station) es responsable de recuperar las microoperaciones del ROB., enviándolas a su ejecución y guardando los resultados de nuevo en el ROB. La RS busca en el ROB microoperaciones cuyo estado indique que la microoperación dispone de todos sus operandos. Si está disponible la unidad de ejecución que necesita una microoperación, la RS capta esa microoperación y la envía a la unidad de ejecución conveniente. Se pueden enviar hasta cinco microoperaciones en un ciclo. Hay cinco puertos que unen la RS a las cinco unidades de ejecución. El puerto 0 se usa para instrucciones con enteros y coma flotante, con la excepción de las operaciones sencillas con enteros y la gestión de las predicciones de saltos 74 erróneas que se asignan al puerto 1. Las unidades de ejecución MMX se asignan también a estos puertos. Los puertos restantes se utilizan para cargas y almacenamientos en memoria. Cuando se completa una ejecución, se actualiza la entrada adecuada del ROB, y la unidad de ejecución queda disponible para otra microoperación. Puerto 4 A/desde ROB C e Puerto 3 n t r a Puerto 2 l Unidad de ejecución de almacenamientos Unidad de ejecución de almacenamientos A/desde la cache de datos Unidad de ejecución de cargas d e Desplazador MMX ALU MMX R e s e r v a s Puerto 1 IEU (sencillas) Y JEU ALU MMX Multiplicador MMX IEU (complejas) Puerto 0 FPU (complejas) FPU (sencillas) Figura 5.4. Unidad de envío/ejecución del Pentium II Unidad de Retiro La unidad de retiro (RU, retire unit) va procesando el buffer de reordenación para entregar los resultados de la ejecución de instrucciones. En primer lugar la RU debe tener presentes los fallos en las predicciones de salto, y las microoperaciones que se hayan ejecutado pero para las cuales los saltos precedentes no se hayan validado. Una vez que se determina que una microoperación se ha ejecutado y no es vulnerable a eliminación debido a un fallo de predicción se marca como lista para ser retirada. Cuando se ha retirado la instrucción del Pentium previa, y todas las microoperaciones de la siguiente instrucción se han marcado como listas para ser retiradas, la RU actualiza los registros de la arquitectura afectados por esta instrucción, y quita del ROB la microoperación. 75 Ejemplo 5.5: Mejoras incorporadas al sistema de memoria del 80486. Dada la disponibilidad de sistemas de memoria muy grandes, y debido a que los costos de los circuitos son mínimos, muchos fabricantes de tarjetas de memoria han agregado la verificación de paridad a sus tarjetas de memoria RAM. Esto se pone de manifiesto al comparar el sistema de memoria del microprocesador 80386 y del 80486. Ambos sistemas contienen 4 GB, pero el sistema de memoria del 80486 incluye un generador / detector de paridad interno, para determinar si un dato es leído correctamente de una localidad de memoria. Ejercicios propuestos 1.- Explique cómo el modo pipeline alarga el tiempo de acceso para muchos accesos de memoria en un sistema basado en el microprocesador 80386. 2.- El avance de la tecnología ha traído consigo la aparición de una cantidad importante de nuevos bienes y servicios de carácter tecnológico, como los móviles, ordenadores, los servicios de Internet, etc. El desarrollo de la investigación e innovación permite la constante actualización y renovación del sector tecnológico, tal es el caso de la potencia de los microprocesadores la cual se duplica cada 18 meses. Con base a la información anterior analice la evolución de la velocidad de los microprocesadores Intel y describa las mejoras del desempeño obtenidas en la construcción de computadoras personales. Consulta en otros libros [Sayers 1995] trata arquitecturas prácticas de microprocesadores de 8, 16 y 32 bits. [Tokheim, 1995] incluye información sobre microprocesadores de la compañía Intel y Motorola. [Stallings 2000] Destaca las mejoras del diseño de microprocesadores tomando como ejemplos el microprocesador Pentium II y el PowerPC. Además se encuentra información sobre la arquitectura del microprocesador en cualquiera de los textos recomendados 76 Consulta en la Web http://www.duiops.net/hardware/micros/microshis.htm: Presenta la historia de los microprocesadores Intel. http://www.ac.uma.es/educacion/cursos/telecomunicacion/FundCompST/mas_ material/prestaciones/evolucion_80x86_n05.pdf: Muestra un cuadro en donde se resume la evolución de la familia de microprocesadores Intel. http://petra.euitio.uniovi.es/~i1766818/TUTOR/TUTOR06.htm#1: Describe de una manera muy sencilla los microprocesadores Intel a partir del modelo 80486. Ejercicios de Autoevaluación 1.- Si se compara la arquitectura del microprocesador 80386 con la del 80486 no se encontrará diferencias. Sin embargo el tiempo de ejecución de las instrucciones varía significativamente de un microprocesador a otro. Con base a la información analice cómo ha evolucionado el tiempo de ejecución de las instrucciones en estos microprocesadores para la mejora del desempeño. 2.- La unidad de coma flotante del microprocesador Pentium se ha rediseñado totalmente respecto a la que usa el 80486. Este desarrollo ha ocasionado la ejecución más rápida de operaciones aritméticas y de carga de datos. Tome como base lo antes expuesto y realice lo siguiente: - Estudie la construcción de la unidad de coma flotante en el Pentium II y describa las mejoras incluidas en su construcción para un mejor desempeño. Respuesta a los Ejercicios de Autoevaluación 1.- En el 80486 casi la mitad de las instrucciones son ejecutadas en un período de reloj, en vez de los dos períodos que necesita el 80386 para ejecutar instrucciones similares. 2.- La unidad de coma flotante del Pentium II, hace uso de nuevos algoritmos que aceleran la ejecución de las operaciones e incluye nuevos elementos de hardware dedicados, como son: un multiplicador, un sumador y un divisor. 77 UNIDAD 6 El Coprocesador Aritmético y la Tecnología MMX. Los procesadores del tipo 8086 solo podían realizar operaciones aritméticas con números enteros. Para los fraccionarios debían utilizar complicados artificios, por lo que desde el principio se crearon procesadores específicos y costosos para operaciones aritméticas con números fraccionarios. Puesto que la CPU no hace otra cosa que cálculos, el estudiante podría estar preguntándose por qué necesita ayuda para realizarlos. Lo que ocurre es que la CPU solo puede llevar a cabo operaciones aritméticas básicas con números enteros, para procesar operaciones con valores fraccionarios, requiere bastante tiempo lo que disminuye su velocidad considerablemente, debido especialmente a que la CPU tiene que ejecutar también otras tareas simultáneamente. En aquellos campos de aplicación donde se requieren muchas posiciones decimales y los errores de redondeo deben de mantenerse tan insignificantes como sea posible, resulta imprescindible la utilización de un coprocesador aritmético. A partir de la introducción del 80486, Intel incorporó el coprocesador aritmético junto con el procesador principal, por lo que su existencia dejó de ser opcional, convirtiéndose en estándar. Con cada generación de CPU utilizada en sistemas de computadoras personales Intel, también introducía su correspondiente coprocesador. La unidad 5 del presente material incluye el estudio del funcionamiento de la familia de coprocesadores aritméticos etiquetada como 80X87. También se incluye en esta unidad el estudio de la tecnología MMX, introducida por Intel en su línea de procesadores Pentium. Aunque no se pueda considerar la tecnología MMX como un procesador en si mismo, es uno de los mayores pasos que ha dado Intel. Este realce incluye 57 nuevas instrucciones muy optimizadas para tareas multimedia, estas instrucciones usan una técnica conocida como SIMD (single-instruction, multiple-data), es decir una secuencia de instrucciones y múltiples secuencias de datos que posibilita efectuar la misma operación, tal como una suma o una multiplicación con varios elementos de datos a la vez Objetivo de la Unidad 6: Analizar programas que resuelvan problemas aritméticos, para la descripción de la operación del coprocesador aritmético o de la tecnología MMX. Contenido de la Unidad 5: El contenido de la unidad contempla el estudio de los siguientes temas: Formato de datos y arquitectura del coprocesador aritmético. Conjunto de instrucciones y programación del coprocesador aritmético. La tecnología MMX: Tipos de datos y conjunto de instrucciones. 78 Actividades recomendadas para el estudio del contenido de la unidad 6. 1.- Examine la tabla 6.1, en ella puede identificar las lecturas de los temas contentivos de la unidad 6: TÍTULO MATERIAL DE REFERENCIA CONTENIDO CAPITULO Formato de datos para el coprocesador aritmético. Arquitectura de 80X87. El texto Los El Coprocesador Microprocesadores Conjunto de instrucciones. Aritmético y la Intel, B. B. Brey. Tecnología MMX. Programación con el coprocesador aritmético. . 14 Introducción a la tecnología MMX. Tipo de datos e instrucciones. Tabla 6.1 2.- Una vez leído el contendido indicado en la tabla 5.1, usted estará en capacidad de responder lo siguiente: 2.2 ¿Qué tipos de datos maneja el coprocesador? 2.8 ¿Qué tipos de números flotantes soporta el coprocesador? 2.9 ¿Cuáles son las directivas que emplea el coprocesador para almacenar datos? 2.10 ¿Para qué tipo de aplicaciones están diseñadas específicamente las instrucciones MMX? 3.- Estudie los siguientes contenidos teóricos a través de los cuales complementará los conocimientos adquiridos con las lecturas indicadas en la tabla 6.1: El Coprocesador Aritmético Es un microprocesador de instalación opcional, también denominado Unidad de Punto Flotante, que auxilia al microprocesador en el uso eficiente de programas de graficación, cálculos matemáticos complejos y diseño, lo cual al 79 especializarse en dichas funciones acelera la velocidad con que una computadora puede responder a necesidades tan sofisticadas. Los coprocesadores están todavía mas críticamente ajustados a la velocidad del reloj que los procesadores normales. Por lo tanto, debe asegurarse que cualquier coprocesador que se seleccione para un sistema esté diseñado para manejar la frecuencia de reloj de su computadora. Fuente: El autor. Instrucción Simple, Múltiples Datos (SIMD) Las aplicaciones de multimedia y comunicaciones de hoy en día con frecuencia usan ciclos repetitivos que, aunque ocupan el 10 por ciento o menos del código total de la aplicación, pueden ser responsables hasta por el 90 por ciento del tiempo de ejecución. El proceso denomina SIMD (Single Instruction Multiple Data) hace posible que una instrucción realice la misma función sobre múltiples datos, en otras palabras, las instrucciones ejecutan las operaciones simultáneamente en varios datos en paralelo. Un ejemplo de su funcionamiento en la realidad es con el vídeo: En los procesadores conocidos hasta la llegada del MMX llegaban 8 pixeles de datos gráficos de una en una y se procesaban separadamente. En los procesadores MMX, los 8 pixeles llegan al procesador en un paquete de 64 bits y se procesan a todos en una sola instrucción. Otro ejemplo lo tenemos aquí, en una muestra de sonido de 16 bits, podemos manipular hasta 4 muestras al mismo tiempo. Sobre una aplicación estándar, el rendimiento mejora entre un 10 y un 20 por ciento, pero cuando el programa ha sido diseñado específicamente para utilizar todo el potencial del MMX, el rendimiento puede llegar al 40 o 60 por ciento. http://neutron.ing.ucv.ve/revista-e/No3/Ferreira.html Pixel Píxel es la abreviatura de la expresión inglesa Picture Element (Elemento de Imagen), y es la unidad más pequeña que encontraremos en las imágenes compuestas por mapa de bits. El píxel es la unidad mínima en que se divide la retícula de la pantalla del monitor y cada uno de ellos tiene diferente color. Su tono de color se consigue combinando los tres colores básicos (rojo, verde y azul) en distintas proporciones. Un píxel tiene tres características distinguibles: Forma cuadrada Posición relativa al resto de píxeles de un mapa de bits. Profundidad de color (capacidad para almacenar color), que se expresa en bits. http://www2.canalaudiovisual.com/ezine/books/jirimag/1Imag21.htm Instrucciones MMX del Pentium Este conjunto de instrucciones está orientado a programación multimedia. Los datos de vídeo y audio suelen representarse mediante vectores o matrices 80 grandes, compuestos por datos de longitud reducida (8 o 16 bits), mientras que las instrucciones convencionales operan normalmente con datos de 32 o 64 bits. Estos son algunos ejemplos: En gráficos y en vídeo, cada escena consiste en una matriz de puntos de imagen, y hay 8 bits para cada punto de imagen u 8 bits para cada componente de color (rojo, verde, azul) del punto de imagen. Las muestras de audio suelen estar cuantizadas con 16 bits. Para algunos algoritmos de gráficos de 3D es común emplear 32 bits para los tipos de datos básicos. Para posibilitar le procesamiento paralelo con estos tamaños de datos, en MMX se definen tres nuevos tipos de datos. Tienen una longitud de 64 bits, y constan de varios campos de datos más pequeños, cada uno de los cuales contiene un entero de coma fija. Estos tipos de datos son los siguientes: • • • Byte empaquetado: Ocho bytes en una cantidad de 64 bits. Palabra empaquetada: Cuatro palabras de 16 bits empaquetadas en 64 bits. Palabra doble empaquetada: Dos palabras dobles de 32 bits empaquetadas en 64 bits. [Stallings, 2000] 4.- En el siguiente ejemplo se muestra el uso de la instrucción PADDB de la tecnología MMX disponible en el Pentium II: Ejemplo 6.1: Suma con saturación mediante el uso de la instrucción PADDB. La instrucción PADDB toma como operando un byte empaquetado, y realiza en paralelo sumas con cada posición de byte para producir un byte empaquetado de salida. Una característica inusual que presenta el conjunto de instrucciones MMX es la introducción de la aritmética de saturación. Con la aritmética sin signo ordinaria, cuando una operación produce un desbordamiento (es decir, se produce una acarreo en la posición del bit mas significativa) el bit se trunca. Considere, por ejemplo las dos palabras en hexadecimal, F000H y 3000H. Su suma se expresaría como: F000H = +3000H = 1111 0000 0000 0000 0011 0000 0000 0000 1 0010 0000 0000 0000 = 2000H Acarreo 81 Si los dos números representaban intensidad de imagen, el resultado de la suma hace que la combinación de zonas sombreadas oscuras aparezca como más clara. Esto no es lo que se pretende normalmente. Mediante la aritmética con saturación, cuando la suma produce un desbordamiento, o la resta produce un desbordamiento negativo, el resultado se fija respectivamente al mayor o al menor valor representable. Para el ejemplo dado, la aritmética con saturación daría como resultado: F000H = +3000H = 1111 0000 0000 0000 0011 0000 0000 0000 1 0010 0000 0000 0000 = 2000H Acarreo 1111 1111 1111 1111 = FFFFH Suma con saturación 5.- En el ejemplo 6.2 tomado de [Stallings, 2000], se muestra el uso de las instrucciones MMX en una función típica de video. Ejemplo 6.2: Composición de una imagen en una función típica de vídeo mediante el uso de la tecnología MMX. Una función típica de vídeo es el efecto de desvanecimiento o extinción progresiva (fade-out) y reaparición (fade-in), mediante el cual una imagen A se deshace y convierte gradualmente en otra B. Las dos imágenes se combinan mediante una media ponderada: Pixel_resultado = Pixel_A x fade + Pixel_B x (1 – fade) Este cálculo se efectúa para cada posición de punto de imagen en A y B. Si se produce una secuencia de video mientras fade está cambiando progresivamente desde 1 a 0 (con una escala ajustada a un entero de 8 bits), el resultado es una transformación paulatina de la imagen A en la imagen B. La figura 6.1 muestra para un conjunto de puntos de imagen, la secuencia de pasos necesaria. Las componentes de pixel de 8 bits son transformadas en elementos de 16 bits para adaptarlas al tamaño de las multiplicaciones MMX de 16 bits. 82 Alpha Alpha Azul Azul Verde Verde Rojo Rojo Imagen A Imagen B Ar3 1. Desempaquetar bytes de componentes de pixel rojo de las imágenes A y B Ar3 Ar2 Ar2 Ar1 Ar1 Ar0 Br3 Ar0 Br3 Br2 Br2 Br1 Br1 Sustracción 2. Restar la imagen B de la imagen A r3 r2 r1 r0 X X X X fade fade fade fade 3.Multiplicar el resultado por el valor de fade fade x r3 4.Sumar los pixels fade x r2 + + Br3 Br2 fade x r1 + + Br1 Br0 fade x r0 de la imagen B 5.Volver a empaquetar en bytes los nuevos píxels compuestos nuevor3 nuevor2 nuevor1 r3 r2 nuevor0 r1 r0 Figura 6.1 Composición de imagen en una representación de planos de colores Br0 Br0 83 A continuación se presenta el código MMX que ejecuta las operaciones antes indicadas: PXOR MOVQ MM7, MM7 MM3, fad_val MOVD MM0, imagenA MOVD MM1, imagenB PUNPCKBLW PUNPCKBLW PSUBW PMULHW MM0, MM7 MM1, MM7 MM0, MM1 MM0, MM3 PADDDW PACKUSWB MM0, MM1 MM0, MM7 ; poner a cero MM7 ; cargar el valor de fade replicado 4 veces ; cargar las componentes de rojo de 4 pixels de la imagen A ; cargar las componentes de rojo de 4 pixels de la imagen B ; desempaquetar a 16 bits 4 pixels ; desempaquetar a 16 bits 4 pixels ; restar la imagen B de la imagen A ; multiplicar los valores de la resta por el valor de fade ; sumar el resultado a la imagen B ; empaquetar en bytes los resultados de 16 bits Ejercicios propuestos 1.- La siguiente línea corresponde a una sección de un programa escrito para ser ejecutado por el coprocesador aritmético: FST DATA Analice la sección del programa dado y describa cómo la ejecuta el coprocesador. Asuma que DATA está definida como una localidad de memoria de 64 bits. 2.- Describa cómo ocurre la saturación con signo, si las cantidades a sumar son de un byte. Consulta en otros libros [Stallings 2000] Destaca las mejoras del diseño de microprocesadores tomando como ejemplos el microprocesador Pentium II y el PowerPC. 84 Ejercicios de Autoevaluación 1.- El siguiente conjunto de instrucciones, ha sido extraído de un programa desarrollado para ser ejecutado por el coprocesador aritmético: .MODEL SMALL . . . RAD .DD 2.34 . . FLD RAD . . . Analice la sección del programa dado y describa que función realiza la instrucción FLD RAD. 2.- A continuación se presenta la sección de un programa que emplea instrucciones MMX, tales como: PADDB MM1, MM2 Para la instrucción dada, responda lo siguiente: • • ¿Qué tipo de operación permite realizar? Describa qué función realiza esta instrucción. Respuesta a los Ejercicios de Autoevaluación 1.- En la sección del programa dado, la instrucción FLD RD, carga el valor almacenado en RAD en ST. 2.- Solución: • • La instrucción permite realizar la operación aritmética de la suma. Esta instrucción suma el contenido completo de 64 bits del registro MM2 al contenido del registro MM1, byte por byte. El resultado es ubicado en MM1.