Document

Anuncio

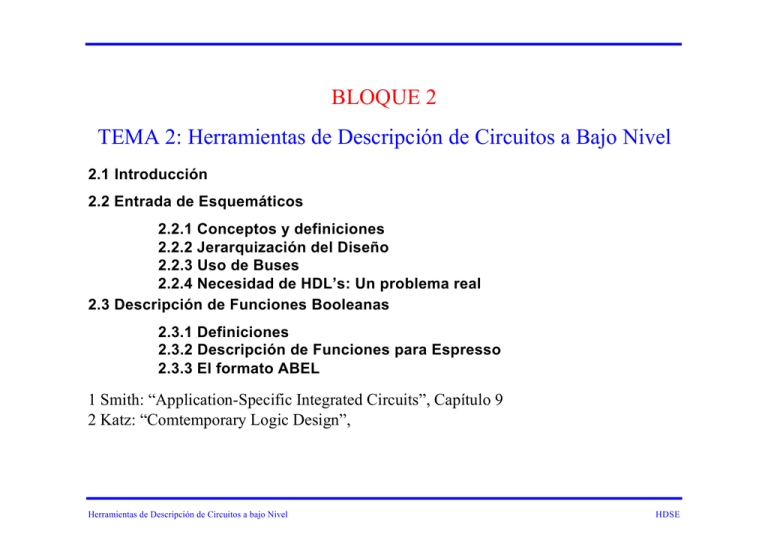

BLOQUE 2

TEMA 2: Herramientas de Descripción de Circuitos a Bajo Nivel

2.1 Introducción

2.2 Entrada de Esquemáticos

2.2.1 Conceptos y definiciones

2.2.2 Jerarquización del Diseño

2.2.3 Uso de Buses

2.2.4 Necesidad de HDL’s: Un problema real

2.3 Descripción de Funciones Booleanas

2.3.1 Definiciones

2.3.2 Descripción de Funciones para Espresso

2.3.3 El formato ABEL

1 Smith: “Application-Specific Integrated Circuits”, Capítulo 9

2 Katz: “Comtemporary Logic Design”,

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

INTRODUCCIÖN

Especificación

librerías

HDL

captura de

esquemas

síntesis

netlist

-------------------

El propósito de la Entrada de Diseño es

describir el circuito a una serie de herramientas de automatización y validación

-------------------

netlist: versión ASCII o binaria de una

descripción estructural de un circuito

La entrada de diseño puede ser:

- una vista esquemático del sistema

- lenguajes de descripción de hardware (HDL)

generan directamente el netlist mediante el uso de herramientas de síntesis.

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ENTRADA DE ESQUEMÁTICOS

ESQUEMÁTICO

Captura de

Esquemas

--------------------------------------------------------------------------------------------------------------------------------------------

NETLIST

El esquemático es un dibujo donde se muestran

los componentes del diseño asi como sus conexiones (contiene toda la información necesaria para describir el sistema)

Un dibujo no significa nada para las herramientas de diseño, se necesita una

herramienta (captura de esquemas) que transforme el esquemático en un fichero ASCII o una versión binaría del mismo

A este fichero se le llama netlist, y lleva la misma información que el esquemático

en la forma adecuada para la herramienta de diseño

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ENTRADA DE ESQUEMÁTICOS

Objetos de un esquématico i

Los componentes se eligen de una librería de celdas

módulo

celda primitiva

instancia, nombre de instancia

símbolo, símbolo generado

cable (wire, net, nudo)

pin

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ENTRADA DE ESQUEMÁTICOS

Objetos de un esquématico ii

Conexión entre “wires” (dot o solder dot),

conexión por nombre, nodos globales

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ENTRADA DE ESQUEMÁTICOS

Jerarquización de Diseño i

generación de símbolos

esquematico (padre)

subesquemático (hijo, niño)

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ENTRADA DE ESQUEMÁTICOS

Jerarquización de Diseño iii

esquemático plano (a), esquemáticos jerárquicos (b), (c), (d)

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ENTRADA DE ESQUEMÁTICOS

BUSES

BUS: “wire” especial que lleva información sobre más de una señal

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ENTRADA DE ESQUEMÁTICOS

a En general una herramienta de “captura de esquemas” permite

P editar esquemáticos

colocar las componentes y conectarlas

asignar propiedades o atributos a las instancias

dar nombres a instancias y nodos

P generar símbolos para esquemáticos

P editar símbolos: dibujar símbolos a medida

P chequear (analizar) esquemáticos: identificar errores simples

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ENTRADA DE ESQUEMÁTICOS

Necesidad de HDLs

aDificultad de introducir cambios una vez concluido

el esquemático y generado su símbolo

EJEMPLO: Incorporar una señal adicional de reset a nuestro circuito

Nos puede obligar a retocar la posicion de todas las celdas instanciadas en el esquemático

Nos obliga a hacer un símbolo nuevo

Si el bloque es usado en un diseño jerarquizado las celdas a modificar son todas aquellas que usen la celda que ha sido modificada

Ejemplo catastrófico: Incluir una señal adicional de SET en unos

biestables usados como bloques básicos de un micro-controlador

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

HDLs DE BAJO NIVEL

a Los HDLs nos permiten la generación del netlist de un circuito sin

necesidad de pasar por la vista esquemático a partir de una descripción

comportamiento del mismo y haciendo uso de Herramientas de Síntesis

Ejemplo: Descripción de un MUX de 8b en HDL (VHDL).

entity Mux8 is

generic (TPD: TIME:= 1ns);

port (A, B: in BIT_VECTOR (7 downto 0);

Sel : in BIT:= ‘0’ ; Y : out BIT_VECTOR (7 downto 0));

end;

architecture Behave of Mux8 is

begin

Y <= A after TPD when Sel = ‘1’ else B after TPD;

end;

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

Descripción de Funciones Booleanas

HDLs DE BAJO NIVEL

Definiciones:

Teoremas:

#1: Mintérmino Término producto fundamental

= xy + xy = m 11 + m 00

#1: Una función lógica está descrita de

= ∑ m ( 0, 3 ) . forma unívoca si se especifican su ONSET, OFF-SET y DC-SET.

#2: ON-SET Conjunto de mintérminos

para los que la función es “1”.

#3: OFF-SET Conjunto de mintérminos para los que la función es “0”.

#2: ON-SET, OFF-SET y DC-SET no

pueden tener ningún mintérmino en

común.

#2: ON-SET, OFF-SET y DC-SET cubren por completo el espacio en que

#4: DC-SET Conjunto de mintérminos

está definida la función.

para los que la función está inespecificada “-”.

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

Descripción de Funciones Lógicas para ESPRESSO

.i 4

.o 1

.type f

.p 5

1000 1

0101 1

0000 1

0010 1

1101 1

.e

HDLs DE BAJO NIVEL

#1 Dando el ON-SET de manera que DC-SET= ∅ y

OFF-SET=not(ON-SET)

a).type f (en el fichero de entrada).

b)con el modificador -f en linea de com.

∪ y DC-SET; OFF-SET=not(ON#2 Dando el ON-SET

SET ∪ DC-SET)

a).type fd (en el fichero de entrada).

b)con el modificador -fd en linea de com.

#3 Dando el ON-SET y OFF-SET; DC-SET=not(ONSET ∪ OFF-SET)

a).type fr (en el fichero de entrada)

b)con el modificador -fr en linea de com.

#4 Dando el ON-SET, DC-SET y OFF-SET

a).type fdr (en el fichero de entrada)

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

Descripción de Funciones Lógicas para ESPRESSO

Comando

.i [d]

.o [d]

.type [f, fd, fr, fdr]

.phase [s] [s]....[s]

.p [d]

.e (.end)

#

HDLs DE BAJO NIVEL

Significado

Número de Variables de Entrada

Número de Variables de Salida

Tipo de Función de Entrada

Cadena con tantos 1 y 0 como funciones de salida

que define la polaridad a adoptar durante la minimización, 1 para el ON-SET y 0 para el OFF-SET

Número de Términos producto en la función.

Fin del fichero

Comienzo de un comentario.

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

Descripción de Funciones Lógicas para ESPRESSO

HDLs DE BAJO NIVEL

Funciones Multisalida

lista de cubos que tienen parte de entrada y parte de salida

La parte de entrada de cada

cubo representa un término producto mientras que cada posición del cubo es una variable.

0

1

-

El literal aparece complementado en el TP

El literal aparece tal cual en

el TP

El literal no aparece en el TP

Herramientas de Descripción de Circuitos a bajo Nivel

La parte de salida de cada cubo

se interpreta según el tipo de función descrita.

f

1 Pertene al ONfd

1 Pertenece al ON-SET

- Pertenece al DC-SET

fr

1 Pertenece al ON-SET

0 Pertenece al OFF-SET

fd

1 Pertenece al ON-SET

0 Pertenece al OFF-SET

- Pertenece al DC-SET

HDSE

Descripción de Funciones Lógicas para ESPRESSO

#Sumador de números de 2 bits

#sin entrada de acarreo

.i 4

.o 3

.type fr

.par 2 (1 3) (2 4)

.phase 011

00 00 000

00 01 001

00 10 010

00 11 011

01 00 001

01 01 010

01 10 011

01 11 100

10 00 010

10 01 011

10 10 100

10 11 101

11 00 011

11 01 100

11 10 101

11 11 110

.e

Herramientas de Descripción de Circuitos a bajo Nivel

HDLs DE BAJO NIVEL

Esta línea es un comentario

Esta línea es un comentario

Cuatro entradas

Tres salidas

Damos ON-SET y OFF-SET

Creamos 2 pares de variables (1er y 2o número)

La salida más significativa tiene polaridad negativa.

0+0=0

0+1=1

0+2=2

0+3=3

1+0=1

1+1=2

1+2=3

1+3=4

2+0=2

2+1=3

2+2=4

2+3=5

3+0=3

3+1=4

3+2=5

3+3=6

Fin del fichero

HDSE

Descripción de Funciones Lógicas para ESPRESSO

HDLs DE BAJO NIVEL

EJEMPLO DE MINIMIZACIÓN USANDO ESPRESSO:

A

B

C

F1 F2 F3

0

0

0

1

0

0

0

0

1

0

1

1

0

1

0

1

0

0

0

1

1

1

0

1

1

0

0

1

0

0

1

0

1

1

1

1

1

1

0

1

0

1

1

1

1

1

0

1

INPUT (6 términos):

F1 = A + B + !C

F2 = !BC

F3 = C + AB

Salida de ESPRESSO:

.i 3

.o 3

.p 5

1-- 100

11- 001

--0 100

-01 011

-11 101

.e

OUTPUT (5 términos):

F1 = A + BC + !C

F2 = !BC

F3 = BC + AB+!BC

ESPRESSO reduce los seis términos originales a estos cinco

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

ABEL: Advanced Boolean Equation Language

-Permite entrar a una herramienta de diseño la descripción del

comportamiento de un circuito lógico.

-Es un lenguaje de descripción de hardware (HDL) industrial

desarrollado por “Data I/O Corporation” para SPLDs.

-ABEL es mucho más simple que VHDL ó Verilog pero también es capaz

de describir sistemas de gran complejidad.

-ABEL puede usarse para describir el comportamiento de un

sistema en una variedad de formas, incluyendo ecuaciones

lógicas, tablas de verdad, y diagramas de estado, usando sentencias

tipo C.

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

ESTRUCTURA BÁSICA DE UN FICHERO ABEL

Un fichero fuente de ABEL contiene los siguientes elementos:

1-Cabecera: incluye “Module”, “Options” y “Title”.

2-Declaraciones (Declarations): “Pin”, “Constant”, “Node”, “Sets”,

“States”y “Library”.

3-Descripciones Lógicas: “Equations”, “Truth-table” y “State_diagram”.

4-Vectores de Test: “Test_Vectors”.

5-Final: “End”.

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

“Template” típico:

module nombre del módulo

[title string]

[deviceID device tipo_dispositivo;]

pin declarations

other declarations

equations

ecuaciones

[Test_Vectors]

Vectores de test

end nombre del módulo

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

Ejemplo “half adder”:

Modulo

module mi_primer_circuito;

A

SUM

mi_primer_circuito Carry_out

B

title ‘ee200 assignment 1‘

EE200XY

device ‘XC4003E‘;

“pines de entrada

A

B

SUM

Carry_out

0

0

0

0

0

1

1

0

“pines de salida

1

0

1

0

Sum, Carry_out pin 15,18 istype ‘com‘;

1

1

0

1

A,B pin 3, 5;

equations

SUM=(A&!B)#(!A&B);

Carry_out=A&B;

end mi_primer_circuito;

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

Sentencias más importantes

-Module: todos y cada uno de los ficheros fuentes comienza con una sentencia module seguida

del nombre del módulo (identificador). Ficheros fuentes muy largos a menudo están compuestos

por múltiples módulos con su propio título, ecuaciones y sentencias.

-Title: es opcional y puede usarse para identificar el proyecto. El nombre del título debe estar

entre comillas simples. La línea del título es ignorada por el compilador pero se maneja para

documentación.

-String: es una serie de caracteres ASCII encerrados por comas simples. Las “strings” se usan

para TITLE, sentencias de OPTIONS, y en declaraciones de pin, node y atributos.

-Device: esta declaración es opcional y asocia un identificador del dispositivo con un dispositivo

de lógica programable específico. La sentencia device debe finalizar con punto y coma. Cuando

estés usando la herramienta de CAD Xilinx para compilar el diseño, es mejor no poner esta

sentencia en el fichero fuente para mantener tu diseño independiente del dispositivo. Cuando tu

crees un proyecto nuevo en Xilinx especificarás el tipo de dispositivo (este puede cambiarse

también en la ventana de Project Manager usando el botón de Project Information). El formato es

device_id device ‘dispositivo_real‘;

como sigue:

EJEMPLO: Mi_Decodificador device ‘XC4003E‘;

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

-Comments: los comentarios pueden insertarse en cualquier lugar dentro del fichero y

comienzan con una comilla doble y finaliza con otra o al final de la línea, si esta llega primero.

-Pin: las declaraciones de pines que uno da al compilador usando nombres simbólicos, se

asocian con pines del dispositivo externo. El formato es:

[!] identificador_pin pin [#pin] [istype ‘atributos‘];

Se puede identificar más de un pin por línea:

[!] pin_id,pin_id,pin_id pin [#pin,#pin,#pin] [istype ‘atributos‘];

EJEMPLOS:

pin 2,3,4;

OUT1 pin 9 istype ‘reg‘;

ENABLE pin;

!Chip_sect pin 12 istype ‘com‘;

!S0..!S6 pin istype ‘com‘;

IN1,IN2,A1

El comando ! indica que la señal está activa en bajo (estará invertida). El comando

istype es un asignamiento de atributo opcional para un pin. ‘com‘ indica que la salida es una señal

combinacional y ‘reg‘ indica que es una señal registrada con un flip-flop. Este comando es sólo para

pines de salida.

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

-Node: las declaraciones de node tienen el mismo formato que las de pin. Definen señales

internas que no se conectan a pines externos. Ejemplo: tmp1 node [istype ‘com‘];

-Otras declaraciones: nos permiten definir constantes, sets, macros y expresiones para

simplificar el programa. Por ejemplo una declaración de constante tiene el siguiente formato:

id = expr;

Ejemplos:

A = 21;

C = 2*7;

ADDR = [1,0,1,1];

LARGE = B&C;

D = [D3,D2,D1,D0];

D = [D3..D0]; “notación vectorial (siempre que usemos D en una ecuación nos referiremos

al vector [D3,D2,D1,D0] “

-Números: Pueden introducirse en diferentes bases: binaria, octal, decimal y hexadecimal.

La base por defecto es la decimal. Para especificar la base se han de usar los siguientes símbolos:

NOMBRE

BASE

Binaria

Octal

Decimal

Hexadecimal

BASE

2

8

10

16

SÍMBOLO

^b

^o

^d (defecto)

^h

Herramientas de Descripción de Circuitos a bajo Nivel

EJEMPLOS: ABEL

35

^h35

^b101

Valor Decimal

35

53

5

La base por defecto se cambia con el directivo “Radix”.

HDSE

ABEL

HDLs DE BAJO NIVEL

-Directivos: permite la manipulación avanzada del fichero fuente y del proceso. Pueden

ubicarse en cualquier lugar dentro del código:

@ALTERNATE: permiten un conjunto alternativo de operadores lógicos: AND (*), OR (+), NOT (/).

Los operadores alternativos se mantienen efectivos hasta que pongamos el directivo @STANDARD

o lleguemos al final del módulo.

@RADIX expresión: cambia la base por defecto. La base por defecto es la decimal (10). La nueva base

especificada se mantiene vigente hasta que usemos otro directivo radix o hasta llegar al final del

módulo. Ejemplo: @radix 2; “cambia la base por defecto a la binaria

@radix 1010; “regresa desde binaria a decimal

-Sets: un set es un conjunto de señales o constantes que se usa para referirnos a un grupo de

señales por un único nombre. Es muy util para simplificar expresiones lógicas. Cualquier operación

que se aplique a un set se aplica a cada elemento de este.

Un set es una lista de constantes o señales separadas por comas o por el operador .., siempre entre []:

EJEMPLOS:

[D0,D1,D2,D3,D4,D5]

[D0..D5]

[D7..D15]

[b1,b2,a0..a3]

[!S7..!S0] “señales activas en bajo

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

-Accediendo a un set: podemos acceder a los elementos dentro de un set. Se usan valores

numéricos para indicar el índice del set. El número se refiere a la posición del bit en el set

comenzando por cero para el bit menos significativo del set:

D1=[D15..D0]; “declaración de set

X2=[X3..X0]; “declaración de set

X2:=D1[3..0]; “hace X2 igual a [D3,D2,D1,D0]

X2:=D1[7..4]; “hace X2 igual a [D7,D6,D5,D4]

-Operaciones con sets: la mayoría de las operaciones se pueden aplicar a un set y se realizan

sobre cada elemento de este de acuerdo a las reglas del algebra Booleana:

Ejemplo1:

Ejemplo2:

Signal=[D2,D1,D0]; “declaración del set Signal

[A,B]=C&D;

Signal=[1,0,1]&[0,1,1]; “Signal es igual a [0,0,1]

“es equivalente a dos sentencias

A=C&D;

B=C&D;

Ejemplo3:

[A1,B1]=[D1,D2]&[C3,C2];

Ejemplo4:

“es equivalente a

X&[A,B,C];

[A1,B1]=[D1&C3,D2&C2];

“es equivalente a

“o equivalente a

[X&A,X&B,X&C]

A1=D1&C3;

“sin embargo consideramos la siguiente expresión

A2=D2&C2;

2&[A,B,C];

“tenemos que convertir el número “2” a representación binaria (010)

[0&A,1&B,0&C];

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

Operadores de Relación

Operadores Lógicos

Operador

(defecto)

Descripción

Operador

Alternativo

&

AND

*

#

OR

+

!

NOT

/

$

XOR

:*:

Operadores Aritméticos

Operador

Descripción

a-b

Resta

a+b

Suma

>>

Desplaz. izda.

<<

Desplaz. dcha.

Herramientas de Descripción de Circuitos a bajo Nivel

Operador

Descripción

==

Igual

!=

Distinto

<

Menor

>

Mayor

<=

Menor o igual

>=

Mayor o igual

HDSE

ABEL

HDLs DE BAJO NIVEL

DESCRIPCIÓN LÓGICA

Un diseño lógico se puede describir de varias formas:

-Ecuaciones.

-Tabla de Verdad.

-Descripción de Estado.

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

Método I: Usando Ecuaciones

-Equations: usa la clave equations para comenzar las descripciones lógicas.

Equations especifica expresiones lógicas usando los operadores antes definidos o la sentencia

condicional “When-Then-Else”.

La sentencia “When-Then-Else” se usa en equations para describir una función lógica. Su formato es:

When condición THEN elemento=espresión;

When condición THEN ecuación;

Ejemplo de ecuaciones:

SUM = (A&!B)#(!A&B);

A0 := EN&!D1&D3&!D7;

WHEN (A==B) THEN D1_out=A1;

ELSE WHEN (A==C) THEN D1_out=A0;

WHEN (A>B) THEN {X1:=D1; X2:=D2;}

when (a != b) then

c:= mi_entrada ;

else

c:= mi_nodo_reg ;

c.clk = mi_reloj ;

Herramientas de Descripción de Circuitos a bajo Nivel

El signo = se usa para asignaciones combinacionales

El signo := se usa para asignaciones secuenciales.

Ejemplo:

Equations

mi_nudo_registro := mi_entrada

;

HDSE

ABEL

Método II: Usando Tablas

Están limitadas por la palabra

clave TRUTH_TABLE

El signo -> se usa para asignaciones combinacionales

El signo :> se usa para asignaciones secuenciales.

Ejemplo1:

TRUTH_TABLE

([control] -> [salida])

[0]

-> [dato_A] ;

[1]

-> [dato_B] ;

Herramientas de Descripción de Circuitos a bajo Nivel

HDLs DE BAJO NIVEL

Ejemplo2: Semi-Sumador

TRUTH_TABLE ([A,B] -> [Sum, Carry_out])

[0,0]

-> [0,0] ;

[0,1]

-> [1,0] ;

[1,0]

-> [1,0] ;

[1,1]

-> [0,1] ;

Ejemplo3: Semi-Sumador

“Definimos un set

IN=[A,B]; OUT=[Sum.Carry_out]:

TRUTH_TABLE (IN -> OUT)

0

-> 0 ;

1

-> 2;

2

-> 2;

3

-> 1;

HDSE

ABEL

Ejemplo5: Las tablas de verdad se pueden usar

tambien para describir maquinas secuenciales:

Module CNT3;

CLOCK pin; “señal de entrada

RESET pin; “señal de entrada

OUT pin istype ‘com‘; “señal de salida (combinacional) (se activa en al estado de cuenta 111)”

QC,QB,QA pin istype ‘reg‘; “señal de salida (tipo

registro) (salidas de los flip-flops) (estado de cuenta)”

[QC,QB,QA].CLK = CLOCK; “CLOCK es el reloj

de de los FF”

[QC,QB,QA].AR= RESET; “RESET es un reset

asíncrono (en alto el contador se resetea al estado 000)”

TRUTH_TABLE

( [QC,QB,QA] :> [QC,QB,QA] -> OUT )

[0 0 0] :> [0 0 1] -> 0 ;

[0 0 1] :> [0 1 0] -> 0 ;

[0 1 0] :> [0 1 1] -> 0 ;

[0 1 1] :> [1 0 0] -> 0 ;

[1 0 0] :> [1 0 1] -> 0 ;

[1 0 1] :> [1 1 0] -> 0 ;

[1 1 0] :> [1 1 1] -> 0 ;

[1 1 1] :> [0 0 0] ->

1;

end CNT3;

Herramientas de Descripción de Circuitos a bajo Nivel

HDLs DE BAJO NIVEL

Ejemplo4: XOR con dos entradas y un enable

“Se ilustra el uso de inespecificaciones

(.X.)

IN=[A,B]; OUT=[Sum.Carry_out]:

TRUTH_TABLE ([EN,A,B] -> OUT)

[0,.X.,.X.]

-> .X. ;

[1,0,0]

-> 0;

Sintaxis

TRUTH_TABLE (in_ids -> out_ids)

entradas

-> salidas;

TRUTH_TABLE (in_ids :> reg_ids)

entradas

:> salidas_reg;

TRUTH_TABLE

>out_ids)

(in_ids

:>

reg_ids

HDSE

-

ABEL

HDLs DE BAJO NIVEL

Método III: Usando Diagramas de Estado

Están

limitadas

por

la

palabra

clave

Declaración de los bits de estado (se declaran nom-

Sentencias condicionales:

-”IF-THEN-ELSE

-”GOTO”

-”CASE”

para definir el próximo estado

seguidas por un ”WITH”

opcional

bres de estados simbólicos en la sección Declaration).

rojo pin istype ‘reg’ ;

amarillo pin istype ‘reg’ ;

Ejemplo1:

“En la sección Declarations definimos primero los registros de estado “

Declaración de nombre y asignamiento de esta- SREG=[Q1,Q0]; “defininción de los

dos

registros de estado”

luces = [rojo, amarillo, verde] ;

S0=[0,0];

cruzar = [0,0,1];

S1=[1,1];

Definir el reloj para el conjunto

[rojo, amarillo, verde].clk = mi_reloj ;

State_diagram SREG

state S0: OUT1=1;

Definir las transiciones de estados.

if A then S1

else S0;

state S1: OUT2=1;

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

Formato ABEL: Extensiones punto.

.Q ó .FB

.AP

S

.D / T

D/T

nombre_señal.ext

Q

.CLK

Se usan las extensiones punto para

describir el circuito con más precisión. Las extensiones son muy

útiles y proporcionan un mecanismo

para referirnos especificamente a

señales internas y nodos asociados

a señales primarias.

Sintaxis:

.OE

R

.AR

Herramientas de Descripción de Circuitos a bajo Nivel

Algunas Extensiones Punto son de

propósito general (independientes

de la arquitectura o pin-to-pin) y

pueden usarse con una gran variedad de arquitecturas de dispositivos.

Otras Extensiones Punto se usan

para clases específicas de arquitecturas de dispositivos y se llaman

“detalladas”.

HDSE

ABEL

HDLs DE BAJO NIVEL

Comando

Ejemplo

Comentario

Module

module Mi_Módulo

Un diseño puede incluir muchos módulos

Title

title ‘El que queramos’

No es más que un string (importante !! usar las quotes)

Device

mi_dispositivo device ‘p102’ ;

mi_dispositivo es un ID para documentación.

Comment

“los comentarios van entre dobles comillas ”

“salvo si acaban en el fin de la línea

El fin de una línea significa el fin de un comentario, por lo que se puede

prescindir de cerrarlo si llegan hasta el fin de la línea.

@alternate

@alternate “ uso de símbolos alternativos

Operador

AND

OR

NOT

XOR

XNOR

Pin declaration

mi_reloj pin ;

Define mi_reloj como un pin

Equations

equations

out = in1 # in2 ;

Define lógica combinacional

out es el resultado de la Or(in1,in2)

Assignments

mi_salida = / mi_entrada ;

mi_salida es la inversa de mi_entrada

Signal Sets

D = [D0, D1, D2, D4] ;

Esto es un bus para ABEL

Suffix

mi_salida.re = CLR ;

mi_entrada.pr = PRE ;

CLR es un reset para el registro mi_salida

PRE es un preset para el registro mi_entrada

Addition

Count = [D0, D1, D2] ;

Count := Count + 1 ;

No se puede usar @alternate si se usa + para sumar

Enable

ENABLE IO3 = IO2 ;

IO3 = mi_entrada ;

Habilita el uso en un pin tipo tri-estado

Constants

k = [1,0,1] ;

K vale 5

Relational

D == K5 ;

D es igual a K5 (== != > < <= >=)

End

end Mi_Módulo

Se acabó

Herramientas de Descripción de Circuitos a bajo Nivel

Símbolo Alternativo

*

+

/

:+:

:*:

Por Defecto

&

#

!

$

!$

HDSE

ABEL

HDLs DE BAJO NIVEL

Formato ABEL: Vectores de Test

Está limitada por la palabra

clave TEST_VECTORS

Permiten realizar un Test funcional de la descripción lógica.

Los vectores se escriben utilizando el formato de las Tabla de

Verdad.

Señales especiales definidas

Características:

-Los vectores de Test son opcionales.

-Proporcionan un mecanismo para verificar la

operación correcta del circuito.

-Especifican la operación lógica esperada del

dispositivo lógico dando explicitamente las salidas como función de las entradas.

Sintaxis:

Test_vectors [nota]

.C. Pulso positivo

(input -> output)

.Z. Señal Triestado

[in_valores -> out_valores]

.

.

.

.X. Don’t care

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

Ejemplo 1

MODULE ejemplo1

mi_reloj pin; “Mi reloj es un pin de entrada

x7..x0 node istype ‘reg’ ; “x7,6,5,4,3,2,1 son nudos tipo registro

total7..total0 pin istype ‘reg’ ; “total7,6,5,4,3,2,1 son salidas tipo registro

x = [x7..x0]; “Genero un grupo x conteniendo todas las x i

total = [total7..total0]; “Genero un grupo total conteniendo todas las totali

equations “Empieza el módulo de ecuaciones

[x,total].clk = mi_reloj ; “Se asigna el reloj para los grupos x y total

x := x+1 ; “Se implementa un contador para x

total := total + x ; “Se acumula

test_vectors ([mi_reloj] -> [x, total]) “Se define un módulo de test

[.c.] -> [1,0]; “Primer ciclo, acumulado 0

[.c.] -> [2,1]; “Segundo ciclo, acumulado 1

[.c.] -> [3,3]; “Tercer ciclo, acumulado 1+2=3

[.c.] -> [4,6]; “Cuarto ciclo, acumulado 1+2+3=6

[.c.] -> [5,10]; “Quinto ciclo, acumulado 1+2+3+4=10

[.c.] -> [6,15]; “Sexto ciclo, acumulado 1+2+3+4+5=15

[.c.] -> [7,21]; “Séptimo ciclo, acumulado 1+2+3+4+5+6=21

[.c.] -> [8,28]; “...

[.c.] -> [9,36]; “...

END

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

Ejemplo 2

MODULE controlador

clk pin; “clk es un reloj de entrada

reset pin; “reset es un pin de entrada

count4..count0 node istype ‘reg’ ; “count 4,3,2,1 son nudos tipo registro

contador= [count4..count0]; “Genero un grupo contador

rojo pin istype ‘reg’ ; “ rojo es una salida de registro

amarillo pin istype ‘reg’ ; “ amarillo es una salida de registro

verde pin istype ‘reg’ ; “ verde es una salida de registro

luces = [rojo, amarillo, verde ] ; “ Defino el grupo de luces

pasar = [0 , 0 , 1] ; “ Asignamiento de estados

cuidado = [0 , 1, 0] ; “ Asignamiento de estados

parar = [1 , 0 , 0] ; “ Asignamiento de estados

equations “Empieza el módulo de ecuaciones

verde.ap =reset ; “ cuando se resetea se hace un set al verde

rojo.ar =reset ; “ un reset al rojo

amarillo.ar =reset ; “ y un reset al amarillo (Se parte del estado pasar)

contador.ar =reset ; “Se resetea la cuenta.

contador.clk =clk ; “ Se define el reloj del grupo contador

luces.clk = clk ; “ Defino el grupo de luces

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE

ABEL

HDLs DE BAJO NIVEL

Ejemplo 2 (cont)

State_Diagram luces

state pasar :

IF (contador < 30) then pasar with

contador := contador + 1 ;

ELSE goto cuidado with

contador := contador + 1 ;

state cuidado :

IF (contador != 0 ) then cuidado with

contador := contador + 1 ;

ELSE goto parar with

contador := contador + 1 ;

state parar:

IF (contador < 30) then parar with

contador := contador + 1 ;

ELSE goto pasar with

contador := 1 ;

END

Herramientas de Descripción de Circuitos a bajo Nivel

HDSE