descargar

Anuncio

Arquitecturas vectoriales,

SIMD y extensiones

multimedia

William Stallings, Organización y Arquitectura de

Computadores, 5ta. ed., Capítulo 16: Procesamiento Paralelo.

Andrew S. Tanenbaum, Organización de Computadoras 4ta.

ed., Capítulo 8: Arquitecturas de computadoras paralelas.

Hesham El-Rewini & Mostafa Abd-El-Barr, Advanced

Computer Architecture and Parallel Processing. Willey.

Taxonomía de Flynn

Procesadores vectoriales

Definición

Implica un repertorio de instrucciones (ISA) con instrucciones que

operen sobre vectores (arreglos unidimensionales de datos), en

contraste con los procesadores escalares, que operan sólo sobre un

único elemento.

Explotación del paralelismo en los datos. No concurrencia.

El concepto está presente en diversas tecnologías.

Supercomputadoras de los 70s. Cray. UF segmentadas.

Array processors de los 90s. Connection Machines. Múltiples UF

simultámeas (SIMD).

Extensiones multimedia de los procesadores de propósitos generales. Desde el Pentium 1997.

Aceleradores gráficos o GPU (Graphics processing unit).

Procesadores vectoriales

Alternativas

Procesadores vectoriales

Supercomputadoras de los 70s

Se trata de procesadores con unidades vectoriales segmentadas,

además de unidades escalares. Cada unidad vectorial dispone de un

banco de registros vectoriales (cada uno con 64 o 128 words) y una

unidad funcional vectorial fuertemente segmentada. Dispone de

instrucciones escalares clásicas e instrucciones vectoriales (load,

store, alu, mixed). El usuario puede operar directamente sobre

vectores en assembler (hoy utilidad relativa).

CD Cyber 205

Cray

IBM 3090

Nec SX

Hitachi S8000

Fujitsu VP

Procesadores vectoriales

IBM 3090 con unidad vectorial

Unidad vectorial, compuesta por:

Unidades funcionales segmentadas

Registros vectoriales

Procesadores vectoriales

ISA

Dispone, además de registros de

m palabras, de algunos registros

especiales: VL (vector length,

l<m) y M (mask, m bits, opera si

1).

Ejemplo:

for(i=0;i<50;i++){

if(a[i]>0)

a[i] = a[i] + 1;

}

R0 <- A(0:49:1)

VL <- #50

M <- R0 > 0

WHERE(M) R0 <- R0 + 1

Arquitecturas SIMD

Single Instruction stream, Multiple Data stream

Constan de una única unidad de control y múltiples unidades

idénticas de procesamiento que realizan la misma instrucción al

unísono. Llamados también Array Processors.

Especializados en problemas numéricos que puedan expresarse

como matrices o vectores. Cada unidad de procesamiento consta de

una ALU y registros, y se utiliza para computar un elemento del

resultado (front-end von Neumann, más un array de procesadores

idénticos que realizan la misma instrucción).

Arquitecturas SIMD

Single Instruction stream, Multiple Data stream

Pueden utilizar memoria compartida o distribuida.

Ejemplo: ILLIAC IV (1970s), 64 procesadores

conectados en una grilla de 8x8. CM-2 (1990s)

de Connection Machines (RIP), 65536

procesadores conectados en hipercubo.

Arquitecturas SIMD

Single Instruction stream, Multiple Data stream

Explotación eficiente del paralelismo en los datos.

Ejemplo: ajuste de volumen de un strem de audio digital o ajuste de

contraste en una imagen (la misma operación se realiza sobre un

número muy grande de datos).

SIMD

Extensiones multimedia

En procesamiento de audio y video

deben manejarse arreglos grandes

de datos de 8 o 16 bits.

Gran potencial para SIMD.

Incorporan características propias

de los DSP.

La idea es utilizar registros de 64

bits para procesar al mismo tiempo

8 palabras de 8 bits, o cuatro de 16

(paralelismo SIMD a escala

reducida).

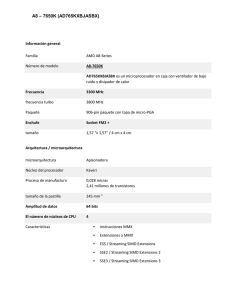

Pentium MMX y Pentium II: MultiMedia eXtension (enteros),

originario del i860. 57 instrucciones y 8 nuevos registros MM0-MM7

(son los mismos registros del stack de la unidad de punto flotante,

no simultáneos).

Extensiones multimedia (cont)

Ejecuta instrucciones entre las sub-palabras, por ejemplo suma o

MAC, utilizando aritmética de saturación, propio de los DSP. Existen

extensiones para enteros y para punto flotante.

Intel MMX, Pentium II (1997 enteros) -> AMD 3DNow! en K6-2 1999 (fp) -> Intel SSE,

Streaming SIMD Extension, en el Pentium III (fp) 1999 –> SSE2 en P4/Opteron 2001 ->

SSE3 P4/Athlon 2004 –> SSE3 Core2 2006, Advanced Digital Media Boost 128 bits/1c

Además VIS en UltraSPARC, MDMX para MIPS y MAX-2 para HP PA-RISC.

Extensiones multimedia (cont)

MIPS lanzó en 1996 MDMX (MIPS Digital Media Extensions).

32 nuevos registros de 64 bits (media registers), mapeados sobre los

de punto flotante, para ahorrar hardware; y un acumulador de

producto extendido de 192 bits.

Los media registers pueden almacenar dos nuevos tipos de datos:

octo byte (OB) y quad half (QH) que contienen 8 bytes (8-bit) y 4

media-palabra (16-bit) integers.

Variantes de las intrucciones existentes, incluyendo aritmética de

saturación.

Extensiones multimedia PF 128 bits

Nuevas extensiones multimedia

Streaming SIMD Extension 5 (SSE5)

FMA4 instruction set, fused multiply–add

Fused multiply accumulate (FMACxx) instructions (FMA4 extension: single rounding, four

operands d = a + b * c) Ver: https://www.pgroup.com/lit/articles/insider/v3n3a4.htm

Advanced Vector Extensions (AVX2), 256 bits

→ AVX-512