Práctica 3 - Departamento de Ingeniería Electrónica

Anuncio

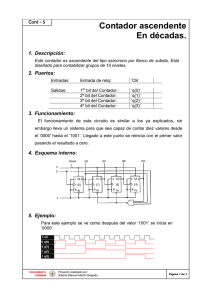

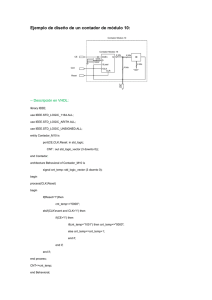

Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital Escuela Superior de Ingenieros Universidad de Sevilla Departamento de Ingeniería Electrónica Versión 1.2. 3 de Marzo de 2008 Práctica 3 LABORATORIO DE MICROELECTRÓNICA Jonathan N. Tombs Fernando Muñoz Chavero Miguel A. Aguirre Javier Nápoles Práctica 3. Receptor de una línea serie 1 Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital Práctica 3. Comunicación serie con la tarjeta S3 Este práctica es la tercera de un grupo de tres dedicada a entrenar al alumno con el entorno de trabajo Xilinx ISE 9.2 y la tarjeta Digilent S3. Se diseñarán un sistema de comunicaciones entre un ordenador personal y las tarjeta, basadas en la utilización de un enlace serie RS232. Los objetivos de la práctica son los siguientes: 1. Perfeccionar el entrenamiento con el entorno Xilinx ISE 9.2. 2. Faciltar un mecanismo de comunicaciones entre un PC y la tarjeta S3 que sirva para transferencia de información entre ambos sistemas. Práctica 3. Receptor de una línea serie 2 Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital 1. Objetivo propuesto • • Se trata de diseñar un enlace serie RS232 con una velocidad de transferencia y definición del enlace de comunicaciones fijo. Proveer de un mecanismo de transferencia de información entre la tarjeta y el usuario para posibles aplicaciones en los proyectos. 2. Enlace de Serie Un enlace serie es una comunicación asíncrona a una velocidad determinada. La comunicación se realiza diseñando una UART para la transmisión y para la recepción de mensajes. Las condiciones de diseño serán las siguientes: • 8 bits • Paridad par • 1 start y 2 de stop • 9600 baudios • Half‐duplex. No se permite envío y recepción simultáneos. Desde el PC utilizaremos la utilidad de Windows “hiperterminal”, que nos facilitará la transferencia a través del COM1. Una línea serie tiene dos líneas RX y TX, RX recibe la información y TX la envía. DataRec1 DataRec0 RECEPTOR Registro Byte RX Registro Byte Driver Displays DataOK StTrans TRANSMISOR DataRec1 TX Por otra parte, representaremos la información recibida en los displays de la placa. En el ejercicio de hoy almacenaremos cuatro valores en sendos registros de 8 bits, que forman una pequeña FIFO de dos bytes. A su vez estos registros se representan en el Práctica 3. Receptor de una línea serie 3 Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital display y luego se envían al PC por la línea de transmisión. En la consola hiperterminal se visualizarán los valores de la información retrasados un envío. Para realizar la práctica se utilizará el puerto RS232 de la placa, conectado al PC mediante un cable serie. La norma RS232 obliga a transmitir mediante tensiones de 0 a ‐15V. Se precisa, pues, de un chip que adapte dichas tensiones. En la figura se representa el esquema eléctrico de dicho puerto implementado en la placa S3. 3. Realización de la práctica Por razones didácticas seguiremos la evolución de la práctica de menor a mayor complejidad. Además se proporciona la parte del diseño relacionada con los drivers de los display, que pueden ser los mismos que se utilizaron en la práctica 1. Se comenzará realizando un transmisor que envíe un valor fijo al PC. 3.1 TRANSMISOR El transmisor es un circuito bastante sencillo, en el que la información transmitida por la línea TX tiene una configuración fija. En este caso se trata de una carga en paralelo y una salida en serie, para enviar 8 bits de información y a los cuales que hay que añadir el bit de start y bit proveniente del generador de paridad. La línea de transmisión está en estado ‘1’ en reposo. La transmisión se realizará a la velocidad de 9600 baudios. Práctica 3. Receptor de una línea serie 4 Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital Utilizaremos los siguientes elementos para realizar el tranmisor: • Contador de bits • Contados de baudios • Máquina de estados que controla la transmisión • Generador de paridad • Multiplexor de selector de bit. En esta práctica es muy aconsejable utilizar un contador genérico en el que se adapte su extensión y valor de saturación a cada una de las aplicaciones, con señal de habilitación (enable) y señal de reset síncrono. La línea serie se comporta según la figura adjunta: Start B0 B7 Paridad Stop Muestreo B0 es el bit menos significativo del Byte a transmitir, y el bit de paridad representa un valor que hace que el número de bits a 1 del byte, junto con el propio bit de paridad, sea par. Los bits de stop representan un tiempo de al menos dos bytes en los que la línea TX está en reposo. La figura presenta un esquema de una posible solución al circuito. 9600 b.p.s. StSend Fin Maq Est Transm Transmit resets resets Contador de Baudios (Mod 5208) S9600 Contador de Bits (Mod 11) Selector 0 0 1-8 DataPar GenParidad Transmit TX 9 1 10 Práctica 3. Receptor de una línea serie 5 Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital 3.1.1 Máquina de estados La máquina de estados de transmisión controla la transmisión, siguiendo el circuito del esquema anterior es: StSend=0 Reposo Transmite=0 Fin=1 StSend=1 Fin=0 Transmision Transmite=1 Donde StSend es un pulso de inicio de transmisión, Fin es un pulso de fin de transmisión dado por el contador de bits. Transmite tiene la misión de habilitar todo el tiempo del proceso durante el cual se transmite. La señal Transmite activará el contador de baudios de transmisión y el de bits, es decir, esta señal invertida mantiene a cero estos contadores cuando no hay transmisión. 3.1.2. Contador de Bits de Transmisión Este contador debe contar al menos 11 bits, donde el bit 0 es el de start, que está a ‘0’, los bits 1 a 8 son la información transmitida, el bit 9 es el de paridad y el bit 10 debe estar a ‘1’. Este contador cambia cada 1/9600 segundos. Para esta parte de la práctica se procederá a fijar un valor al dato de entrada. Se propone que para este dato se utilice el carácter hexadecimal 0x45. 3.2 RECEPTOR En la figura 1 se muestra el esquema general del receptor. Podemos distinguir los siguientes bloques a diseñar en VHDL: • Desmultiplicador para ajustar la frecuencia de recepción • Registro de recepción, conversor de serie a paralelo • Generador de paridad • Máquina de estados de recepción En la figura se muestra un esquema de la arquitectura del receptor basado en los bloques anteriormente mencionados. Práctica 3. Receptor de una línea serie 6 Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital RX Maq Est Receptor ByteOki Fin Contador de Baudios s19200 (Mod 2604) Resets SmplBit Contador de Bits (Mod 10) Registro Desplazamiento prt b7 b0 st DataRec (1 a 8) ByteOki ByteOk ByteOkp Gen Paridad ByteOkp El receptor ha de muestrear la información a mitad de bit, para asegurar que la recepción sea correcta. Por ello utilizaremos un contador que desmultiplica a doble velocidad, y muestreará la señal cada dos pulsos, tal y como se muestra en la figura. Start B0 B7 Paridad Stop Muestreo La velocidad de bits se ha de construir a partir de una desmultiplicación del reloj de 50MHz. Se construye un contador desmultiplicador de 50Mhz a 19200 (2x9600) ciclos por segundo: 50000000 / 19200=2604 Este contador se utilizará para muestrear cada bit. Se realizará de la siguiente manera, mediante una máquina de estados: • Se recibe el bit de Start, en el que se pone la línea RX a cero. • El contador se pone a cero y utilizaremos una señal de para muestrear cada dos pulsos de saturación. • Se han de contar 9 bits (8 + paridad) • El dato válido se genera a partir de la valoración de la paridad. La necesidad de un contador de velocidad doble se justifica para garantizar que el muestreo se realizará a mitad del tiempo de un bit de la información recibida, tal y como se muestra en la figura. 3.2.1 Diseño de la máquina de estados de recepción 9600 b.p.s. Práctica 3. Receptor de una línea serie 7 Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital Esta máquina de estados controla el muestreo de señales activadas por el contador de baudios. Se activa a partir del bit de start por RX. En reposo los contadores no se mueven. Una vez que se activa el contador de baudios, se atiende a su bit de saturación. Cada dos bits de saturación, se muestrea la señal de RX a través de SmplBit. El mecanismo se detiene cuando el número de bits muestreado es igual al valor de saturación del contador de bits ‘SatCtBits’. 3.2.2. Registro de desplazamiento La información se guarda en un registro de desplazamiento que cuando se habilita, se , transfiere la información al registro adyacente, y si no está habilitado, se retiene la información. 3.3. VERIFICACIÓN Para realizar la verficación de la información enviada se propone realizar dos acciones: 1. Representar en el display de la placa la información de los bytes recibidos. LA representación en el display se facilita en un módulo VHDL ya realizado y disponible en la web de descargas. 2. Reenvío al PC de la información de los bytes, mediante el transmisor. Los valores enviados aparecerían en la consola de la herramienta ‘hiperterminal’. 3.3.1 Hiperterminal Práctica 3. Receptor de una línea serie 8 Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital Es una aplicación de Windows que permite realizar operaciones de comunicación por diferentes canales, y en particular por el puerto serie, identificaci por COM1:. Se encuentra en Inicio‐>Programas‐>Accesorios‐>Comunicaciones‐>Hyperterminal Con el programa desconectado (icono del teléfono descolgado), Archivo‐>Propiedades Debe aparecer conectar usando COM1. Aquí presionar el botón ∙”Configurar”. Aquí debe aparecer la configuración de la velocidad del puerto serie: Práctica 3. Receptor de una línea serie 9 Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital La figura muestra la configuración del puerto serie para realizar esta práctica. Una vez configurado la información que se escriba desde teclado en la consola del hyperterminal se transfiere automáticamente al puerto serie, y la información recibida será escrita en la consola. Los caracteres escritos no aparecen en la configuración por defecto de la consola. 4. Desarrollo de la Práctica Como se ha comentado comenzaremos por el transmisor. Realizaremos una primera versión que enviará al PC un valor fijo. 4.1 Contador Descripción Entidad CONT_BAUDIOS y CONT_BITS Contador síncrono con habilitación y valor de saturación. Se llamará a esta instancia en cuatro ocasiones, para dos temporizar los baudios y dos para contar bits. entity contador is Generic (Nbit: INTEGER := 8; ValSat: INTEGER := 100); Port ( clk : in STD_LOGIC; reset : in STD_LOGIC;--reset asíncrono enable : in STD_LOGIC; resets : in STD_LOGIC;--reset síncrono Sat: out STD_LOGIC; Q : out STD_LOGIC_VECTOR (Nbit-1 downto 0)); end contador; Descripción de los puertos clk reset enable resets Sat Reloj Reset asíncrono activo a nivel alto Señal de habilitación activa a nivel alto. Si enable=’1’ el contador avanzará uno en la cuenta en el flanco positivo de reloj. Reset síncrono activo a nivel alto. Si resets=’1’ el contador pasará a cero en el siguiente flanco positivo de reloj. Pulso de salida que aparece cuando el contador alcanza ValSat. Práctica 3. Receptor de una línea serie 10 Q Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital Salida de Nbit igual a la valor de la cuenta. 4.2 Paridad Descripción Entidad dato Paridad 4.3 GEN_PAR Circuito totalmente combinacional para calcular el bit de paridad del byte. entity paridad is Port ( data : in STD_LOGIC_VECTOR (7 downto 0); parity: out STD_LOGIC); end paridad; Descripción de los puertos Byte para calcular la paridad Valor de la paridad Máquina de estado de transmisión Descripción Entidad clk rst StSend Fin Transmit FSM_TRANSMISOR Circuito de control del proceso de transmisión entity fsmTrns is Port ( clk : in STD_LOGIC; rst : in STD_LOGIC; StSend : in STD_LOGIC; Fin : in STD_LOGIC; Transmit : out STD_LOGIC); end fsmTrns; Descripción de los puertos Reloj de sistema de 50MHz Reset asíncrono activo a nivel alto Comienza el proceso de transmisión. Debe ser un pulso de un periodo de reloj Final del contador de bits de transmisión Esta señal está a ‘1’ durante el periodo de tranmisión. 4.4 Máquina de estado de recepción Descripción Entidad FSM_RECEPTOR Circuito totalmente combinacional para calcular el bit de paridad del byte. entity fsmRec is Port ( clk : in STD_LOGIC; rst : in STD_LOGIC; RX : in STD_LOGIC; satCtBits : in STD_LOGIC; s19200 : in STD_LOGIC; clrCtBits : out STD_LOGIC; smplBit : out STD_LOGIC; ByteOki : out STD_LOGIC); end fsmRec; Práctica 3. Receptor de una línea serie 11 Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital Descripción de los puertos clk Reloj de sistema de 50MHz rst Reset asíncrono activo a nivel alto RX Línea de recepción satCtBits Señal indicadora del final del contador de bits S19200 Saturación del contador de baudios clrCtBits Reset síncrono de los contadores de baudios y de bits SmplBit Pulso de muestreo de un bit. Se habilita el contador de bits y el registro de desplazamiento. Debe durar un periodo de reloj. ByteOk Se alcanza el final de la cuenta de byte y se debe verificar la paridad. SmplBit Muestreo de un bit 4.5 Registro de Desplazamiento Descripción Entidad clk reset enable RX DataPar REG_DESPL Registro de desplazamiento que lee el valor de la información recibida en modo serie. Se lee el bit menos significativo primero. entity SerialPar is Generic (Nbits: INTEGER := 10); Port ( clk : in STD_LOGIC; reset : in STD_LOGIC; enable : in STD_LOGIC; RX: in STD_LOGIC; DataPar: out STD_LOGIC_VECTOR (Nbits-1 downto 0)); end SerialPar; Descripción de los puertos Reloj de sistema Reset asíncrono activo a nivel alto Señal de habilitación activa a nivel alto. Si enable=’1’ cada registro transferirá el contenido de cada uno de sus bits al siguiente. Señals de recepción serie. Valor de salida paralelo. El registro de desplazamiento ha de realizarse siendo el Msb el registro que primero recibe la información. Puede realizarse utilizando el siguiente código concurrente: pData(Nbits‐2 downto 0)<=Data(Nbits‐1 downto 1) when(enable=ʹ1ʹ) else Data(Nbits‐2 downto 0); pData(Nbits‐1)<=RX when(enable=ʹ1ʹ) else Data(Nbits‐1); 4.6 Presentación de la información PRES_INFO Práctica 3. Receptor de una línea serie 12 Departamento de Ingeniería Electrónica. Universidad de Sevilla Asignatura: Laboratorio de Microelectrónica Digital Descripción Presenta la información en el display de 7 segmentos. Se trata de la práctica 1 adaptada a este problema. Se entrega como parte del enunciado. entity PrDisplay is Entidad Port ( clk : in STD_LOGIC; reset : in STD_LOGIC; data0: in STD_LOGIC_VECTOR (7 downto 0); data1: in STD_LOGIC_VECTOR (7 downto 0); siete_seg: out STD_LOGIC_VECTOR (6 downto 0); select: out STD_LOGIC_VECTOR (3 downto 0)); end PrDisplay; clk reset Data0 Data1 select DataPar Descripción de los puertos Reloj de sistema Reset asíncrono activo a nivel alto Valor del registro 0 a representar Valor del registro 0 a representar Selector del display Valor del display de siete segmentos 4.7 Conexionado de pines de entrada/salida El fichero “USER CONSTRAINTS FILE” debe contener la siguiente información: NET ʺSelector<0>ʺ LOC = ʺE13ʺ ; NET ʺSelector <1>ʺ LOC = ʺF14ʺ ; NET ʺSelector <2>ʺ LOC = ʺG14ʺ ; NET ʺSelector <3>ʺ LOC = ʺD14ʺ ; NET ʺclkʺ LOC = ʺT9ʺ ; NET ʺRXʺ LOC = ʺT13ʺ ; NET ʺrstʺ LOC = ʺL14ʺ ; NET ʺSiete_Seg<1>ʺ LOC = ʺE14ʺ ; NET ʺSiete_Seg<2>ʺ LOC = ʺG13ʺ ; NET ʺSiete_Seg<3>ʺ LOC = ʺN15ʺ ; NET ʺSiete_Seg<4>ʺ LOC = ʺP15ʺ ; NET ʺSiete_Seg<5>ʺ LOC = ʺR16ʺ ; NET ʺSiete_Seg<6>ʺ LOC = ʺF13ʺ ; NET ʺSiete_Seg<7>ʺ LOC = ʺN16ʺ ; NET ʺTXʺ LOC = ʺR13ʺ ; Práctica 3. Receptor de una línea serie 13