Lógica Programable -Introducción -

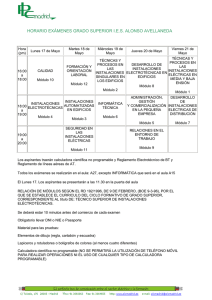

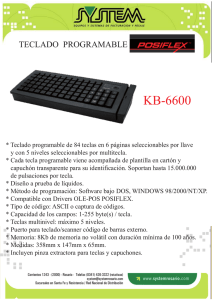

Anuncio

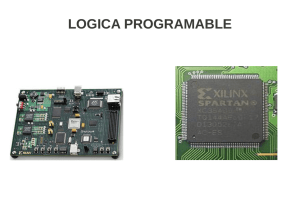

Lógica Programable -Introducción Introducción a los Sistemas Lógicos y Digitales 2008 Sergio Noriega – Introducción a los Sistemas Lógicos y Digitales - 2008 Memorias Lógica Programable Clasificación según acceso: SRAM Volátiles Simple puerto Doble puerto DRAM Aleatorio No volátiles ROM PROM EPROM EEPROM FLASH NVRAM Secuencial Registro de desplazamiento Circuito de acoplamiento de carga (CCD) FIFO (First In First Out) LIFO (Last In First Out) Contenido CAM (Content Addressable Memory) Memorias Lógica Programable Introducción a los Sistemas Lógicos y Digitales 2007 Memorias Lógica Programable Introducción a los Sistemas Lógicos y Digitales 2007 Memorias Lógica Programable Introducción a los Sistemas Lógicos y Digitales 2007 Memorias Lógica Programable Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable Caminos posibles para desarrollo de lógica: Lógica convencional: •Compuertas (diseño discreto a muy bajo nivel de integración). •Circuitos integrados específicos básicos (sumadores, contadores, FF´s , decodificadores, MUX´s, DeMUX´s, etc.) •Circuitos integrados específicos complejos (timer, contador universal, etc.) Lógica programable por hardware: •Memoria ROM y sus derivados ( ROM, PROM, EEPROM, Flash, etc.). •Lógica programable (PAL, GAL, EPLD, CPLD-FPGA, etc.). Lógica programable por software: Microprocesador (microprocesador, microcontrolador, DSP, etc.). Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable Exigencias del mercado actual: •Equipos cada vez mas complejos. •Especificaciones variables. •Reducción de costos (tiempos de desarrollo ↓↓). El diseñador debe por lo tanto: •Requerir de dispositivos mas modernos. •Herramientas de desarrollo mas flexibles. •Posibilidad de actualizar los diseños. •Disminuir costos en el chequeo del producto final. Solución: Disponer de una plataforma de diseño que le brinde una solución universal. Generalmente esto se consigue en el ámbito digital, con la elección de sistemas basados en el empleo de microprocesadores y/o lógica programable. Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable Soluciones posibles con lógica programada por hardware MPGA (Mask Programmabled Gate Array): Diseño específico de chips. Rentable para muy grandes volúmenes de componentes. ASIC (Application Specific Integrated Circuit): Diseño semi-programable. Rentable para volúmenes moderados de partes. FPL (Field Programmable Logic): Totalmente configurable. Rentable para volúmenespequeños de partes. Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable Ventajas del uso de lógica programable sobre lógica standard Mayor performance: Mayor velocidad. Menor tamaño. Mayor confiabilidad. Mejor adaptación a cambios en el diseño. Control rápido y eficiente del diseño. Menor Menor Menor Menor costo de desarrollo: tiempo muerto en el desarrollo. cantidad de partes diferentes. cantidad diferentes de fabricantes. Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable ESTO CUBRE SOLO EL DISEÑO DE CIRCUITOS COMBINATORIOS Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable ESTO CUBRE SOLO EL DISEÑO DE CIRCUITOS COMBINATORIOS Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable ESTO CUBRE SOLO EL DISEÑO DE CIRCUITOS COMBINATORIOS Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable ESTO CUBRE SOLO EL DISEÑO DE CIRCUITOS COMBINATORIOS Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable ESTO CUBRE SOLO EL DISEÑO DE CIRCUITOS COMBINATORIOS Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable ESTRUCTURA DE UNA MEMORIA PROM La opción de desarrollar lógica combinatoria con ROM tiene la ventaja de poder implementar múltiples funciones de varias variables simultáneamente Por ejemplo una ROM de 64KBytes x 8 permite generar 8 funciones de hasta 16 variables cada una. Los problemas son: baja velocidad de respuesta, subutilización del hardware e imposibilidad de generar lógica secuencial. Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable Evolución de los Dispositivos Lógicos Programables (PLD) Primera generación: PAL (Programmable Array Logic) PLA (Programmable Logic Array) GAL (Generic Array Logic) Segunda generación: EPLD (Electrically Programmable Logic Device) Tercera generación: FPGA (Field Programmable Gate Array) Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable ESTRUCTURA BÁSICA DE UNA PAL Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable ESTRUCTURA BÁSICA DE UNA PLA Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable Esquema del circuito asociado a una de las compuertas AND que forman la estructura de una PAL básica. intacto Esquema físico para la implementación de la función quemado AB no hay unión Esquema simplificado para la implementación de la función AB hay unión Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable PAL (Programmable Array Logic) En el año 1977 Monolithic Memories Inc. creó el primer circuito integrado digital programable por el usuario. Vista del primer chip programable (PAL16L8) Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable PAL (Programmable Array Logic) Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable PAL (Programmable Array Logic) PAL16L8 Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable PAL (Programmable Array Logic) PAL16L8 Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable PAL (Programmable Array Logic) PAL16R8 Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable PAL (Programmable Array Logic) Lógica Programable PAL16R8 PAL16R8 Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable GAL16LV8 Lattice Semiconductor Lógica Programable Generic Array Logic La GAL es a diferencia de la PAL programable con memoria EEPROM a fin de poder ser re-programable un número muy grande de veces (10.000 y con mantenimiento de la información de unos 10 años). LV trabaja con 3.3V y V con 5V. Posee 8 bloques lógicos idénticos para generar funciones Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable GAL16LV8 Lógica Programable OLMC (Out Logic Macrocell) Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable GAL16LV8 Lógica Programable La GAL16LV8 tiene 3 modos de configuración de In/Out: Modo Simple (similar a la estructura de la PAL16L8) Modo Complejo (agrega la posibilidad de usar Tri-State) Modo Registrado (permite salidas con FFD) Modo Simple Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable GAL16LV8 Lógica Programable Modo Complejo Modo Registrado Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable GAL16LV8 Lógica Programable Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable EPLD Lógica Programable Los circuitos programables digitales de segunda generación también se basan en el uso de matriz AND-OR (programable la AND) para generar un dado número de funciones lógicas generalmente de hasta 5 variables. Las características mas sobresalientes de las EPLD ó también llamadas CPLD (Complex PLD) son: > Utilizan tecnología E2PROM para su programación. > Existe una matriz compleja de interconexión (PIM) con gran flexibilidad en la configuración interna y asignación de señales a los pines de E/S. > Poseen una interface serie especial con propósitos de programación y test en fabrica y por el usuario. > Su estructura interna cuenta con bloques idénticos (Logic Blocks) para genera una función combinatoria con posibilidad de salida registrada. > Suelen utilizarse para aquellos diseños donde se requiera de baja a mediana complejidad con recursos fundamentalmente de lógica combinatoria y a bajo costo. Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable FPGA Lógica Programable Son dispositivos de 3ra. generación con bloques lógicos basados en LUTs. Tienen una matriz de interconexión mucho mas compleja y distribuída que las EPLD. Existen versiones de FPGA que tienen como elementos de memoria celdas SRAM (las mas comunes), además de anti-fusibles y Flash. Con RAM se tiene la ventaja de poder implementar diferentes tipos de memoria además de poseer una mayor densidad de integración lo que permite mayor realización de lógica. La desventaja es la necesidad de una memoria externa de booteo. Actualmente hay versiones de FPGA con bloques dedicados de PLL y multiplicadores aritméticos para implementar DSP. Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Lógica Programable Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable EPLD vs. FPGA Lógica Programable Las EPLD son mas baratas y no requieren el empleo de memoria serie para su configuración como las FPGA basadas en RAM. Son de granuladidad gruesa. Las FPGA basadas en RAM en cambio permiten mayor densidad de integración, tanto interna como disponibilidad de pines de E/S, una gran capacidad de síntesis secuencial y flexibilidad en el diseño lógico. Las FPGA basadas en anti-fusibles son OTP (One Time Programmable) y su utilización está restringuida al ámbito aeroespacial. Las FPGA basadas en tecnología E2PROM sacrifican espacio en beneficio de eliminar la memoria E2PROM serie y abaratar un poco los costos. Las FPGA suelen ser de granualidad fina. Introducción a los Sistemas Lógicos y Digitales 2007 Lógica Programable Bibliografía: Apuntes de teoría: • Trabajo Final “Introducción a los Dispositivos FPGA: Análisis y Ejemplos de Diseño ”. Autor: Eduardo Bozich. Año 2005. Libros: • • • • • • • “Circuitos microelectrónicos”. Sedra - Smith. Ed. Oxford. “Sistemas Digitales”. R. Tocci, N. Widmer, G. Moss. Ed. Prentice Hall. “Diseño Digital”. M. Morris Mano. Ed. Prentice Hall. 3ra edición. “Diseño de Sistemas Digitales”. John Vyemura. Ed. Thomson. “Diseño Lógico”. Antonio Ruiz, Alberto Espinosa. Ed. McGraw-Hill. “Digital Design:Principles & Practices”. John Wakerly. Ed. Prentice Hall. “Digital Design with CPLD Applications and VHDL”. Robert Dueck. Ed. Thomson . • “Diseño Digital”. Alan Marcovitz. Ed. McGraw-Hill. • “Electrónica Digital”. James Bignell, R. Donovan. Ed. CECSA. • “Fundamentos de Diseño Lógico y Computadoras”. M. Mano, C. Kime. Ed. Prentice Hall. Sergio Noriega – Introducción a los Sistemas Lógicos y Digitales - 2008