Pasos para conectar la CPLD al cable JTAG USB 1) El pin VIO, pin

Anuncio

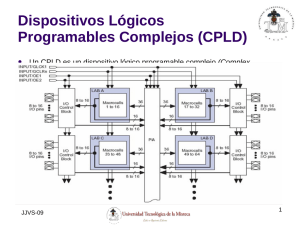

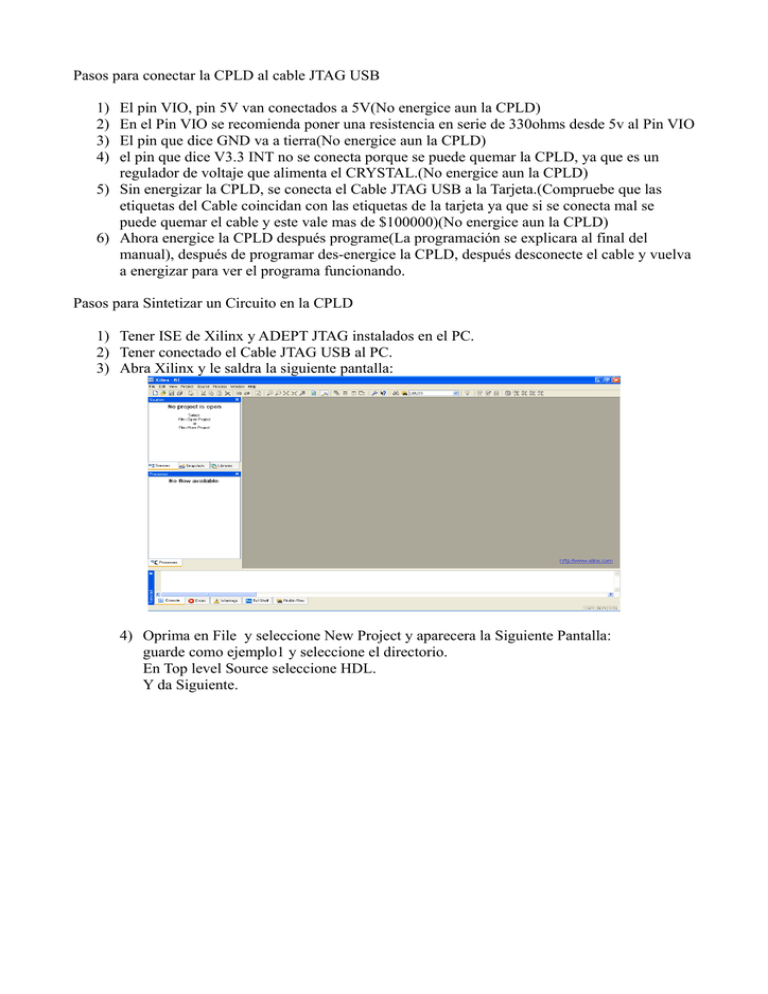

Pasos para conectar la CPLD al cable JTAG USB 1) 2) 3) 4) El pin VIO, pin 5V van conectados a 5V(No energice aun la CPLD) En el Pin VIO se recomienda poner una resistencia en serie de 330ohms desde 5v al Pin VIO El pin que dice GND va a tierra(No energice aun la CPLD) el pin que dice V3.3 INT no se conecta porque se puede quemar la CPLD, ya que es un regulador de voltaje que alimenta el CRYSTAL.(No energice aun la CPLD) 5) Sin energizar la CPLD, se conecta el Cable JTAG USB a la Tarjeta.(Compruebe que las etiquetas del Cable coincidan con las etiquetas de la tarjeta ya que si se conecta mal se puede quemar el cable y este vale mas de $100000)(No energice aun la CPLD) 6) Ahora energice la CPLD después programe(La programación se explicara al final del manual), después de programar des-energice la CPLD, después desconecte el cable y vuelva a energizar para ver el programa funcionando. Pasos para Sintetizar un Circuito en la CPLD 1) Tener ISE de Xilinx y ADEPT JTAG instalados en el PC. 2) Tener conectado el Cable JTAG USB al PC. 3) Abra Xilinx y le saldra la siguiente pantalla: 4) Oprima en File y seleccione New Project y aparecera la Siguiente Pantalla: guarde como ejemplo1 y seleccione el directorio. En Top level Source seleccione HDL. Y da Siguiente. 5)Luego aparecera la Siguiente pantalla: (Llene con los Siguientes Valores la Tabla) 6)Al dar Siguiente aparecera la Siguiente pantalla: Se le da Click a New Source. 7) Despues de Dar Click en New Source aparcera la Siguiente Ventana: Seleccionan Verilog Module y en la Caja de texto escriben “ejemplo1” y se da siguiente. 8) Al Dar Siguiente aparecerá la Siguiente Ventana: Llenen la Tabla tal y como aparece en la Imagen, con los puertos IN_A, IN_B, IN_C y OUT, la función de cada puerto sera correspondiente al nombre en Ingles. 9) Al dar Siguiente luego dan Finish y les sale un mensaje que dice que si quiere crear la carpeta de directorio, le da Yes y luego oprime Siguiente, Siguiente y luego Finish. 10) Despues le aparecera la siguiente Ventana: 11) Dentro del Editor de Texto aparece el siguiente texto: Module ejemplo1(IN_A,IN_B,IN_C,OUT) input IN_A; input IN_B; input IN_C; output OUT; ///aca ponemos el codigo de logica digital que necesitamos poner endmodule 12) Ahora Agregamos el Siguiente codigo al Modulo: 13) En la parte Izquierda de la pantalla aparece la siguiente Caja Processes: Donde se dara Click a “Assign Package Pins”: 14) Ahora aparecera la siguiente ventana: Donde aparecera a mano izquierda los nombres de los puertos y en el contenedor de mano derecha la CPLD con sus pines. Los pines de la CPLD se caracterizan por tener colores y formas diferentes en este laboratorio solo se utilizaran los pines de color gris que tienen forma redonda. 15)Ahora nos posicionamos en la caja de contiene el nombre de los puertos en la y damos ZOOM+ para visualizar en nombre de cada pin de la CPLD. Para asignar a las Salidas de la CPLD debemos Arrastrar la celda al Pin disponible, en este caso utilizaremos los Pines(P5,P6,P7 y P8). El P5 lo asignamos a IN_A, el P6 a IN_B, el P7 a IN_C y el P8 a OUT. Debe quedar asi: 16) Ahora vamos File y le damos Save, luego damos ok y cerramos la ventana. 17) Volviendo a Xilinx nos posicionamos en la caja Processes y buscamos la opcion Implement Desing/Synthetize XST y buscamos Check Syntax, y damos click, si este se marca en verde quiere decir que el codigo quedo bien escrito y podemos continuar. 18) Ahora en la misma caja nos ubicamos en la opcion Implement Desing/Optional implementation tools y damos doble click en “Generate SVF/XSFV/STALP file” y aparecera lo siguiente: 19)En la ventana que tiene como Titulo Impact seleccionamos la opcion “Prepare BoundaryScan File” y damos Finish. La ventana impact tiene que quedar como la anterior imagen. 20)Ahora nos sale un Dialog File, nos ubicamos en la raiz de nuestro proyecto y guardamos el archivo *.SVF como ejemplo1 21)Después de guardar nos aparecerá otra caja de Dialogo para abrir un archivo y abrimos el archivo “ejemplo1.jed” 22) ahora nos aparecer el una ventana en Xilinx como la siguiente: Le damos click derecho al integrado y seleccionamos “Program” 23) luego nos saldra la siguiente ventana donde oprimiremos en OK: 24) Ahora abrimos el otro software llamado ADEPT: 25)Ahora repasando los puntos del 1 al 5 para conectar la CPLD al Cable JTAG (esto esta al principio del manual) Una vez Conectada correctamente pare evitar cualquier corto, y una vez energizada la CPLD teniendo conectado el cable JTAG USB al PC procedemos a oprimir el Boton “Initialize Chain” en el programa ADEPT. Deberá actualizarse el programa a lo siguiente: 26)Ahora Oprimimos en el Botón Browse y buscamos el archivo “ejemplo1.svf” 27) Después oprime en el botón “Program” y aparecerá lo siguiente: Cuando termine de programar, cerramos el programa, apagamos la alimentación de la fuente, desconectamos el cable JTAG USB de la CPLD y encendemos de nuevo la CPLD para probar el hardware Diseñado.