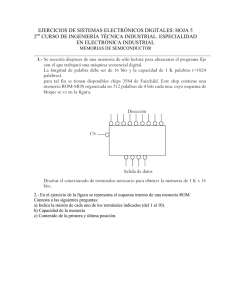

1 - DEFIB

Anuncio

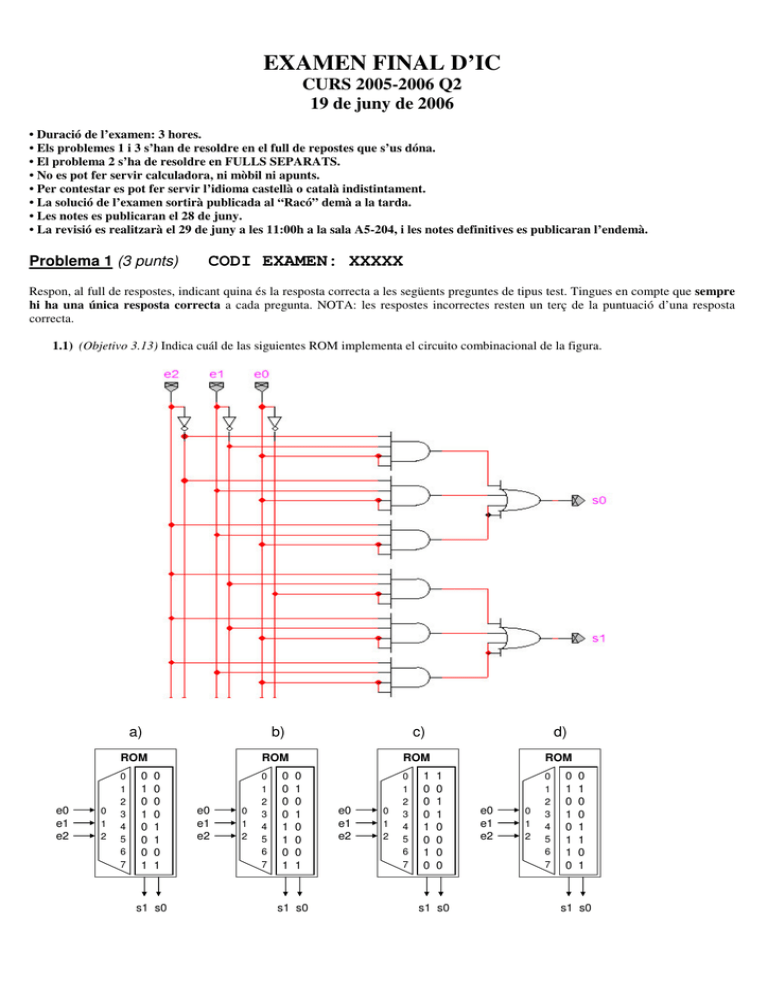

EXAMEN FINAL D’IC CURS 2005-2006 Q2 19 de juny de 2006 • Duració de l’examen: 3 hores. • Els problemes 1 i 3 s’han de resoldre en el full de repostes que s’us dóna. • El problema 2 s’ha de resoldre en FULLS SEPARATS. • No es pot fer servir calculadora, ni mòbil ni apunts. • Per contestar es pot fer servir l’idioma castellà o català indistintament. • La solució de l’examen sortirà publicada al “Racó” demà a la tarda. • Les notes es publicaran el 28 de juny. • La revisió es realitzarà el 29 de juny a les 11:00h a la sala A5-204, i les notes definitives es publicaran l’endemà. Problema 1 (3 punts) CODI EXAMEN: XXXXX Respon, al full de respostes, indicant quina és la resposta correcta a les següents preguntes de tipus test. Tingues en compte que sempre hi ha una única resposta correcta a cada pregunta. NOTA: les respostes incorrectes resten un terç de la puntuació d’una resposta correcta. 1.1) (Objetivo 3.13) Indica cuál de las siguientes ROM implementa el circuito combinacional de la figura. e0 e1 e2 0 1 2 a) b) c) d) ROM ROM ROM ROM 0 1 2 3 4 5 6 7 0 1 0 1 0 0 0 1 0 0 0 0 1 1 0 1 s1 s0 e0 e1 e2 0 1 2 0 1 2 3 4 5 6 7 0 0 0 0 1 1 0 1 0 1 0 1 0 0 0 1 s1 s0 e0 e1 e2 0 1 2 0 1 2 3 4 5 6 7 1 0 0 0 1 0 1 0 1 0 1 1 0 0 0 0 s1 s0 e0 e1 e2 0 1 2 0 1 2 3 4 5 6 7 0 1 0 1 0 1 1 0 0 1 0 0 1 1 0 1 s1 s0 1.2) (Objetivo 8.2) Indica cuál de las siguientes respuestas describe correctamente la modificación de los registros o posiciones de memoria después de haber ejecutado la siguiente secuencia de instrucciones del computador SISP-I-1. InstrMem[0x0FBD] MOVI R1, 8 . CMPLT R1, R3, R1 . BZ R1, 2 . XOR R2, R2, R2 Supón que el estado inicial del computador antes de ejecutar la primera instrucción es el siguiente: • La posición i de la memoria de datos contiene el valor i, DataMem[i]=i, para 0 ≤ i ≤ 216–1. • • a) b) c) d) El contenido del registro general Ri vale i para 0 ≤ i ≤ 7. El contenido del registro PC vale 0x0FBD. PC=0x0FC1, PC=0x0FC1, PC=0x0FC0, PC=0x0FC1, R1=1, R1=1, R1=1, R1=0, R2=2 R2=0 R2=0 R2=0 1.3) (Objetivo 4.10) Se dispone del siguiente esquema lógico de un dispositivo secuencial implementado mediante un biestable por estado. Se desconoce su funcionamiento, por lo que se desea obtener su grafo de estados. Si los biestables se inicializan todos a 0 excepto el de más a la derecha que se inicializa a 1, responde cuál de los siguientes grafos corresponde al esquema anterior. 1 x Ei S1 S0 1 1 0 1 0 E0 E1 E0 E1 00 01 11 00 0 a) E3 11 b) 0 0 E2 0 E3 10 1 E2 10 1 0 0 01 1 1 0 0 0 1 0 1 E0 E1 E0 E1 00 01 11 00 1 c) E3 11 0 1 E2 1 d) 1 E3 10 10 0 0 1 E2 1 01 0 1.4) (Objetivo 5.12) Se ha diseñado un procesador de propósito específico que está formado por las unidades de control y de proceso que se muestran a continuación. El tiempo de propagación de los dispositivos es: TROM=200 ut, TBIESTABLE = TREG = 100 ut, TMUX = 50 ut, TZ = 100 ut, TSRL-1 = 0 ut. Supondremos que: • • las señales entran al procesador provenientes de un registro/biestable y la salida del procesador se conecta directamente a un biestable. La ROM implementa un grafo de Moore. ¿Cuál es el tiempo de ciclo mínimo que puede tener la señal de reloj (Clk) para que el procesador funcione correctamente? a) b) c) d) 350 ut 300 ut 150 ut 450 ut 1.5) (Objetivos 6.4 y 2.5) Dados los vectores de 8 bits X e Y se obtiene un vector de 8 bits como salida de cada uno de los siguientes dispositivos: • Restador binario, SUB(X,Y). • Desplazador lógico, SHL(X,Y). Como trabajamos con 8 bits, considerad que los 4 bits de menor peso de Y, interpretados en complemento a 2, indican el exponente de la potencia de 2 por la que se multiplica el valor representado por X. Indica cuál de las siguientes afirmaciones es cierta. a) Para X = 10110110 e Y = 00111011, SUB(X,Y) representa el resultado correcto de la resta interpretando los operandos y el resultado como números enteros en complemento a 2. b) Para X = 01011001 e Y = 10001110, SUB(X,Y) representa el resultado correcto de la resta interpretando los operandos y el resultado como números enteros en complemento a 2. c) Para X = 10101010 e Y = 00001010, SHL(X,Y) representa el resultado correcto de la multiplicación por la potencia de 2 que indica Y, interpretando el operando X y el resultado como números naturales en binario. d) Para X = 10101010 e Y = 00001111, SHL(X,Y) no representa el resultado correcto de la multiplicación por la potencia de 2 que indica Y, interpretando el operando X y el resultado como números enteros en complemento a 2. 1.6) (Objectiu 5.8.2) Indica quina és la implementació interna correcta d’un registre de n bits amb senyal de càrrega com el de la figura: a) b) c) Full de respostes del Problema 1 d) CODI: XXXXX NOM: .................................................................................................................... DNI:.......................... Indica la resposta correcta a cadascuna de les preguntes del problema 1, especificant la lletra (a, b, c o d) corresponent, a l’espai indicat pels punts suspensius: La resposta correcta a la pregunta 1.1 és ........ La resposta correcta a la pregunta 1.2 és ........ La resposta correcta a la pregunta 1.3 és ........ La resposta correcta a la pregunta 1.4 és ........ La resposta correcta a la pregunta 1.5 és ........ La resposta correcta a la pregunta 1.6 és ........ Problema 2 (3,5 punts) Es vol dissenyar un multiplicador de nombres naturals de n bits. Ens proporcionen la següent Unitat de Procés, idèntica a la que es va fer servir a la pràctica 3. X IniUP D(0) Y SL-1 SRL-1 1 0 MUX 1 0 MUX D(j+1) REG REG D(j) X·y B(j) yj b0 Clk B(j)<0> M 0 W(0) ADD 1 0 MUX W(j+1) REG W(j) W El bloc X·y (Mulbit) fa Ands en paral·lel dels n bits del bus D(j) amb el bit yj, el bloc “SL-1” genera els n bits de menys pes del resultat de desplaçar una posició cap a l’esquerra (multiplicació per 2), el bloc “SRL-1” desplaça una posició cap a la dreta (divisió per 2) i el bloc 0 dóna un zero codificat en binari amb els n bits que tenen tots els busos de dades. Emprarem el següent algoritme artimètic per a realitzar la multiplicació: D (0 ) = X B (0 ) = Y W (0 ) = 0,0,...,0 per a j = 0 fins n-1 fer M = MULBIT ( D ( j ), B ( j ) < 0 >) W ( j + 1) = ADD (W ( j ), M ) D ( j + 1) = SL - 1( D ( j )) B ( j + 1) = SRL - 1( B ( j )) fi_per_a W = W (n) El funcionament del multiplicador com a caixa negra ha de ser el següent: • Al cicle en què el senyal IniMul val 1, les dades dels busos d’entrada X i Y són vàlids i s’han d’emmagatzemar per a poder iniciar la seva multiplicació. • Les dades només estan un cicle a l’entrada, el cicle en què IniMul val 1. • El multiplicador indicarà que té el resultat correcte al bus de sortida, posant a 1 durant un cicle el senyal de control FinMul. • Només està garantida la presència de la dada correcta al bus de sortida del multiplicador durant aquell cicle, pel què el sistema exterior ha d’estar esperant aquest cicle, per a no perdre el resultat. • Si durant la multiplicació d’un parell de nombres (després del cicle en què IniMul val 1 i abans de que FinMul valgui 1), arriba per l’entrada IniMul un 1, el multiplicador farà cas omís d’aquesta petició i continuarà amb el càlcul que ja estava realitzant. • Al cicle en què FinMul val 1, ja pot començar una nova multiplicació, si IniMul val 1 en aquell mateix cicle. Es demana: a) (Objectiu 5.2) Dibuixa l’esquema de connexió Unitat de control - Unitat de procés. UC UP b) (Objectiu 5.10) Dibuixa el graf d’estats de la Unitat de Control, si les dades a multiplicar estan codificades en binari amb 4 bits. Es vol ara que s’acabi la multiplicació tan aviat com estigui disponible el resultat. S’ha de tenir en compte que si els k bits de més pes de la dada Y valen 0, no cal fer les k darreres iteracions de l’algorisme, perquè no modificaran el resultat ja obtingut. c) (Objectiu 5.10) Dibuixa els canvis que cal fer a la Unitat de Procés que es proporciona. Dibuixa també el graf d’estats de la nova Unitat de Control. El disseny inicial del multiplicador de 4 bits pot proporcionar resultats incorrectes, quan el resultat no és representable amb 4 bits. d) (Objectiu 2.5.5) Quants bits ha de tenir el bus de sortida W per a que el resultat sigui sempre representable? e) (Objectiu 5.10) Dibuixa els canvis que cal fer a la Unitat de Procés que es proporciona, si es vol que el resultat sempre sigui representable i les entrades estan codificades amb 4 bits. No oblidis indicar el tamany de tots els busos del circuit. Problema 3 (3,5 puntos) Pregunta a): Se ha creado la tabla de la hoja de respuestas de la pregunta 3 a) para indicar el contenido de la ROM que implementa parte de la lógica de control del SISP-I-1 según el circuito “Unidad de Control SISP-I-1 con ROM” del apéndice. Completad con los bits correctos las filas y las columnas sombreadas en la tabla de la hoja de respuestas. Las 3 filas sombreadas hacen referencia al contenido de la ROM de las direcciones 16 a 19 (instrucción ST), 27 (instrucción BNZ con z = 1) y 28 y 29 (instrucción IN). Las 2 columnas sombreadas son las de las señales WrD y Mx@A. (Objectivo 9.1) Pregunta b): (Objectivo 9.5) Se define una extensión del lenguaje máquina SISA-I añadiéndole a este dos nuevas instrucciones, la MOVR (copiar el contenido de un registro en otro registro) y la BR (salto incondicional relativo al PC). El formato binario, la semántica y el formato en ensamblador de las dos nuevas instrucciones es el siguiente (los bits marcados con ? tenéis que definirlos vosotros): MOVR: Binario: Ensamblador: Semántica: 1???dddaaa?????? MOVR Rd, Ra Rd Ra BR: Binario: Ensamblador: Semántica: 1??????????????? BR Ns PC PC + SEXT(N) (N es el campo de 8 bits de la instrucción que tenéis que denotar como nnnnnnnn. Ns que aparece en la sentencia ensamblador es el entero representado por el vector N en complemento a dos). Las dos nuevas instrucciones se deben añadir a la implementación actual del procesador SISP-I-1 que tiene una pequeña ROM en la lógica de control (Figuras del apéndice). Las dos instrucciones se pueden añadir cambiando solamente el contenido de algunas de las direcciones de la pequeña ROM de la lógica de control y sin necesidad de efectuar ningún otro cambio en el computador. Para poder hacer esto se os pide: b1) Indica el formato binario que debe tener cada una de las dos nuevas instrucciones. Dad el valor (0, 1, d, a, n , x) a cada uno de los bits marcados con ? en el formato binario de la definición de las instrucciones que acabamos de hacer. Usa para ello la hoja de respuestas. (Objectivo 9.5.1) b2) Completa las dos filas de la tabla de la hoja de respuestas de la pregunta 3 b2) que indican el contenido de la ROM, en las direcciones que tú indiques, para implementar las dos nuevas instrucciones. Indica cuando sea necesario con x los bits de la dirección de la ROM para que cada fila haga referencia a las direcciones de la ROM implicadas. Indica con x los valores de los bits del contenido de la ROM que pueden valer indistintamente 0 o 1. (Objectivo 9.5.3) NOM: .................................................................................................................... DNI:.......................... Full de respostes del Problema 3 Nota aclaratoria: CO = INS(15:12) 8/6-SE Mx@B Mx@A Rb/I In/Ld InLd/Alu z WrIO e 0 TknBr 1 Not used Not used CO 2 WrMem Contenido de la ROM Dirección ROM 3 e = INS(8) WrD Pregunta a) CODI: XXXXX AND, OR, XOR, NOT ADD, SUB, SHA, SHL CMPLT, CMPLE, -, CMPEQ CMPLTU, CMPLEU, -, ADDI LD ST 0:3 0 0 0 0 x x x x 4:7 0 0 0 1 x x x x 8:1 0 0 1 0 x x x x 12:15 0 0 1 1 x x x x 16:19 0 1 0 0 x x x x 20:21 0 1 0 1 0 x x x 22:23 0 1 0 1 1 x x x 24 0 1 1 0 0 0 x x 25 0 1 1 0 0 1 x x 26 0 1 1 0 1 0 x x 27 0 1 1 0 1 1 x x 28:29 0 1 1 1 0 x x x 30:31 0 1 1 1 1 x x x BNZ caso z = 1 IN OUT 32:63 x x x x x x x Not Used 1 MOVI MOVHI BZ caso z = 0 BZ caso z = 1 BNZ caso z = 0 Pregunta b1) Binario instrucción MOVR: 1 Binario instrucción BR: 1 Pregunta b2) 1 1 ... ... 8/6-SE Mx@B Mx@A Rb/I In/Ld InLd/Alu 0 WrD 1 WrIO 2 ... WrMem 3 z Not used TknBr e CO Contenido de la ROM Not used Dirección ROM x x MOVR x x BR Formato Instrucciones SISA-I 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0000 Rd Ra Func Rb Aritméticas y Lógicas: AND, OR, XOR, NOT, ADD, SUB, SHA, SHL 0001 Rd Ra Comp Rb Comparación: CMPLT, CMPLE, –, CMPEQ, CMPLTU, CMPLEU, –, – 0010 Rd Ra Inmed6 0011 Rd Ra Offset Load: LD 0100 Rb Ra Offset Store: ST 0101 Rd 0 Inmed8 MOVI 0101 Rd 1 Inmed8 MOVHI 0110 Rb 0 OffsetPC Ruptura Secuencia: BZ (Branch on Zero) 0110 Rb 1 OffsetPC Ruptura Secuencia: BNZ (Branch on Not Zero) 0111 Rd 0 Port Entrada: IN 0111 Rb 1 Port Entrada: OUT 1xxx Suma con inmediato: ADDI x x x x x x x x x x x x Sin Usar Func 000 001 010 011 100 101 110 111 Comp AND OR XOR NOT ADD SUB SHA SHL 000 001 010 011 100 101 110 111 CMPLT CMPLE --CMPEQ CMPLTU CMPLEU ----- Condición menor que menor o igual que igual que menor que (unsigned) menor o igual que (unsigned) ALU SISP-I-1 Y e X X Y MVI ADD X Y F CMP X Y AL F 3 F z b0 b1 b2 0 1 2 7 6 5 4 3 2 1 0 MUX z OP 3 W +1 OP e TknBr WrIO WrM In/Ld InLd/Alu WrD @D @A F Rb/I @B IMMED @IO INSTRUCTION MEMORY PC+ REG 1 0 MUX Clk PC ADDR-INS TknBr ADD OP e TknBr WrIO WrMem In/Ld InLd/Alu WrD @D @A F Rb/I @B IMMED @IO 8-SE z INS RD-INS Instruction In/Ld Clk 1 0 MUX D WrD RD-DATA @D @D WrM !Clk !Clk WrIO WrD INPUT/ OUTPUT 1 0 MUX InLd/Alu RD-IO DataRdM z DataRdIO SISP-I-1 CONTROL LOGIC Unidad de proceso SISP-I-1 REGFILE @A @A @B @B A Wr-Io B A DATA MEMORY Wr-Data B WR-IO WR-DATA IMMED Rb/I ADDR-IO @IO z 1 0 MUX X Y z e OP ALU ADDR-DATA F ALUout F e OP Unidad de Control SISP-I-1 con ROM 6-8-SE INS b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0 IMMED @IO 8 b0 b1 b2 1 0 3MUX b0 b1 b2 b0 b1 b2 1 0 3MUX z b0 b1 b2 b0 b1 b2 3 @B 3 F 3 @A 3 @D 3 OP e In0 In1 In2 In3 In4 In5 Out0 Out1 Out2 Out3 Out4 Out5 Out6 Out7 Out8 Out9 Out10 Out11 PROM-SISP-I-1-CONTROL 8/6-SE Mx@B Mx@A Rb/I In/Ld InLd/Alu WrD WrIO WrMem TknBr