ESTUDIO COMPARATIVO DE LOS DSP`s DEL MERCADO

Anuncio

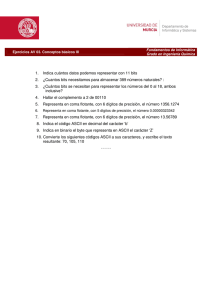

ESTUDIO COMPARATIVO DE LOS DSP’s DEL MERCADO Alumno: Damián Martínez Muñoz Dpto. Ingeniería de Telecomunicación Universidad de Jaén Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real INDICE 1.1 Introducción 3 1.2 Evolución Histórica 3 1.3 Arquitectura de los DSP’s 4 1.4 Clasificación de los DSP’s 4 2 DSP’s de Texas Instruments 7 2.1 Familia TMS320C1x 9 2.2 Familia TMS320C2x 12 2.3 Familia TMS320C2xx 15 2.4 Familia TMS320C3x 18 2.5 Familia TMS320C4x 20 2.6 Familia TMS320C5x 22 2.7 Familia TMS320C54x 24 2.8 Familia TMS320C8x 27 2.9 Familia TMS320AVxxx 30 3 DSP’s de Motorola 33 3.1 Familia DSP561xx 33 3.2 Familia DSP5600x 34 3.3 DSP96002 35 4 DSP’s de Analog Devices 37 4.1 Familia ADSP-2100 38 4.2 Familia ADSP-21cspxx 39 4.3 Familia ADSP-21020 40 4.4 Familia SHARC (ADSP-2106x) 41 ANEXO: Tablas comparativa 43 Bibliografía 49 Direcciones WEB de interés 49 Damián Martínez Muñoz 2 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 1.1 Introducción En el presente trabajo se pretende hacer una descripción del mercado actual de Procesadores Digital de Señal (DSP). A pesar de que el número de fabricantes de DSP’s es cada vez más elevado, en este estudio sólo nos vamos a centrar en los tres principales fabricantes: Texas Instruments, Motorola y Analog Devices. Primero se hará un estudio pormenorizado de las diferentes familias de DSP’s que ofrece cada fabricante, resaltando sus características diferenciales de unas respecto a las otras. El primer fabricante en ser abordado es Texas Instruments. Este lugar es de justicia ya que fueron los pioneros en esta nueva clase de dispositivos. El segundo fabricante estudiado es Motorola. Aunque se sumó al mercado de DSP’s con cierto retraso, ha conseguido ocupar un lugar destacado dentro de un mercado tan competitivo. El tercer y último fabricante estudiado es Analog Devices. Este fabricante es uno de los que ha experimentado un mayor incremento de cuota de mercado en los últimos años. Las razones fundamentales de este desarrollo radica en la gran cantidad de memoria integrada en el mismo chip y el precio económico. El trabajo concluye con una tabla en la que aparecen la mayor parte de los DSP’s del mercado agrupados por las características de precisión que ofrecen. En esta tabla no sólo aparecen los tres fabricantes anteriormente citados sino también el resto de fabricantes. 1.2 Evolución Histórica La aparición de los DSP’s se produjo a mediados de la década de los 80 (año 1.984). El primer DSP que apareció en el mercado (TMS320C10 de Texas Instruments) entró a competir directamente con los Microcontroladores de 8-16 bits que había en el mercado. Otros dispositivos con los competían eran los Microprocesadores de propósito general. Rápidamente los DSP’s fueron ganando la batalla a los competidores anteriormente enumerados. Esto condujo a la aparición de nuevos miembros, cada vez más potentes y baratos, en este nuevo segmento del mercado. Entre las razones de este éxito comercial de los DSP’s están: • Elevada potencia de cálculo. • Emulación, simulación y ejecución en tiempo real. • Flexibilidad. • Fiabilidad. • Incremento del rendimiento del sistema. • Coste reducido del sistema. En los últimos años hemos asistido a un crecimiento espectacular en el uso de los DSP’s, comenzando a ser utilizados en campos que hasta ahora casi no había entrado la electrónica (automoción, multimedia, entretenimiento, etc.). Así mismo, su aparición ha permitido que desarrollos que hasta entonces sólo se habían realizado a Damián Martínez Muñoz 3 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real nivel de simulación, hayan podido ser realizados en tiempo real. El crecimiento en el mercado de los DSP’s triplica el que experimenta el resto del mercado electrónico. En resumen, los DSP’s han facilitado la creciente digitalización de los más diferentes campos. Este desarrollo no tiene un final definido, apareciendo cada día nuevas aplicaciones en las que son usadas. Baste con echar una mirada a las revistas especializadas de Tratamiento Digital de la Señal para comprobar la anterior aseveración. 1.3 Arquitectura de los DSP’s La arquitectura de los DSP’s ha sido pensada para poder realizar la operación MAC (multiplicación + suma con el acumulador) en el menor ciclo de instrucciones posible. Esta operación (MAC) es la base en el Tratamiento Digital de la Señal. Si pensamos en la implementación de un filtro digital tenemos que las operaciones básicas que tenemos que realizar son multiplicaciones y sumas. N M i=0 i=0 y[n] = ∑ a i x (n − i ) + ∑ bi x (n − i ) Para conseguir este resultado, la clásica arquitectura Von Neuman ha sido modificada. En la arquitectura Von Neuman existía un único banco de memoria en el que se encontraba tanto la memoria de programa como los datos. En la arquitectura Harvard, se diferencian la memoria de programa de la de datos.. Por tanto, una de las características básicas de los DSP’s es la existencia de varios bancos de memoria. Otro hecho diferencial es que se pretende que en un único ciclo de instrucción se pueda decodificar la instrucción, traer dos datos de memoria, realizar una operación MAC en la ALU y cargar la siguiente posición de memoria de programa. Para conseguir estos resultados se recurre, aparte de aumentar el número de bancos de memoria, a la existencia de varias unidades de proceso trabajando en paralelo. 1.4 Clasificación de los DSP’s Los DSP’s pueden ser clasificados atendiendo a diferentes criterios. La clasificación más extendida es la que tiene en cuenta la precisión con que se realizan las operaciones. Atendiendo a este criterio tenemos la siguiente clasificación: • DSP’s de coma fija: los datos se representan en formato de coma fija. Presentan el problema de la limitación del rango dinámico de los datos que pueden representar. Por contra, su precio es bastante más económico que los de coma flotante. El número de bits usados para representar los datos varía entre los DSP’s de 16 bits y los de 24 bits. Los primeros se aplican sobre todo en control, telecomunicaciones y codificación de voz. Los segundos tienen prácticamente totalmente copado el mercado del audio profesional, siendo una solución intermedia entre los DSP’s de coma fija de 16 bits y los de coma flotante de 32 bits. • DSP’s de coma flotante: los datos son representados con formato de coma flotante. Su rango dinámico es mucho mayor que los de coma fija, aunque su precio es Damián Martínez Muñoz 4 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real mayor. Hay unanimidad en el mercado en cuanto al número de bits usados para representar datos: 32 bits. Su juego de operaciones soportan también operaciones con datos en formato coma fija. Los nuevos miembros de ambos tipos de DSP’s coinciden en que el juego de instrucciones tienden a parecerse a las de los lenguajes de alto nivel (lenguaje C sobre todo). Esto facilita el empleo de compiladores cruzados, de tal forma que facilita el proceso de programación de los DSP’s, sin tener un conocimiento de la arquitectura del DSP empleado. Damián Martínez Muñoz 5 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Texas Instruments Damián Martínez Muñoz 6 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 2 DSP’s de Texas Instruments Texas Instruments engloba su conjunto de DSP’s mediante el prefijo TMS320. Como ya se ha mencionado anteriormente, fue el primer fabricante de estos nuevos dispositivos allá por el año 1.984. Sus productos están ampliamente consolidados en el mercado y ocupan una posición de privilegio respecto a sus competidores. Sin embargo, en algunos ámbitos de aplicación el mercado lo tienen copado otros fabricantes. Las ventajas de los DSP’s de Texas respecto a los de la competencia son: • Gama de productos más amplia. • Líderes en soluciones de mercado. • Fabricación consolidada y compromiso de entrega. • Amplia variedad en opciones de encapsulado. • Mejor soporte técnico desde la aparición de la idea hasta la consecución del producto. • Bajo coste en sistemas de desarrollo y módulos de evaluación. • Simuladores hardware fiables. • Existencia de compiladores cruzados para lenguajes de alto nivel. • Existencia de Debuggers. • Existencia de Emuladores en tiempo real. • Amplia librería de software para aplicaciones. • Servicio hotline de asistencia técnica, también accesible desde Internet • Para algunos de sus productos, hay otros posibles fabricantes por lo que la dependencia tecnológica es menor. La siguiente gráfica representa las diferentes generaciones de DSP’s que conforman la oferta de Texas Instruments. Damián Martínez Muñoz 7 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real ‘C8x Rendimiento 320C80/-40/-50 Multiprocesador DSP - Máximo Rendimiento - Aplicaciones Multimedia - 2 BOPS ‘C4x ‘C3x 320C30/C30-27/-40/-50 320C/LC31 320C31-27/-40/-50/-60 320C32-40/-50 320C40-40/-50/-60 320C44-40/-50/-60 - Muy Alto Rendimiento - Procesamiento en Paralelo. - 60 MFLOPS 32-bit Punto Flotante ‘C54x 320C/LC/VC541 320C/LC/VC542 - Alto Rendimiento. 320LC543/VC543 ‘C5x - 60 MFLOPS 320LC544/VC544 320LC545/VC545 ‘C2xx 320C50/C50-57/-80 320LC546/VC546 320LC50 320LC548/VC548 ‘C2x 320C/BC51/51-57/-80 320C203/LC203-40/-57/-80 320C/BC52/52-57/-80 ‘C1x 320C204-40/-57/-80 320LC52-57 320C25/P25-40/-50 320C205-40/-57/-80 320C10/C10-25 320C26 320C/BC53/53-57/-80 320F206-40/-57/-80 320C14/P14 320LC56/57 320C28/C28-50 - 100 MIPS 320LF207-40/-57/-80 320C/P/LC15 320C203/-57/-80 320BC57S ‘AVxxx 320C209-40/-57 320C/LC16 320C209-/57 - Alto Rendimiento 320C240-40 320C/P/LC17 320AV310 - Alta Integración. -12 MIPS 320F240-40 320C/P17-25 40-50 MIPS 320AV120 - Muy Bajo Coste 320AV220 Optimización - Periféricos Rendimiento / Coste 320AV420 - 6 MIPS 16-bit Coma Fija 40 MIPS Generación A continuación veremos una a una las diferentes familias que aparecen en esta gráfica. Damián Martínez Muñoz 8 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 2.1 Familia TMS320C1X (coma fija) Fueron los primeros DSP’s que aparecieron en el mercado. Son DSP’s de coma fija de 16 bits. Hay una gran cantidad de miembros en esta familia, diferenciándose principalmente en el encapsulado, velocidad y configuración de memoria interna. Puntos destacados: • Diferentes configuraciones de Memoria RAM, ROM ó OTP PROM interna para una mayor flexibilidad en el diseño. • En ella se encuentran muchos de los DSP’s más económicos del mercado. • Capacidad de integración a través de la librería cDSP. • Posibilidad de escoger entre 5 versiones (‘C10,’C14,’C15,’C16,’C17) para optimizar los costes del sistema. Aplicaciones Fundamentales: • • • • • Sistema antibloqueo de frenos (ABS). Instrumentos musicales. Medidores de energía. Servomecanismos y control de motores. Contestadores automáticos digitales. Características : • • • • • • • • • • • • • 144 palabras de memoria RAM interna programable para el ‘C10, 256 palabras para el resto de dispositivos ‘C1x. 1.5k palabras de programa en ROM en el ‘C10, 4k en el ‘C14,’C15,’C17 y 8k en el ‘C16. Opciones con 4k palabras de memoria OTP de programa. Posibilidad de direccionar hasta 64k palabras de datos externos en el ‘C16, 4k para los demás dispositivos. Unidad aritmético-lógica de 32 bits. 32 bits a la salida del multiplicador de la ALU (Dos entradas de 16 bits). Multiplicación en un solo ciclo de instrucción. Hasta 4 timers internos para el control de operaciones. Hasta ocho niveles de anidamiento en la pila hardware Dos registros auxiliares. 4 canales de entrada y de salida en el ‘C 14,’C15 y ‘C17. Registro de desplazamiento de 16 bit. Estados de espera para comunicación con memorias/periféricos externos más lentos. Damián Martínez Muñoz 9 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real En la siguiente figura se desglosan los diferentes miembros que componen esta familia. APLICACIONES EN TELECOMUNICACIÓN ‘C17 ‘C16 ‘C14 MÁS MEMORIA FUNCIONES DE CONTROL ‘C15 NÚCLEO DE LA GAMA ‘C1x ‘C10 BAJO COSTE FAMILIA TMS320C1x Damián Martínez Muñoz 10 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Como muestra, en la siguiente figura se representa el diagrama de bloques del TMS320C15 RAM de datos 256x16 ROM de programa 4kx16 A(11-0) D(15-0) Registro T de 16bit Registro de desplazamiento de 16 Multiplicador16x16 bits Registro P de 32 bit 8 Puertos E/S 16 bits ALU de 32 bits Shift L(0,1,4) 2 registros auxiliares Registro de estado Diagrama de bloques TMS320C15 2.2 Familia TMS320C2x Damián Martínez Muñoz 11 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Conforma la segunda generación de DSP’s de Texas Instruments. Su arquitectura interna amplía las posibilidades que ofrecía la primera generación. Al igual que ésta, sus miembros son de coma fija de 16 bits. Puntos destacados: • Diferentes configuraciones de memoria RAM, ROM ó OTP PROM interna para una mayor flexibilidad en el diseño. • Un gran gama de herramientas de desarrollo de desarrollo desde $99, desde módulos de inicio hasta emuladores en tiempo real. • Capacidad de integración a través del paquete cDSP. • Posibilidad de escoger entre 3 versiones (‘C25,’C26,’C28) para optimizar los costes del sistema. Aplicaciones Fundamentales: • • • • • • Sistema de frenos antideslizamiento. Servomecanismos y control de motores. Control de robots. Telecomunicaciones. Sistemas de sonido, procesamiento de voz. Aplicaciones de filtrado digital. Características : • • • • • • • • • • • • 544 palabras de memoria RAM interna de datos programable (incluida 256 de programa/datos). 1568 palabras de memoria RAM configurable entre programa/datos en el ‘C26. 4k palabras de ROM de programa interna para el ‘C25. Opciones con 4k palabras de memoria interna OTP ROM de programa. Capacidad de direccionamiento hasta un total de 128k palabras de memoria de datos/programa externa. ALU y acumulador de 32 bits. Multiplicador paralelo de 16x16 bits con resultado de 32 bits. Instrucciones de multiplicación/acumulación con un solo ciclo de instrucción. Mejora en las instrucciones repetitivas para conseguir un uso eficiente de la memoria de programa e incrementar la velocidad de ejecución. Instrucciones para desplazamiento de bloques de datos/programa para facilitar la gestión de programa. Timer interno para operaciones de control. Hasta 8 registros auxiliares. Damián Martínez Muñoz 12 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real En las dos siguientes figuras se representa el diagrama de bloques de esta familia de DSP’s. RAM de Datos B0 256x16 RAM D/P B1 256x16 ROM de Datos B2 256x16 ROM de Programa B2 256x16 A(15-0) D(15-0) CPU Registro de desplazamiento de 16 bits ( L) Puertos de E/S (16x16) Registro T de 16 bits ALU de 32 bits Acumulador de 32 bits ShiftL (0-7) 8 Registros Auxiliares 8 niveles de anidamiento pila Dos registros de estado Contador de repetición Contador Puerto serie síncrono Diagrama de bloques TMS320C2x Damián Martínez Muñoz 13 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Multiplicador/ALU TMS320C2x BUS DE PROGRAMA 16 16 16 Desplamiento izquierda 16 Registro T (16) 16 MUX 16 Multiplicador (16x16) 32 Registro P (32) 32 Desplazamiento izquierda (0-16) 32 32 MUX 32 32 Unidad Aritmético Lógica (ALU) 32 CC Registro Acumulador (32) 32 16 Desplazamiento Izquierda (0-7) Damián Martínez Muñoz 14 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 2.3 Familia TMS320C2xx Es también de coma fija de 16 bits e implementa diferentes mejoras a los de las generaciones anteriores. Puntos destacados: • • • • • • • • • Potencia computacional desde 20 hasta 40 MIPS. Precios a partir de $0.12 por MIPS. Versiones de 3, 3.3 y 5V. Consumo típico bajo: 1.9 mA/MIPS a 5V 1.1 mA/MIPS a 3 y 3.3V Encapsulado TQFP de 100 y 80 pines. Código fuente compatible con las generaciones ‘C1x y ‘C2x. Compatibilidad hacia arriba con la generación ‘C5x. Posibilidad de integración usando la librería cDSP. Posibilidad de emulación usando JTAG. Aplicaciones Fundamentales: • • • • • • • • • • Aplicaciones telefónicas. Terminales punto de venta. Sistemas de seguridad. Telecomunicaciones. Redes de comunicaciones. Servomecanismos y control de motores. Detectores Radar. Cámaras digitales. Modems. CD Roms. Características : • Hasta 4.5k de memoria RAM de datos/programa interna. • En algunas versiones hasta 32k palabras de memoria flash interna (‘F206/’F207). • 16 pines de E/S de propósito general. • ALU/acumulador de 32 bits. • Multiplicador paralelo de 16x16 bits con resultado de 32 bits. • Arquitectura optimizada para permitir que las instrucciones repetitivas se ejecuten de forma eficiente. • Timer interno de 16 bits. • Registro de desplazamiento de 16 bits. • 8 niveles de anidamiento en la pila. • Existe modo de bajo consumo. • El software permite generar estados de espera. Damián Martínez Muñoz 15 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Los TMS320C2xx abrieron nuevas vías a otras generaciones de DSPs (coma fija) Hicieron posible que los procesadores DSPs tuvieran nuevos campos de aplicación : ORDENADORES,INDUSTRIA, CONSUMO Y TELEFONÍA ‘ C54x Generación ‘ C5x Generación ‘ C2xx Generación ‘ C2x Generación Ordenador Industria Consumo Telefonía ‘ C1x Generación Damián Martínez Muñoz 16 Ing. Telecomunicación FLASH 32Kx16 ‘C24x 16Kx16 Sistemas de Procesado de Señal en Tiempo Real RAM (datos/Prog) doble-puerto 544x16 RAM(Datos/Prog) Acceso Simple 4Kx16 ROM 4Kx16 ‘C24x 16Kx16 Control de Emulación D(15-0) A(15-0) BUS DE DATOS/PROGRAMA Registro de Desplazamiento 16 bits (L) Registro T (16 b) Multiplicador (16x16) Desplazamiento (0,1,4-6) ALU (16 bits) ACUMULADOR (32 bits) FUENTE DE ALIMENTACIÓN DESPLAZAMIENTO L (0-7) 8 REGISTROS AUXILIARES 8 NIVELES DE PILA (HW) INSTRUCCIONES DE REPETICIÓN 2 REGISTROS DE ESTADO DIAGRAMA DE BLOQUES ‘C2xx Damián Martínez Muñoz B U S DE P E R I F E R I C O S PUERTO SERIE SINCRONO PUERTO SERIE ASINCRONO TEMPORIZADOR ESTADOS DE ESPERA (SW) PUERTOS DE E/S 10-Bits ADC1 10-bits ADC2 DETECTOR DE BAJO NIVEL WATCHDOG TIMER 17 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 2.4 Familia TMS320C3x Es la primera generación de DSP’s de Texas Instruments de coma flotante. La longitud de palabra es de 32 bit. Puntos destacados: • Potencia de cálculo de hasta 60 MFLOPS (millones de operaciones en coma flotante por segundo). • Alta eficiencia usando lenguaje C. • Gran espacio de direccionamiento: 16Mwords. • Gestión rápida de memoria con DMA interna. Aplicaciones Fundamentales: • • • • • • • • • Audio digital. Gráficos 3-D. Impresoras láser, fotocopiadoras, escáners. Escáners de código de barras. Video conferencia. Automatización industrial y robótica. Correo de voz y Faxs. Servomecanismos y control de motores. Redes de comunicaciones. Características : • Alta potencia de cálculo: Ciclos de instrucción de 33-ns. 30 MIPS. 60 MFLOPS. 330 MOPS. Ancho de banda E/S de 120 Mbytes/second. • CPU con arquitectura pipeline: Multiplicación paralela y operaciones aritmético/lógicas con números enteros o en coma flotante en un único chip. 8 registros con precisión extendida. • Potente juego de instrucciones: Ejecución de instrucciónes en un sólo ciclo. Control de sistema y operaciones numéricas. • Periféricos integrados: Controlador de DMA para E/S simultáneas y operaciones en la CPU. Temporizadores. Puertos serie. • Memoria: Paralelismo del bus para permitir desplazamiento rápido de datos. Damián Martínez Muñoz 18 Ing. Telecomunicación CACHE 64x32 Sistemas de Procesado de Señal en Tiempo Real RAM (Doble puerto) 1Kx32 256x32(‘C32) RAM (Doble puerto) 1Kx32 512x32(‘C32) ROM 4Kx32 (‘C30) Boot (‘C31/’C32) Puerto Principal Interfaz de Memoria Acceso de Datos 32 bits(‘C30-C31) 8/16/32 bits(‘C32) Acceso al programa 32 bits (‘C30-‘C31) (3)-D(31-0) 16/32 bits (‘C32) (4)-A(23-0) Reset Int3-0 Iack XfI-0 H1 H1 Mcbl/Mp X2/Clkin Vdd ,Vss Shz Emu6-0 X1 C o n t r o l a d o r CPU Multiplicador de enteros y coma flotante ALU de enteros y coma flotante 8 Registros de Precisión Coprocesador DMA DMA Canal 0 TCLK0 Timer 0 TCLK1 Timer 1 CLKX0 DX0 FSX0 CLKR0 DR0 FSR0 8 Registros Auxiliares Generación Direcciónes 0 Generación Direcciónes 1 DMA Canal 1 Puerto Serie 0 12 Registros de Control 2 Modelos de muy Bajo Consumo (‘C31-‘C32) Damián Martínez Muñoz CLKX1 DX1 FSX1 CLKR1 DR1 FSR1 Puerto Serie 1(‘C30) Diagrama de Bloques ‘C3x 19 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 2.5 Familia TMS320C4x Es también de coma flotante de 32 bits. Está pensada sobre todo para el procesamiento paralelo, por lo que cuenta con interfaz de comunicación muy rápidas. Puntos destacados: • • • • • Hasta 60 MFLOPS. Gran incremento de potencia de cálculo y de comunicaciones. Capacidad de multiproceso. Escalabilidad. Tolerante a fallos. Aplicaciones Fundamentales: • • • • • • • Comunicaciones de muy alta velocidad. Realidad virtual, simuladores. Procesamiento de rádar/sónar/imagen. Gráficos 3-D. Control de robots. Reconocimiento de voz. Infraestructura de telecomunicaciones. Características : • 6 puertos de comunicaciónes para comunicación entre procesadores a alta velocidad: Máxima velocidad de transferencia asíncrona de 32 Mbytes/s por cada puerto. Comunicación directa de procesador-procesador sin circuitería adicional. • Coprocesador DMA con 6 canales para E/S simultáneas y operaciones de la CPU. • Alta velocidad de la CPU del DSP capaz de 330 MOPS y 384 Mbytes/s: Hasta 11 operaciones por ciclo de instrucción. Ciclos de instrucción de 33, 40 y 50 ns. • Dos buses externos de direcciones y datos semejantes, permitiendo sistemas con memoria compartida y alta velocidad de transferencia de datos, transferencias en un único ciclo: Velocidad de transferencia de datos por un puerto de hasta 120 Mbytes/s (‘C40-60). Damián Martínez Muñoz 20 Ing. Telecomunicación UNIDADES DE PROCESO: Coprocesador DMA. CPU Alto Rendimiento. Sistemas de Procesado de Señal en Tiempo Real ENTRADAS/SALIDAS: Coprocesador DMA. Puertos de Comunicaciones. Buses locales y Globales Rendimiento del TMS320C4x Ciclo de instrucción 25 ns CPU 8OPS/Cycle 320 MOPS 2 Accesos de Datos 80 MOPS 1 Multiplicación FP 40 MOPS 1 Operación FP (ALU) 40 MOPS 1 Contador de bucle 40 MOPS 1 Búsqueda instrucción 40 MOPS 2 Registros de Direcciones 40 MOPS Coprocesador DMA 3 OPS/Ciclo 120 MOPS 1 Acceso de Datos 40 MOPS 1 Incremento del Contador de Transferencias 40 MOPS 1 Registro de Direcciónes 40 MOPS TOTAL MOPS = 440 MOPS Damián Martínez Muñoz TRANSFERENCIA DE DATOS Puerto Global 160 Mbytes/sec. Puerto Local 160 Mbytes/sec. 6 Puertos de Comunicaciones 192 Mbytes/sec. TOTAL E/S = 512 Mbytes/sec. 21 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 2.6 Familia TMS320C5x Vuelve a ser una familia de procesadores de coma fija de 16 bits. Puntos destacados: • • • • Potencia de cálculo de hasta 50 MIPS. Precios de venta desde $0.30 por MIP. Versiones de 3 y 5V. Diferentes versiones de encapsulado: 100 pins TQFP/PQFP, 128 pins TQFP, 132 pins PQFP y 144 pins TQFP. • Diferentes versiones de memoria RAM y ROM integradas. • Emulación JTAG • Compatible con ‘C1x, ‘C2x y ‘C2xx. Aplicaciones Fundamentales: • • • • • • • Teléfonos inalámbricos y móviles. Módems de alta velocidad. Comunicaciones personales. Sistemas de sonido y procesamiento de voz. Impresoras láser, fotocopiadoras. Otras aplicaciones de telecomunicación. Multimedia. • Control de discos duros. Características : • • • • • • • • • El ciclo de instrucción del DSP ‘C5x es de 20 ns. Potencia de procesamiento de 50 MIPS. Consumos a razón de 1.15mA/MIPS. Disponibles diferentes configuraciones de memoria RAM y ROM interna. Emulación on-chip, eliminando los retardos de propagación asociados a las antiguas tecnologías de emulación. Código fuente compatible con el ‘C1x, ‘C2x y ‘C2xx. Proporciona un tratamiento de bit a alta velocidad sin tener que modificar los bits de estado de la ALU ó registros. Permite, sin lógica adicional, la conexión de memoria externa lenta y dispositivos de entrada/salida, reduciendo costes. Los 12 registros más fundamentales de la CPU están duplicados. Damián Martínez Muñoz 22 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real RAM (Datos/Prog) ROM 10Kx16 (‘C50),2Kx16 (‘C51) 1Kx16(‘C52),4Kx16(‘C53,C53S) 7Kx16 (‘LC56,’LC57,’LC57S) 2Kx16 Boot (‘C50.’C57S) 8Kx16 prog.(‘C51),4Kx16 prog. (‘C52),16Kx16.(‘C53,’C53S), 32Kx16 (‘LC56,’LC57) Control de Emulación D(15-0) A(15-0) BUS DE DATOS/PROGRAMA Registro de Desplazamiento (Pre-Post) Multiplicador (16x16) Desplazamiento (ACC,PROD) ALU (32 bits) FUENTE DE ALIMENTACIÓN PPL PLU DESPLAZAMIENTO (0-7) 8 REGISTROS AUXILIARES 8 NIVELES DE PILA (HW) 32 bits ACC & 32 bits ACC buffer REGISTROS DE ESTADO DIAGRAMA DE BLOQUES ‘C5x Damián Martínez Muñoz B U S DE P E R I F E R I C O S PUERTO SERIE 1 PUERTO SERIE 2** TIMERS ESTADOS DE ESPERA (SW) PUERTOS DE E/S INTERFAZ DEL PUERTO HOST* * Disponible en ‘LC57 y ‘LC57S ** Un puerto serie en ‘C52, puertos serie con buffer en ‘LC56, ‘LC57 y ’LC57S 23 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 2.7 Familia TMS320C54x También es de coma fija. Son más rápidos que la familia ‘C5x. Puntos destacados: • • • • • • • Hasta 66 MIPS. Operación Viterbi integrada. Tres modos de bajo consumo. Diferentes configuraciones de RAM y ROM internas. Puerto serie con auto-buffer. Interfaz puerto host. Encapsulado ultra pequeño (100, 128 y 144 pins TQFPs). Aplicaciones Fundamentales: • • • • • • Comunicaciones digitales móviles. Sistemas personales de comunicación. Módems. Telecomunicaciones avanzadas. Comunicaciones digitales inalámbricas. Envío de datos en sistemas móviles. Características : • 66 MIPS. • Acelerador Viterbi integrado. • Opera a 2.7 y 5V. • Direcciones de 40 bits y dos acumuladores de 40 bits para la ejecución de operaciones en paralelo. • ALU de 40 bits configurable como dos de 16 con capacidad de realizar dos operaciones en un único ciclo. • Multiplicador 17x17 que permite las operaciones con enteros con y sin signo. • 4 buses internos y dos generadores de direcciones que permiten realizar diferentes operaciones y facilitan el acceso a memoria. • 8 registros auxiliares. • Dispone como herramienta del compilador de c para DSP de coma fija más avanzado del sector. • Modos de bajo consumo para aplicaciones en que se usan baterías. Damián Martínez Muñoz 24 Ing. Telecomunicación ROM(Datos/Prog) Sistemas de Procesado de Señal en Tiempo Real RAM(Datos/Prog) Control de Emulación D(15-0) A(15-0) FUENTE DE ALIMENTACIÓN BUS DE DATOS/PROGRAMA MAC 17x17 MPY RND SAT SUMADOR 40 BIT ALU ALU 40 BIT OPERAC. CMPS CODIF. EXPONENCIAL DESPLAZAMIENTO 40 BITS ( 16 31) ACUMULADORES 40 BITS ACC A 40 BITS ACC B UNIDAD DE DIRECCIONAMIENTO 8 REGISTROS AUXILIARES 2 UNIDADES DE DIRECCIONAMIENTO DIAGRAMA DE BLOQUES ‘C54x Damián Martínez Muñoz B U S DE P E R I F E R I C O S PUERTO SERIE PUERTO SERIE TDM TIMER GENERADOR DE RELOG(PLL) GENERADOR SW DE ESTADOS DE ESPERA INTERFAZ DE PUERTO HOST PUERTO SERIE CON BUFFER 25 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real SECCION ANALOGICA EN BB SECCION DIGITAL EN BB Interfaz de AUDIO Interfaz TMS320C54x DSP RF Codif./Decodif de VOZ Corrección de Errores Codif/Decodif de CANAL Ecualización Demodulación Encriptación Microcontrolador INTERFAZ HOMBRE/MAQUINA ANTENA TRANSMISIÓN y RECEPCIÓN en RF SPEAKER MICRO PANTALLA TECLADO TARJETA SIM SOLUCIÓN PARA UN TELEFONO MOVIL DIGITAL Damián Martínez Muñoz 26 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 2.8 Familia TMS320C8x Integra varias unidades de proceso en el mismo encapsulado. Estas unidades de proceso son de coma fija de 16 bits. Puntos destacados: • Arquitectura de ‘C8x : Arquitectura MIMD (Múltiple instrucción - Múltiple dato) totalmente programable. Instrucciones avanzadas de DSP. Procesador principal RISC de 32 bit. Controlador de transferencia. Velocidad de transferencia de hasta 400 Mbytes/sec. Capacidad de direccionamiento hasta 4 Gbytes. Ciclos de instrucción de 17, 20 y 25 ns. • TMS320C80 : Controlador de vídeo. 4 DSPs trabajando en paralelo. 50 kbytes de RAM interna. 2 BOPS. Encapsulados 305 pins PGA, 352 BGA. • TMS320C82 : 2 DSPs trabajando en paralelo. 44 kbytes de RAM interna. 1.5 BOPS. Encapsulado 352 BGA. Aplicaciones Fundamentales: • • • • • • • • • Vídeo conferencia. Vídeo teléfonos. Telecomunicaciones a alta velocidad. Procesamiento de imagen y vídeo. Estaciones de trabajo multimedia. Aceleradores de gráficos 2-D y 3-D. Realidad virtual. Seguridad. Sistemas de rádar y sónar. Características : • • • • • Controlador inteligente de transferencia interno y memoria (SRAM). Procesamiento paralelo múltiple de 32 bit. La ALU de 32 bit puede ser configurada como 2 de 16 bits ó 4 de 8 bits para proceso paralelo de datos con baja precisión. Interfaz directa con DRAM, SRAM y VRAM. Interfaz de bus externo dinámico de 8, 16, 32 y 64 bit. Damián Martínez Muñoz 27 Ing. Telecomunicación PALETA DE PANTALLA Sistemas de Procesado de Señal en Tiempo Real V R A M D R A M TMS320C80 CAPTURA DE VIDEO CONTROL CODIFICADOR DE AUDIO ( 16 Bits) DE MEMORIA PCI I/F CHIP XDS EN TARJETA TARJETA DE DESARROLLO DE SW DEL TMS320C8x Damián Martínez Muñoz 28 Ing. Telecomunicación DSP AVANZADO G L I Sistemas de Procesado de Señal en Tiempo Real DSP AVANZADO G L I DSP AVANZADO G L I DSP AVANZADO G L I RISC MP 64 32 32 64 32 32 64 32 32 64 32 32 FLU CONTROLADORES DE VIDEO CAPTURA VIDEO 32 64 64 CROSSBAR 50 Kbytes SRAM - TMS320C80 44 Kbytes SRAM -TMS320C82 Damián Martínez Muñoz R E L O J E S 64 CONTROLADOR DE TRANSFERENCIA 29 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 2.9 Familia TMS320AVxxx (DCP) Están orientados a una aplicación determinada. Está compuesta por varios miembros. Puntos destacados TMS320AV110 (Decodificador de audio MPEG): • • • Decodificador de audio ISO-MPEG en un único chip. Decodifica los modos mono, estéreo, dual y joint stereo. Soporta todas las frecuencias de muestreo y bit rates de MPEG, incluido el formato libre. • Acepta entrada de datos a ráfagas hasta una velocidad de 15 Mbits/s. • Encapsulado pequeño de 120-pins plastic quad flat package (PQFP). Puntos destacados TMS320AV120 (Decodificador de audio MPEG): • • • • No requiere un microprocesador host para inicialización y operación. Acepta SCR y PTS de audio y proporciona sincronización automática. Proporciona información de estado al inicio de cada trama. Encapsulado PLCC de 44 pins de bajo coste. Puntos destacados TMS320AV220 (Decodificador de vídeo MPEG): • Interfaz directa con el decodificador de audio MPEG ‘AV110 y el codificador NTSC ‘AV120. • Sistema decodificador integrado con buffer para entrada de audio. • Sincronización automática de audio y vídeo sin necesidad de lógica externa. • Soporta formatos de salida de vídeo NTSC y PAL. • Soporta resolución SIF y CCI R 601. Puntos destacados TMS320AV420 (Codificador digital NTSC): • • • • • • Codificador digital NTSC en un único chip. Interpolación de línea vertical para MPEG-1 de vídeo. Entrada : RGB, YUV 4:4:4 ó YUV 4:2:2. Salida s-vídeo (C e Y). Circuito interno para generación de señal de sincronismo. Encapsulado 80 pins quad flat package. Damián Martínez Muñoz 30 Ing. Telecomunicación DECODIFICADOR DE AUDIO MPEG ‘AV120 Proporciona un coste bajo para la implementación de algoritmos de codificación de audio MPEG ( Layers 1 y 2 ) DECODIFICADOR DE VIDEO CD MPEG ‘AV220 Basado en el decodificador de video CL450 de C’Cube con características especificas para Video CD integradas . DECODIFICADOR DE VIDEO CD MPEG ‘AV220 Convierte las secuencias de bits de salida , RGB or YUV del ‘AV220 a una señal analógica NTSC para TV . Damián Martínez Muñoz Sistemas de Procesado de Señal en Tiempo Real • Arquitectura matemáticamente modelada para minimizar el silicio usado y maximizar la calidad de audio. • La calidad CD es mantenida sin ninguna cuantificación adicional. • También puede ser usado como un decodificador de audio MPEG sin necesidad de un procesador host. *Derivado del TMS320AV110 MPEG decodificador de Audio y optimizado para reducir el coste de las aplicaciones de video CD. CHIPSET VIDEO CD • Integra decodificador de sistema MPEG1,buffer para audio y microcódigo interno. • Sincronización de las salidas de audio y video sin un host externo. • Integra funciones de control de Video CD (vista rápida, reverse , elección de pista ...). • Proporciona una interfaz para decodificadores de CDROM SONY y SANYO. • Verticalmente se interpolan las lineas para crear la imagen reduciendo el ruido • Genera señales de sincronización para el decodificador de video ‘AV220. • Soporte Overlays, proporcionando la capacidad de superponer textos y gráficos en la pantalla de vídeo. UN CHIPSET VERSATIL Y OPTIMIZADO 31 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real MOTOROLA Damián Martínez Muñoz 32 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 3 DSP’s de Motorola Motorola, aunque entró a competir en el mercado de los DSP’s relativamente tarde (1987), ha conseguido tener un peso relativamente importante en este mercado. El primer DSP que sacó a mercado (DSP56000/56001) era de coma fija pero de 24 bits. Este valor de precisión ocupa un valor intermedio ocupa un valor intermedio entre la precisión que aporta la coma fija de 16 bits con la coma flotante de 32 bits. Este DSP desde su aparición tuvo una elevada aceptación sobre todo en lo que se refiere a aplicaciones con audio. Actualmente la familia de DSP’s que Motorola ofrece son: • Familia de coma fija de 16 bits (DSP561xx) • Familia de coma fija de 24 bits (DSP5600x) • Familia de coma flotante de 32 bits (DSP96002) A continuación vamos a ver una a una estas familias de DSP’s. 3.1 Familia DSP561xx La arquitectura de los DSP561xx fueron está basada en la arquitectura del DSP56000, añadiendo un codec para conversiones D/A y A/D con ancho de banda vocal para aplicaciones de telefonía móvil digital y comunicaciones de voz. El DSP561xx realiza en un ciclo de instrucción, dos ciclos de reloj, la operación de multiplicación-acumulación (MAC) y facilita la realización de sumas de productos y procesamiento de vectores. La unidad aritmético lógica (ALU) consta de dos acumuladores de 40 bits incluyendo 8 para extensión de signo, con 4 registros de entrada de 16 bits para conservar ciertas variables y coeficientes. Los registros de entrada, para una instrucción MAC deben cargarse al mismo tiempo que la instrucción MAC anterior. Se pueden cargar los registros de entrada a la operación MAC en paralelo con la operación MAC anterior. Cuando almacenamos el resultado en 16 bits de memoria, ocasionalmente el circuito limitador satura los valores del acumulador de 40 bits a +1.0 y -1.0 que son los valores más grandes que puede tomar. El DSP561xx tiene RAM de programa y memoria RAM de datos de doble puerto interna; cada una tiene su propio bus de direcciones y de datos. La RAM de datos de doble puerto permite al generador de direcciones entregar dos direcciones por ciclo, permitiendo dos lecturas o una lectura y una escritura. El generador de direcciones tiene 12 registros de 16 bits, tales como de direcciones de offset y de modificación, que permiten implementar diferentes tipos de direccionamiento. El centro del DSP561xx puede acceder a los registros generadores de direcciones a través de un bus global de datos que une a estos registros con la memoria externa, periféricos, y una unidad funcional para la manipulación de bits. El bus externo de 16 bits del chip multiplexa entre 64 Kbytes de programa y momoria de datos. La CPU puede realizar un acceso a memoria externa en un sólo ciclo de instrucción. Cuando se usa una memoria lenta, el chip puede necesitar estados de espera, controlados mediante programación. Con un reloj externo a 60 MHz y un ciclo de instrucción básico a 30 MHz, un acceso desde memoria a la CPU debe tardar menos de 33 nanosegundos. El DSP561xx tiene dos buses de dirección de memoria de datos Damián Martínez Muñoz 33 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real que acceden a la memoria de datos RAM X, y a la memoria externa para los valores de la memoria Y. Modos de direccionamiento. El DSP561xx soporta direccionamiento directo, indirecto (postincremento /decremento por 1 u offset e indexado con offset) y direccionamiento inmediato. El generador de direcciones también soporta direccionamiento circular y bit reverse (útil para hacer la FFT). Instrucciones especiales. El DSP561xx proporciona instrucciones para realizar bucles tales como “do” y “repeat”; solamente los bloques que se repiten usando la instrucción “do” son interrumpibles. Soporte. Motorola vende el Sistema para Desarrollo de Aplicaciones con operaciones de emulación in-circuit usando las características de emulación on-chip de los DSPs. El emulador on-chip permite puntos de ruptura fijos, ejecución paso a paso, y la lectura/modificación de memoria ó registros. Motorola proporciona un compilador de C Gnu, un debuger, un linkador/ensamblador y un simulador. 3.2 Familia DSP5600x Es un DSP de coma fija de 24 bits. Presenta tres bancos de memoria: uno de programa y dos de memoria de datos (X e Y). Como la mayoría de otros DSP’s, el DSP5600 tiene un bus de memoria externa versátil, capacidad de manipulación de bits y es posible ejecutar desde memoria externa usando un único ciclo de instrucción. El chip no tiene memoria ROM de programa interna, salvo un pequeño program de arranque en algunas versiones. Por contra, el DSP56000 puede acceder a memoria externa en cada ciclo de instrucción sin penalización temporal. En el sentido tradicional, el DSP56000 es una maquina basada en acumulador debido a que las operaciones lógicas y matemáticas se hacen a través de un acumulador. Sin embargo, la arquitectura hace posible la manipulación de bits en registros y en memoria. Tiene una unidad MAC que opera usando un solo ciclo de instrucción; la unidad tiene dos acumuladores de 56 bits (8 bits para extensión de signo); dos conjuntos de registros de 24 bits abastecen la unidad. Antes de que se usen los datos debemos cargarlos dentro de los registros MAC. MAC sólo emplea un ciclo de instrucción (dos ciclos de reloj) para multiplicar y acumular. Otros registros son los registros de direccionamiento y control. Como muchos otros DSP’s, el DSP56000 tiene dos generadores de direcciones similares que acceden a las memorias X e Y para los ciclos MAC. Cada generador de direcciones tiene una ULA de 16 bits y 4 conjuntos de 3 registros: 4 registros de puntero que llevan asociados, cada uno, registros de offset y de modificación. Los registros de modificación pueden especificar el tipo de operaciones aritméticas de dirección del registro, o pueden contener datos. Los registros de modificación soportan un buffer FIFO y direccionamiento bit reverse. El procesador combina direccionamiento de 16 bits con palabras de 24, tiene tres pares de buses de datos y direcciones internos, que permiten acceder a la siguiente instrucción y 2 accesos de datos en un solo ciclo y, por lo tanto, evitar la necesidad de Damián Martínez Muñoz 34 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real una memoria caché interna. Un cuarto bus , el bus global de datos, es un bus lógico simple de 24 bits que transfiere datos hacia y desde periféricos “on-chip”. Podemos cambiar cualquiera de las posiciones de memoria internas y externas de 16 bits y los buses de datos de 24. Cuando el DSP56000 almacena valores de 56 bits en registros de memoria de 24 podemos desplegar una operación de desplazamiento de un bit y saturar el valor a ±1.0. A diferencia de otros DSPs, las memorias X e Y del DSP56000 tienen sus propios espacios de memoria, los cuales incluyen RAM “on-chip” y ROM para las direcciones superiores. Una unidad de intercambio de bus interno gestiona las transferencias entre los buses internos y el único bus externo. La unidad de manipulación de bits ejecuta operaciones de bits en posiciones de memoria y registros de datos, de control y de direcciones. Modos de direccionamiento. El 56000 soporta direccionamiento directo a registro, directo a memoria, indirecto a registro, inmediato, y bit reverse. Instrucciones especiales. El 56000 ejecuta bloques do/end-do, manipulaciones de bit, comparación, división, saltos si el bit está activo/inactivo, saltos incondicionales a subrutinas y movimiento de memoria de programa. Ejecuta operaciones lógicas sólo desde el bit 24 al 47 del acumulador; estos bits representan la parte más significativa de los datos. Soporte. Motorola ofrece varias placas de evaluación del DSP5600x de bajo coste ; también un sistema de desarrollo y aplicación a 40 MHz. Otras herramientas hardware también están disponibles. El DSP56000 usa una interfaz de debug propia, On Chip Emulator (OnCE), en lugar del interfaz estándar JTAG. Motorola aporta un compilador Gnu y un debugger, un ensamblador-linkador y un simulador. Otros fabricantes proporcionan paquetes de adquisición de datos y de diseño de filtros así como software OS. 3.3 DSP96002 El DSP96002 de Motorola es básicamente una extensión a 32 bits en coma flotante del DSP56000 de coma fija de 24 bits. El 96002 tiene 5 buses internos para acelerar el procesamiento de operaciones múltiples. Estos buses incluyen un conjunto de buses de memoria X e Y y de programa. También incluye un bus de datos global para transferir direcciones y datos locales, y también un bus DMA que soporta dos canales DMA. El controlador DMA “on-chip” mueve datos sin interrumpir la ejecución de instrucciones en el DSP. El DSP96002 tiene también dos interfaces de bus externos de 32 bits con soporte de modo paginado DRAM. Estas interfaces externas tienen capacidad multimaster incorporada. Otros DSPs 96002 o un procesador host puede realizar una petición del bus y controlar el bus y usarlo para acceder a la memoria externa compartida o a la memoria interna del 96002. El DSP96002 de Motorola presenta un modelo de programación casi idéntico al del anterior procesador DSP56000 de coma fija de 24 bits. Los ingenieros de Motorola ampliaron el conjunto de instrucciones con instrucciones de coma flotante y extendieron los registros incluyendo los de direccionamiento desde 16 a 32 bits. Damián Martínez Muñoz 35 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Al igual que el DSP56000, el 96002 tiene memoria RAM X e Y y bloques de ROM para proporcionar los coeficientes y variables de los cálculos de multiplicaciónacumulación (MAC) para suma de productos. Las operaciones MAC toman los operandos de entrada de los registros de la ALU (como en el DSP56000) La unidad de ejecución incluye un multiplicador separado y un sumador-restador que controla estas operaciones para los cálculos de FFT , una unidad lógica y un registro de desplazamiento. Estas unidades soportan operaciones con enteros y en coma flotante con exponentes de 11 bits y mantisas de 32. El DSP96002 cumple el estándar IEEE para representaciones de coma flotante de precisión doble y simple. El DSP96002 tiene esencialmente la misma unidad de generación de direcciones que el anterior DSP56000. Esta unidad comprende dos generadores de direcciones que pueden operar a la vez. Cada generador tiene tres conjuntos de 4 registros de 32 bits: direcciones (punteros de dirección), desplazamiento (valores offset) y registros de modificación. Podemos cargar y acceder a estos registros mediante el bus de datos global. El DSP96002 tiene una arquitectura flexible. El DSP soporta una mezcla de espacios de memoria extendidos desde un espacio de direcciones único y unificado a otro con espacios de 32 bits separados para X e Y y memoria de programa. Modos de direccionamiento. El DSP96002 soporta direccionamiento de registro directo, directo a memoria, registro indirecto e inmediato. El generador de direcciones también soporta direccionamiento módulo (para buffers circulares) y bit reverse. Instrucciones especiales. El DSP96002 soporta bucles hardware con bloques repeat, test y cambio de bit, comparación de gráficos, llamadas condicionales a subrutinas y estados, conversiones de entero a coma flotante y viceversa. El DSP96002 no soporta instrucciones de ejecución condicionales. Soporte. Módulo de desarrollo de aplicaciones para evaluaciones y debugging del DSP96002. El módulo usa el soporte de emulación “on-chip” (ONCE) del procesador para establecer puntos de ruptura, ejecuciones paso a paso de la CPU y leer/modificar memoria o registros. No provee soporte JTAG. Podemos configurar el chip para que trabaje con RAM externa para desarrollo. Motorola proporciona un compilador C Gnu y herramientas, también un linkador/ensamblador, librerías y un simulador de comportamiento. Otras compañías ofrecen otras herramientas que incluyen compiladores ADA y C, sistemas de desarrollo para gráficos, software de diseño de filtros y tiempo real OS. Damián Martínez Muñoz 36 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real ANALOG DEVICES Damián Martínez Muñoz 37 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 4.1 Familia ADSP-2100 Los DSP’s de la familia ADSP-2100 proporcionan un juego de instrucciones que requieren un único ciclo de instrucción cuando se implementan algoritmos de DSP. El procesador puede realizar varias operaciones por ciclo. La unidad multiplicadoracumulador (MAC), la ALU y los registros de desplazamiento están separados pero no pueden trabajar en paralelo. Otros registros secundarios siguen cada ejecución de los registros de unidad, permitiendo un rápido cambio de contexto para el procesamiento de instrucciones. Si necesitamos precisión extendida podemos usar el acumulador de 40 bits de la unidad MAC (incluidos los 8 bits para extensión de signo) como dos registros de 16 bits y uno de ocho, y copiar individualmente la información que contienen en otros registros. El registro de desplazamiento mueve una entrada de 16 bits a la izquierda o la derecha dentro de un registro de 32. El hardware también permite la detección de exponente y normalización de bloques en coma flotante para incrementar la precisión del DSP de 16 bits. Una aplicación usa el registro de desplazamiento para conversiones entre números en coma fija y en coma flotante. Los miembros de la familia ADSP-2100 tienen generadores de direcciones X e Y y buses de datos y programa. Cuando en la ejecución utilizamos memoria interna, los buses facilitan los datos X e Y para cada ciclo de MAC. También podemos usar la memoria del programa como memoria de datos para almacenar constantes durante la realización de la instrucción MAC. La memoria de programa de doble puerto permite dos accesos a memoria en un solo ciclo. Para accesos a la memoria externa, el ADSP-2100 tiene un generador de estados de espera programable desde 0 hasta 7 estados posibles. Los diseñadores de Analog Devices optaron por una palabra de datos de 16 bits y una palabra de instrucción de 24. El tamaño de la palabra de instrucción permite al dispositivo usar más instrucciones complejas y ofrece mayor flexibilidad que la que da un código de operación de 16 bits. La diferencia entre el tamaño de la palabra de código y la palabra de datos requiere una arquitectura Harvard con dos espacios de memoria. Estas arquitecturas, con espacios de memoria separados, son frecuentes en la mayoría de los DSPs, permitiendo realizar instrucciones en paralelo con operaciones de ciclo único MAC. Para diseños con memoria externa, los diferentes anchos de memoria conllevan que si se distribuye la memoria de datos y de programa en tres chips de memoria de 8 bits de palabra perderemos uno de cada 3 bytes en el área de memoria de datos. Modo de direccionamiento : Los ADSP-2100 permiten direccionamiento inmediato, directo, indirecto e indexado. Cada generador de direcciones soporta como máximo 4 buffers circulares con 3 registros cada uno. Los registros definen el final, la longitud y las direcciones de acceso. Un generador de direcciones proporciona direccionamiento bit reverse sólo para datos. Instrucciones especiales : El ADSP-2100 puede ejecutar condicionalmente la mayoría de las instrucciones. El comando do-until establece una secuencia de instrucciones que pueden ser de longitud arbitraria. Debido a que el ADSP-2100 es un dispositivo ‘nonpipelinned’ no incurre en penalizaciones por ejecutar saltos y llamadas a subrutinas. Soporte : Analog Devices proporciona un compilador ANSI C, un ensamblador, un linkador y un simulador interactivo. Las tarjetas de evaluación están disponibles para la mayoría de los DSP’s de esta familia. Los emuladores en circuito están disponibles para el debug de tarjetas hardware. Damián Martínez Muñoz 38 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real 4.2 Familia ADSP-21cspxx Analog Devices basa el ADSP-21cspxx de coma fija de 16 bits en los 21xx. Los 21cspxx pueden realizar un procesamiento de señal concurrente. Para facilitar su programación en C, el ADSP-21cspxx tiene un rango de direccionamiento de 16 M palabras y 48 registros de datos internos para el almacenamiento de las variables locales, computación y generación de direcciones de datos. Para el acceso múltiple de señales en tiempo real, 48 registros adicionales permiten al DSP conmutar tareas en un ciclo de reloj. Estos registros ocultos favorecen aplicaciones que ejecutan algoritmos con dos secuencias de datos diferentes. El corazón de los ADSP-21cspxx es un direccionador-procesador-decodificador, que realiza todo el proceso en un solo ciclo, después de que la instrucción direccionada es cargada. Una unidad acumulador-multiplicador de 16x16 bits (MAC) utiliza dos acumuladores de 40 bits que reducen los problemas asociados a un acumulador único. El segundo acumulador tiene un registro de salida compartido con el registro de desplazamiento de 40 bits del DSP. Aunque el ADSP-21cspxx tiene buses de datos de 16 bits, el dispositivo usa palabras de instrucción de 24. Este ancho de palabra permite soportar más operaciones por instrucciones y proporciona mayor flexibilidad en los mecanismos de direccionamiento. El DSP presenta una arquitectura von Neumann de bus doble. Los dos buses permiten obtener datos simultáneamente del espacio de memoria unificado del ADSP-21csp01. Dos generadores de direcciones de datos (DAGs) soportan cada uno cuatro buffers circulares simultáneos. Los DAGs tienen registros base que permiten a un programador situar los buffers circulares en cualquier lugar de la memoria. Los DAGs pueden acceder como máximo a 16 M de palabras de memoria. Un generador de direcciones proporciona un direccionamiento de bit reverse para datos exclusivamente . El ADSP-21csp01 contiene dos puertos serie bidireccionales que se pueden programar para obtener canales múltiples y para transferir datos a 25 Mbps. Un puerto DMA de 16 bits hace de interfaz del dispositivo con otros procesadores y buses del sistema. Un controlador DMA permite al dispositivo transferir datos hacia y desde cada puerto serie y también hacia y desde el puerto DMA sin interrumpir al procesador. Modos de direccionamiento. El ADSP-21csp01 permite direccionamiento inmediato, con registro directo a memoria y con registro indirecto. Instrucciones especiales. Tienen un carácter más ortogonal que las del 21xx. El ADSP-21csp01 puede ejecutar condicionalmente más instrucciones. Un comando do-until establece una secuencia de instrucciones para cada operación. Soporte. Las herramientas de desarrollo incluyen un linkador, un simulador y un compilador C integrado dentro de un entorno de diseño basado en Windows. La compañía también ofrece un emulador in-circuit, EZ-ICE, que usa el interfaz JTAG para monitorizar y controlar el procesador de la tarjeta en cuestión. Analog Devices también proporciona una librería en tiempo real DSP. 4.3 Familia ADSP-21020 Damián Martínez Muñoz 39 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real El ADSP-21020 proporciona los cimientos para el SHARC DSP de Analog Devices. Como los anteriores DSPs de Analog, el ASDP-21020 utiliza palabras de instrucción de 48 bits para codificar múltiples operaciones por instrucción. La instrucción más compleja puede ejecutar 3 cálculos, 2 desplazamientos de datos y la actualización de 2 punteros en un solo ciclo. Sin embargo, tenemos la desventaja de que las palabras de instrucción extensas aumentan el coste del sistema; el 21020 necesita acceder a memorias externas dobles. La arquitectura Harvard del chip soporta 2 generadores de direcciones de datos (DAGs) y 2 buses externos con estados de espera programables: un bus de instrucción de 48 bits y otro de datos de 40 bits con 24 y 32 bits de direccionamiento respectivamente. El 21020 carece de memoria de programa y de datos on-chip. Sin embargo, la CPU lleva a cabo instrucciones de acumular-multiplicar (MAC) en un único ciclo de intrucción mediante la ejecución de instrucciones posicionadas en la memoria caché on-chip de 32 palabras del 21020 y obteniendo los coeficientes y los datos desde memoria externa. A diferencia de los DSPs anteriores, el ADSP-21020 no es un diseño basado en acumulador. Las operaciones se centran en una matriz de 32x40 bits, 10 puertos de registro de fichero que soportan múltiples acumuladores y registros permitiendo más flexibilidad para la compilación en C y el ensamblado de programas. Los registros de datos soportan formatos de coma fija y coma flotante, dependiendo de cómo la instrucción haga referencia a ellos. El 21020 tiene 10 puertos con sólo 9 activos en un ciclo, que enlazan las tres unidades computacionales DSP y los buses de datos y de programa al fichero de registro. Para un mayor cambio de contexto, el DSP oculta éste fichero de registro y todos los registros DAG. Las tres unidades computacionales del ADSP-21020 comprenden un multiplicador de coma flotante con dos acumuladores de coma fija; un registro de desplazamiento de 32 bits; y una ALU que ejecuta operaciones matemáticas tanto coma fija y coma flotante. Los acumuladores de 80 bits proporcionan 16 bits de cabecera para la expansión de bit, que es especialmente útil para largas cadenas MAC. Las tres unidades pueden operar en paralelo, cada una con entradas y salidas al fichero de registro. Las operaciones son concurrentes, a menos que se produzca un conflicto como cuando dos unidades acceden al mismo registro. Cada unidad funcional trabaja en un sólo ciclo de reloj. El registro de indicadores de la ALU retiene los resultados de 8 operaciones de comparación de la ALU. Los bits del registro de indicadores forman un registro de desplazamiento a la derecha. Cuando el procesador ejecuta una operación de comparación de la ALU, estos bits se desplazan hacia el menos significativo. Los dos DAGs del 21020 acceden a las zonas de datos X e Y. Cada generador de direcciones posee 8 conjuntos de registros que soportan 16 bufferes circulares simultáneos; cada conjunto de registros abarca el índice, modificación, base y longitud de los registros. Los bufferes circulares pueden residir en cualquier dirección de memoria y su longitud puede ser arbitraria y son esenciales para la gestión de lineas de retardo y de datos en transformadas en el dominio del tiempo y la frecuencia. El 21020 minimiza el uso de los estados de programa ofreciendo ejecuciones condicionales de la mayoría de las instrucciones: la instrucción utiliza un test de condición preliminar y si ésta es positiva se ejecuta la instrucción. Damián Martínez Muñoz 40 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Modos de direccionamiento. Inmediato con 32 bits, indexado, de bit-reverse, módulo-circular, por registro directo y direccionamiento indirecto. Sin embargo, debemos usar direccionamiento indirecto para acceder a memoria externa. Instrucciones especiales. El 21020 desarrolla manipulaciones de bit, iteraciones de división, llamadas a subrutinas condicionales, bucles de una única instrucción o un bloque de instrucciones, comparaciones en coma fija y coma flotante y ejecuciones condicionales. El ADSP-21020 soporta la IEEE-754 de coma flotante (23 bits de datos, 8 de exponente y uno de signo). También soporta formatos de coma fija, fraccionaria y entera (sin signo o en complemento a dos) de 32 bit. Son posibles 6 niveles de anidación de interrupciones. Soporte. Analog Devices proporciona un conjunto de utilidades que incluyen un compilador de ANSI C, un compilador de C con extensiones numéricas C para cálculos matemáticos y aplicaciones en coma flotante, un debugger fuente, un linkador-ensamblador, un simulador, librerías de aplicaciones y un divisor PROM. Analog Devices ofrece un emulador en circuito de gran velocidad. También tiene licenciado el ADSP-21020 a Temics Semiconductors (SantaClara, CA). 4.4 Familia SHARC (ADSP-2106x) Además de las características de la arquitectura del ADSP-21020, el computador de arquitectura Super Harvard (SHARC) de coma fija y coma flotante, ó ADSP-2106x, integra una gran memoria on-chip y un controlador de E/S para descargar los procesos de E/S de datos. Los chips SHARC tienen dos puertos serie de alta velocidad y un puerto paralelo/host. Ambos hacen posible una interfaz directa a memoria externa, periféricos y procesador host, facilitando la interconexión de hasta 6 ADSP-2106x. La CPU del ADSP-2106x trabaja usando memoria externa o interna del chip para una amplia gama de aplicaciones. Algunos chips SHARC contienen 512 Kbytes de memoria on-chip distribuidos en 2 bancos de memoria RAM de doble puerto. Ésta RAM permite accesos a memoria en un único ciclo de instrucción. Podemos usar esta memoria para almacenar una combinación de 16, 32 ó 40 bits de datos o instrucciones de 48 bits y realizar hasta 4 accesos por ciclo: memoria de programa para código de operación y datos, memoria de datos para los datos y una carga desde memoria externa usando el procesador de E/S del chip. SHARC incluye un controlador de E/S que realiza transferencias en paralelo con la realización de operaciones en la CPU. El controlador de E/S descarga la lectura y escritura entre memoria interna y externa, pero aparecen retardos cuando los accesos se realizan a una misma dirección de memoria. El controlador administra 10 canales DMA, transfiriendo datos dentro de la memoria interna, dispositivos periféricos externos, y el host, 2 puertos serie y 6 puertos de enlace. Todas las operaciones DMA son transferencias de datos sin penalización en tiempo que generalmente no producen interrupción. El controlador de DMA nos permite el control dinámico del ancho del bus de memoria externa. Los puertos serie síncronos pueden transferir datos a velocidades de hasta 40 Mbps; los 6 puertos de comunicaciones pueden transferir datos tan rápido como un byte por ciclo de reloj. Con 6 enlaces operando simultáneamente la máxima transferencia es de 240 Mbytes por segundo. La CPU, el controlador de E/S, y los periféricos interconectan y realizan transferencias flexibles y no intrusivas a través de una unidad de interconexión multibus. Para reducir el cuello de Damián Martínez Muñoz 41 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real botella, la interconexión permite el desplazamiento ilimitado de datos e instrucciones desde memoria interna o externa , caché, y E/S desde periféricos de fuera o dentro del chip, en un solo ciclo. SHARC proporciona 6 puertos de comunicación y conexión para formar array de multiprocesadores. Estos puertos captan datos a través del controlador de E/S y permiten crear mallas de procesadores DSP que pueden acceder a los espacios de memoria del resto (conexiones punto a punto entre los puertos del DSP definen cada procesador dentro de la malla). El controlador “on-chip” de E/S inicia, y responde a esos puertos. Las transferencias pasan a través de los puertos de E/S hacia y desde la memoria interna . El controlador de E/S descarga al procesador principal del DSP de realizar todas estas transferencias. Un puerto en paralelo sirve como interfaz directa para la memoria externa, periféricos o un procesador host. Este bus puede ser compartido hasta un máximo de 6 chips ADSP-2106x. Los chips SHARC ofrecen un espacio de direccionamiento unificado usando un bus de direcciones único de 32 bits y un solo bus de datos de 32 ó 42 bits. Para relojes de 40 MHz., el chip permite usar una memoria con ciclo de acceso de 15 nseg. sin requerir estados de espera. La interfaz especial host soporta µPs de 16 y 32 bits, así como también buses de sistema, tanto ISA como PCI. SHARC trata este host como un dispositivo mapeado en memoria, con escrituras o lecturas directas a memoria interna. Modos de direccionamiento. SHARC ofrece direccionamiento inmediato, indexado, de bit reverse, módulo circular, de registro directo e indirecto (se debe usar el direccionamiento indirecto para accesos a memoria externa). Instrucciones especiales. SHARC permite manipulación de bit, iteraciones de división, llamadas a subrutinas condicionales, bucles con una única instrucción o bloque de instrucciones, comparaciones de coma fija y coma flotante y ejecuciones condicionales. SHARC soporta IEEE-754, coma flotante (23 bits de datos, ocho de exponente y un bit de signo) y el formato extendido IEEE de 40 bits para precisión adicional (32 bits de datos). Soporte. Analog Devices ofrece un emulador basado en JTAG de gran rapidez que usa la capacidad de “debugging” incorporado en el ADSP-2106x. Trabaja bajo Microsoft Windows y soporta “debugging” para sistemas multiprocesador. La compañía también proporciona un Sistema de Desarrollo EZ-Lab, una tarjeta para PC con múltiples procesadores 2106x, así como un EZ-kit reducido con un compilador de C por $179. Otras compañías ofrecen productos tales como tarjetas multiprocesadores para PC, VME y OS. Analog Devices aporta un compilador de C basado en tecnología Gnu. Este compilador soporta C Numérico, que amplía la capacidad de procesamiento de matrices y vectores para procesamiento de señales. Otras herramientas incluyen un emsamblador-linkador, un simulador, librerías de aplicaciones, un divisor PROM y un debugger C a nivel fuente . Damián Martínez Muñoz 42 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real ANEXO: Tablas Comparativas Damián Martínez Muñoz 43 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Dispositivos Aplicaciones Instrucciones /datos (bits) Acumulador (bits) Registro de desplazamiento (bits) Generador de direcciones Buses de datos Puerto de interfaz host Rango de direcciones externo Telefonía GSM, codificación de voz CELP G.729 32/16 48 32 Uno Uno Sí Sí 4 Kbytes Módem, videoconferencia, GSM, speaker de teléfono Estaciones base celulares, módem DSVD, mezcladores de audio, cancelación de eco acústico Radar, sonar, procesamiento de imagen, electrónica médica 24/16 40 32 Dos Dos No Paralelo 4 Mbytes 24/16 40 40 Dos Dos Sí 16 bit host 48 Mbytes puerto DMA 20/16 20 Ninguno Chip separado con 5 6 Sí Paralelo 256 kbytes 32/16 40 40 2 2 No 64 kbytes 16/16 36 No 2 2 Sí Opción del cliente Opción del cliente 64kbytes (datos), 64kbytes (instrucciones) 16/16 36 36 2 2 Sí Opción del cliente 64kbytes (datos), 64kbytes (instrucciones) 32/32 40 40 2 3 No 64Mbytes 16/16 36 36 2 2 No DMA, Hold/Hida Serie Mensajería digital, cableado/móviles, control digital Celular digital, comunicación de voz 16/16 36 16 2 3 Sí No 16/16 40 Ninguno 2 2 No Paralelo Móviles, multimedia, vídeo conferencia, fax/módem Procesamiento de vídeo 32/16 40 40 2 2 Sí 32/(8 ó 16) 40 Ninguno 5 1 por procesador Sí Paralelo y serie 100Mbyte/s DMA Móviles, fax/módem 16/16 40 40 2 2 Sí Control de motores 16/16 32 16 1 1 No TMS320C2x Controladores de discos duros 16/16 32 16 1 1 TMS320C2xx Telecomunicaciones, electrónica de consumición, sistemas de seguridad 16/16 32 16 1 2 16 bit Coma fija Advances Risc Machines Soporte multiprocesador 16 bit Coma fija Picolo Analog Devices ADSP-2011 ADSP-21csp01 Array Microsystems A66xxx Atmel Lode DSP Group Pine DSPcore Oak DSPcore Hitachi SH-DSP Lucent Technologies Codificación de voz, procesamiento celular de señales Máquinas de teléfono-contestadores, módems de baja velocidad, grabadoras de voz Módems, DSVD, vídeo/audio conferencia, teléfonos celulares, DVD, AC3 Telecomunicaciones móviles, imagen digital, multimedia, módems Comunicación móvil, módems 64k words DSP16xxx Motorola 568xxx DSP561xx NEC µPD7701x Oxford Micro Devices 128kbytes (datos), 1Mbyte (instrucciones) 128kbytes (datos), 128kbytes (programa) 96kbytes (datos), 96kbytes (instrucciones) 16 Mbytes A236 SGS-Thomson 256kbytes (datos), 128kbytes (programa) 128kbytes Sí Opción del cliente Soporta paralelo (algunas versiones) No Sí No 384kbytes D950-Core Texas Insruments TMS320C1x Damián Martínez Muñoz 256kbytes 44 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Dispositivos Aplicaciones Instrucciones /datos (bits) Acumulador (bits) Registro de desplazamiento (bits) Generador de direcciones Buses de datos Soporte multiprocesador Puerto de interfaz host Rango de direcciones externo TMS320C5x Multimedia, celulares/sin cable/módem, discos duros Comunicaciones con/sin cable, redes, multimedia Estaciones móviles, plataformas de telefonía multicanal Vídeo conferencia, procesamiento digital, switching digital 16/16 32 16 1 2 Sí Paralelo 384 kbytes 16/16 40 40 2 3 Sí Paralelo 384 kbytes 32/16 40 40 2 2 Sí Paralelo 8 Mbytes 64/16 32 32 2 por DSP 2 por procesador Sí 4 Gbytes 16/16 24 Ninguno 2 2 No Vía Hold/HoldA handshake No 16/16 40 32 2 4 No No 128 bytes (datos), 128 kbytes (programa) Radar, imagen para aplicaciones médicas Audio, control, módem 8/24 (complex) 24/24 60 (dual) 56 Ninguno Chip separado Sí Paralelo Ilimitado Ninguno 2 4 (complex) 2 No Paralelo Móviles, multimedia, telecomunicaciones 24/24 56 56 2 3 Sí PCIcompatible 256 kbytes (datos), 128 kbytes (programa) 16 Mwords x 3 48/40 80 32 2 48/40 80 32 2 32/32 96 Ninguno 32/32 40 32/32 40 TMS320C54x TMS320C6x TMS320C8x Zilog Z893xx Z894xx Contestadores automáticos digitales, controladores de disco duro, telefonía digital, lectores de cinta magnética, control de motores Móviles, compresión de datos, dispositivos de contestadores automáticos digitales 20 y 24 bit Coma fija Butterfly BDSP9124 Motorola 5600x 563xx 20 y24 bit Coma fija 32 bit Coma flotante Analog Devices ADSP-21020 ADSP-2106x Motorola DSP96002 Texas Instruments TMS320C3x TMS320C4x Dispositivos Ultrasonidos para aplicaciones médicas, instrumentación de precisión, gráficos 3D, radar, sonar Procesamiento de gráficos/vídeo/imagen, redes digitales sin cable, antibloqueo, estaciones digitales celulares de sistemas de frenado Imagen, comunicaciones, procesamiento de cadenas Control, gráficos, imagen, audio, copiadoras, impresoras Radar, sonar, imagen, gráficos 3D, infraestructura de telecomunicación, comunicaciones de alta velocidad, aplicaciones de multiproceso Caché de instrucción Damián Martínez Muñoz Niveles de pila hardware 64 bytes (datos), 64 kbytes (programa) 32 bit Coma flotante Pila software Looping hardware Soporte JTAG No No 4G words 3 Sí Paralelo 4G words 2 2 Sí 413x109 32 2 2 Sí Paralelo (dos) No 32 Mbytes 32 2 3 Sí No 4 Gbytes Fuentes de interrupciones Retardo máximo de interrupción FFT 256 puntos (ciclos) Características especiales 45 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real externas (ciclos) 16 bit Coma fija 16 bit Coma fija Permite trabajar con varios µP ARM, 4 acumuladores de 48 bit 64x32 bit No Sí Sí Sí 2 20 Contactar con el vendedor Ninguno 16 No Sí No 4 5 11,920 Interfaz de memoria externa de datos y de programa es de 8 bits, 64 kwords SRAM 64 palabras 31 (caché selectiva de programa) No counter stack Sí Sí 4 5 11,915 No Ninguno No No Sí Ninguno NA Contactar con el vendedor Controlador de DMA de 8 canales, puertos serie multicanal, 96 registros con cambios de tarea un sólo ciclo, 2 puertos serie autobuffer/multicanal Procesador de funciones específico para FFTs ; nivel comercial, industrial y militar No 16 No Sí Sí 1 8 Contactar con el vendedor Unidades MAC dobles, Galois, Aceleradores Viterbi DSP Group No 8 No Sí Emulación onchip 2 2 19,424 Pine DSPcore Oak DSPcore Unidad de manipulación de bit, base ASIC, acelerador Viterbi No Ninguno Sí Sí Emulación onchip 3 2 16,528 Unidad de manipulación de bit, base ASIC, acelerador Viterbi Hitachi No No Sí Sí Sí 4 individuales, 16 codificación binaria 5 Contactar con el vendedor 15x16 bit Ninguno Sí No Sí 2 De 6 a 7 21,293 Bajo consumo (0.7 mA/MIPS), incluye expansión de arquitectura con aceleradores No Bucle do Sí Sí Sí 2 20 15,657 DSP561xx No 15 No Propio 4 5.5 12,162 NEC No 15 No Hardware con bucles anidados Sí Instrucciones y arquitectura tipo µC, unidad MAC nonpipelined, 5 modos de bajo consumo Contador, codec Sí 4 4 10,888 1 kbyte + 1 kbyte (datos) Ninguno Sí No No 4 12 Contactar con el vendedor No Ninguno Sí Sí Sí 1 7 12,971 Texas Insruments No 4 (8 para el C16) No No No 2 7 TMS320C1x TMS320C2x No 8 No Sí No 3 8 Contactar con el vendedor Contactar con el vendedor Advances Risc Machines Picolo Analog Devices ADSP-2011 ADSP-21csp01 Array Microsystems A66xxx Atmel Lode SH-DSP Lucent Technologies DSP16xxx Motorola 568xxx µPD7701x Oxford Micro Devices A236 SGS-Thomson D950-Core Damián Martínez Muñoz µP RISC +DSP, interfaz EDO RAM, DMA, DLL 8 registros/acumuladores de propósito general de 40 bits, conjunto de instrucciones en paralelo de un sólo ciclo, operación multifunción 4 DSPs en paralelo y un µP scalar de 24 bit, 3 puertos DMA para conexión de video, RS-232C, coprocesador integrado con estimación de movimiento Diseño para aplicaciones dedicadas. Librería disponible para diseños ASIC Unidad MAC de dos instrucciones Instrucción Repeat, RAM/ROM extendida 46 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Dispositivos Caché de instrucción Niveles de pila hardware Pila software Looping hardware Soporte JTAG Fuentes de interrupciones externas Retardo máximo de interrupción (ciclos) FFT 256 puntos (ciclos) TMS320C2xx No 8 No No Sí 5 8 25,039 Memoria flash on-chip TMS320C5x No 8 No Sí Sí 6 12 20,907 Unidad lógica en paralelo, amplia gama de RAM y ROM TMS320C54x No Ninguno Sí Sí Sí 5 8 13,251 Gran cantidad de memoria RAM/ROM interna, acelerador Viterbi TMS320C6x 8 kbytes Ninguno Sí Sí Sí 5 12 4227 TMS320C8x 2 kbytes Ninguno Sí Sí Sí 4 6 DSP 4881 Zilog No 6 No No No 3 4 Z893xx Z894xx Contactar con el vendedor No No Sí Sí No 3 6 Contactar con el vendedor 20 y 24 bit Coma fija DSP VLIW, 8 unidades funcionales en paralelo, 32 registros de 32 bit, compilador paralelo 4 DSPs y 1 µP RISC, 50 kbytes de SRAM, control de DRAM y vídeo, coprocesador DMA Interfaz codec, ADC, contador /temporizador ,PLL, SPI Interfaz codec, temporizador/contador, bus de teleprograma/datos externo, direccionamiento lineal 20 y24 bit Coma fija Opción del consumidor Opción del consumidor Sí No 1 NA BDSP9124 Contactar con el vendedor Contactar con el vendedor Motorola Butterfly Características especiales 1k-point complex, FFT 24 bit en 65 ms, 26 instrucciones de alto nivel integradas Emulación onchip, PLL, temporizador No 15 No Bucles do anidados Propio 3 5 8332 5600x 563xx 3 kbytes 16 Sí Sí Sí 5 4.25 10,918 Analog Devices 32x48 bit 20 No Sí Sí 5 5 6303 32x48 bits 30 No Sí Sí 4 5 6303 1024x32 bits 15 No Sí Propio 3 5 Contactar con el vendedor Texas Instruments 64x32 bits Ninguno Sí Sí Propio 4 8 12,410 Interfaz de memoria flexible (C32) TMS320C3x TMS320C4x 128x32 bits Ninguno Sí Sí Sí 4 8 11,884 Puertos de comunicación 32 bit Coma flotante 32 bit Coma flotante ADSP-21020 ADSP-2106x Motorola DSP96002 Damián Martínez Muñoz La pila utiliza automáticamente memoria externa cuando se desborda, DMA La memoria de programa almacena tanto datos como código, arquitectura Harvard off-chip, unidades de cálculo independientes en paralelo SRAM de doble puerto, 512 kbytes onchip, 6 puertos de conexión, 2 serie, controlador E/S de 10 canales DMA 2 interfaces host 32 bit, 2 puertos de memoria externa 32 bit, 2 canales DMA 47 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Comparación entre diferentes DSP’s de coma flotante ADSP-21060 TMS320C40 DSP96002 i860 25 ns 40 ns 50 ns 20 ns 40 25 20 50 120 50 60 100 25 ns 40 ns 50 ns 60 ns 32 (16 principales) 8 8 30 2 0 0 0 240 MB/s 50 MB/s 80 MB/s 0 0.46 ms 1.54 ms 1.05 ms 0.76 ms 150 ns, 6 ciclos 360, 9 ciclos 350 ns, 7 ciclos 440 ns, 22 ciclos Tamaño encapsulamiento 1.59 in2 3.46 in2 3.46 in2 3.06 in2 Ejecución por pulgada cuadrada Respuesta a interrupción 74 MFLOPS/in2 14 MFLOPS/in2 17 MFLOPS/in2 33 MFLOPS/in2 3 ciclos 4 ciclos 3 ciclos 22 ciclos Atributos del procesador Tiempo de ejecución de instrucción MIPS Máximo MFLOPS Espera de las instrucciones en coma flotante RAM interna (32 bit words) Puertos serie Ancho de banda DMA FFT, 1K complex División, coma flotante 32 bit Fuente : Texas Instruments, Motorola, Intel Users Manuals & Datasheets y EDN Magazine Damián Martínez Muñoz 48 Ing. Telecomunicación Sistemas de Procesado de Señal en Tiempo Real Bibliografía • • • • • • • TMS320C1x User’s Guide. Texas Instruments. TMS320C1x Product Bulletin. Texas Instruments. TMS320C2x User’s Guide. Texas Instruments. Apuntes del Seminario sobre DSP’s de Texas realizado por ADM. Manual de Usuario de la familia DS56000. Motorola. Manual de Usuario del DS56002. Motorola. Número de Mayo-1997 de la revista EDN Europe. Direcciones WEB de interés: • • • Texas Instruments: http://www.ti.com Motorola: http://www.motorola-dsp.com Analog Devices: http://www.analog.com Damián Martínez Muñoz 49