Módulo IFF

Anuncio

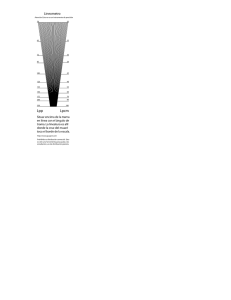

Diseño de Circuitos Integrados para Comunicaciones Page 1 of 6 DCIC-IFF DOCUMENTO Módulo: Especificaciones del módulo IFF Versión: 0.1 Autores: Añadir Añadir Fecha: XX de XX de 2004 Descripción: Especificaciones de diseño para el módulo IFF Otros: - Directorio: ~dcic03XX/projects/dcs/modules/iff/v0.1 Curso 2003-04 Fecha: 06-15-04 Diseño de Circuitos Integrados para Comunicaciones Page 2 of 6 1 Tabla de Contenido 1 Tabla de Contenido....................................................................................................................2 2 Revisiones y estado del documento ..........................................................................................3 3 2.1 Cambios de revisiones......................................................................................................3 2.2 Aspectos a añadir .............................................................................................................3 Especificaciones de diseño del Módulo IFF ..............................................................................4 3.1 Señales de entrada/salida del módulo IFF .......................................................................4 3.2 Señales de I/O de la CPU.................................................................................................4 3.3 Diagrama de tiempos........................................................................................................4 3.4 Descripción .......................................................................................................................5 3.5 Requisitos Funcionales.....................................................................................................5 3.6 Macros utilizadas ..............................................................................................................6 3.7 Interfaz de la memoria RAM de 512 x 66 .........................................................................6 Curso 2003-04 Fecha: 06-15-04 Diseño de Circuitos Integrados para Comunicaciones Page 3 of 6 2 Revisiones y estado del documento 2.1 Ver. 0.1 Cambios de revisiones Cambios Primera versión del documento Tabla 1 Revisiones 2.2 Ver. - Aspectos a añadir Aspectos a añadir en la descripción del módulo - Tabla 2 TBA Aspectos para la siguiente revisión Curso 2003-04 Fecha: 06-15-04 Diseño de Circuitos Integrados para Comunicaciones Page 4 of 6 3 Especificaciones de diseño del Módulo IFF 3.1 Señales de entrada/salida del módulo IFF 3.1.1 Señales Globales Señales Globales: Nombre de la señal clk reset 3.1.2 Descripción Reloj global del sistema Señal de reset asíncrona Tipo I I Señales de Datos y de Control del módulo Nombre de la señal Señales de interfaz din[31:0] sot eot Señales de interfaz ack ack_mask[3:0] Descripción Desde el bloque: RX Hasta el bloque: IFF Dato de entrada de 32 bits Señal de comienzo de la trama de datos de entrada Señal de final de la trama de datos de entrada Desde el bloque: XX Hasta el bloque: IFF Señal de reconocimiento de conexión Máscara que contiene la salida concedica Señales de interfaz sot_out eot_out dout[63:0] crq crq_mask[3:0] Desde el bloque: IFF Hasta el bloque: XX Señal de comienzo de la trama de datos de salida Señal de final de la trama de datos de salida Datos de salida de 64 bits Señal de petición de conexión Máscara de petición de conexión Tipo I I I I I O O O O O 3.2 Señales de I/O de la CPU Señales globales de CPU: Nombre de la señal Descripción Señales de monitorización: Nombre de la señal Descripción Tipo Tipo 3.3 Diagrama de tiempos Cronograma de datos de entrada clk....111...111...111...111...111...111...111...111...111...111...111...111...111...111 sot..........111111..................111111..............................111111......... eot............................111111........................111111..................... crc_err........................111111........................111111..................... din..........DOD0D0D1D1D1D2D2D2D3D3D3D0D0D0D1D1D1D2D2D2D3D3D3D4D4D4......D0D0D0D1D1D1D2D Curso 2003-04 Fecha: 06-15-04 Diseño de Circuitos Integrados para Comunicaciones Page 5 of 6 Cronograma del protocolo de conexión-aceptación clk....111...111...111...111...111...111...111...111...111...111...111...111...111...111 crq..........111111......111111..............................111111..................... crq_mask.....CMCMCM......CMCMCM..............................CMCMCM..................... ack............................111111..............................111111............... ack_mask.......................AMAMAM..............................AMAMAM............... 3.4 Descripción El bloque IFF recibe tramas de datos de 32 bits y las almacena diferenciado el destino de la trama. Con las tramas almacenadas realiza peticiones de conexión y, tras recibir el reconocimiento de conexión, envía la trama seleccionada. Las tramas de entrada con error de CRC no son almacenadas en el sistema. El bloque IFF soporta hasta cuatro posibles destinos (#0 al #3). Cada destino corresponde a una FIFO con capacidad de almacenamiento de 512 palabras. 3.5 Requisitos Funcionales Información-1 La trama de datos de entrada corresponde a una secuencia consecutiva de palabras de 32 bits recibidas a través de din. La primera palabra se señala activando la señal de entrada sot y corresponde a la cabecera de la trama, mientras la última palabra se señala con la señal eot. La trama está compuesta por una palabra de cabecera y varias palabras de datos. La última palabra de datos contiene, además, en sus dos bytes menos significativo el CRC de la trama. En caso de error de CRC se activa, durante la última palabra, la señal de crc_err. Información-2 La primera palabra de la trama, la denominada cabecera, contiene en su segundo byte menos significativo el destino de la trama. Así, por ejemplo: • trama de destino 0: HH0X XXXX … • trama de destino 1: HH1X XXXX … Información-3 Los requisitos del sistema obligan a almacenar las tramas en palabras de 64 bits. A tal efecto se disponen de FIFOs de 512 palabras. Al ser las tramas de longitud variable y ante la necesidad de delimitar el comienzo y el final de una trama almacenada en memoria, junto a los datos se almacenan las señales de comienzo y final de trama. Esta configuración queda reflejada en la siguiente figura: 0 0 1 0 1 0 0 0 1 0 1 0 D4 D2 D0 D4 D2 D0 sot eot Datos 64 bits 00 D3 D1 D5 D3 D1 512 palabras Las palabras impares se deben rellenar con ceros en la parte menos significativa. Requisito-1 El módulo debe almacenar en la FIFO de destino la trama recibida. Las tramas erróneas no deberán almacenarse en la FIFO. Curso 2003-04 Fecha: 06-15-04 Diseño de Circuitos Integrados para Comunicaciones Page 6 of 6 Requisito-2 Cuando el sistema disponga de al menos una trama almacenada en la FIFO, este debe generar una señal de petición de conexión crq, indicando al mismo tiempo y mediante la señal crq_mask las FIFOs que disponen de tramas almacenadas. Cada bit de la máscara crq_mask está sociado a una FIFO, siendo el bit menos significativo el bit asociado a la FIFO0. Una vez solicitada la petición de conexión y en caso de no recibir en el siguiente ciclo un reconocimiento de petición de conexión ack, se volverá a realizar una nueva petición de conexión. Tras recibir un reconocimiento de conexión, no se podrá realizar otra petición hasta que la trama haya sido completamente transmitida. Requisito-3 Tras recibir un reconocimiento de conexión ack, el módulo IFF debe comenzar la transmisión de la trama seleccionada. La FIFO seleccionada se establece en la máscara de reconocimiento ack_mask. El módulo IFF debe activar la señal de sot_out indicando la presencia de la primera palabra de 64 bits de la trama en dout. El módulo IFF debe activar la señal de eot_out indicando la presencia de la última palabra de 64 bits de la trama en dout. 3.6 Macros utilizadas Función Tipo (DP/SP) FIFO0 FIFO1 FIFO2 FIFO3 Total DP DP DP DP Tamaño de la macro 512x66 512x66 512x66 512x66 #Macros #Bits/ macro #Bits (Total) 1 1 1 1 4 33792 33792 33792 33792 33792 33792 33792 33792 135168 Nota: DP: Doble Puerto 3.7 Interfaz de la memoria RAM de 512 x 66 La siguiente tabla muestra las señales de interfaz del módulo de memoria utilizado para implementar las FIFO. Las señales son idénticas para ambos puertos, puerto A y puerto B, por lo que en el nombre de la señal se añade una X(A o B). Señales de Interfaz Nombre de la señal CLKX MEX OEX DX[65:0] QX[65:0] ADDRX[8:0] Curso 2003-04 Descripción Señal de reloj Habilitación del puerto correspondiente Habilitación de salida Bus de datos de entrada del puerto Bus de datos de salida del puerto Dirección Tipo I I I I O I Fecha: 06-15-04