2 C (2 B (2 B (2 A (2 C (2

Anuncio

COGNOMS:. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

NOM:

...................................................

DNI:

. . . . . . . . . . . . . . . . . . . GRUP:. . . . . . . . . . . . . . . . . . . . . . . . . . .

Problema 2 (2 punts)

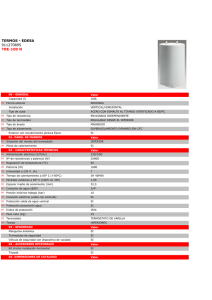

Es disposa d’un processador de 16 bits amb els següents senyals:

- Control: . . . . . . . . . . . . . . . . . . . . . . . L/E , AS , Ready

- Dades:. . . . . . . . . . . . . . . . . . . . . . . . D15:0

- Adreces:. . . . . . . . . . . . . . . . . . . . . . . A23:1 , BE1:0

A aquest processador es vol connectar a un sistema de memòria clàssic de 2 columnes de byte per

permetre accessos a byte i word tal com indica la Figura 1. En concret es volen mapejar les zones de

memòria A B i C sobre un únic mòdul de 222x8 exactament com s’indica a la Figura 2. Indicar la

connexió del mòdul de memòria al bus d’adreces així com la funció de descodificació del CS

Bit (+) pes

200001h

600001h

Bit (-) pes

A

(220x8)

B

(220x8)

C

(221x8)

B

A

(220x8)

C

(221x8)

(220x8)

C00001h

Figura 2

Figura 1

a) Indica quin seria el CS d’aquest modul per mapejar-hi les zones A, B, i C:

b) Indica quina seria la conexió del mòdul al bus d’adreces per que les zones A,B i C quedin mapejades exactament tal com indica la Figura 2:

Problema 3 (2 punts)

Tenim una CPU amb una cache amb les següents característiques:

-

CPI ideal . . . . . . . . . . . . . . . . . . . . . .1.8 cicles / instr

Temps de cicle (Tc) . . . . . . . . . . . . . . . . .10 ns

Nombre de referències per instrucció (nr) . . . . .1.4 ref / instr

Mida de la línia: . . . . . . . . . . . . . . . . . .8 bytes

Política de escriptura en cas d'encert:. . . . . . . .Escriptura retardada (Copy Back)

Política de escriptura en cas de fallo: . . . . . . . .Write Allocate

Temps de servei en cas d'encert: . . . . . . . . . .1 cicle

MP organitzada en: . . . . . . . . . . . . . . . . .4 mòduls entrellaçats

Latència dels mòduls de MP: . . . . . . . . . . . .5 cicles

Amplada de banda del bus MP ⇔ MC: . . . . . .16 bits que es transfereixen en 2 cicles

Quan es reemplaça una linea modificada, primer s’escriu la linea reemplaçada a MP i despres

es llegeix la nova linea.

La cache te càrrega a través (la carrega de MC es fa en paralel a la transferencia)

% escriptures . . . . . . . . . . . . . . . . . . . .15%

% de linees modificades . . . . . . . . . . . . . .20%

Tassa d’encerts (h) . . . . . . . . . . . . . . . . .90%

a) Quin sera el temps de servei (en cicles) en cas de fallo (Tsf) ?

b) Quin será el temps mig d’accés a memòria en cicles?

Tma =

c) Quin serà el temps mig d’execució d’una instrucció en ns.?

Texec =

Problema 4 (2 punts)

Supongamos que tenemos un computador con una memoria cache de datos con las siguientes

características:

• 64 conjuntos

• 4 líneas por conjunto

• 32 bytes por línea

• palabras de 4 bytes

• algoritmo de reemplazo LRU

Y un TLB de datos con las siguientes características:

• 32 entradas

• completamente asociativo y reemplazo LRU

• tamaño de página: 8 Kbytes

Sobre este sistema de memoria, se ejecutan 2 versiones diferentes para una misma aplicación:

int A[128][1024]; /* cada entero ocupa 4 bytes */

/* versión A */

R4 = 0;

for (R12=0; R12<1024; R12++)

for (R9=0; R9<128; R9++) {

R4 = R4 + A[R9][R12];

}

/* versión B */

R4 = 0;

for (R9=0; R9<128; R9++)

for (R12=0; R12<1024; R12++) {

R4 = R4 + A[R9][R12];

}

• Recordad que las matrices en C se almacenan por filas.

• Suponed que la matriz A está almacenada a partir de la dirección 0.

Se pide que rellenéis la siguiente tabla

fallos cache de datos

versión A

versión B

fallos del TLB de datos

Examen final d Estructura de Computadors II

-

7 de Juny de 2000

El problema 1 s’ha d’entregar en un full apart

Els problemes 2, 3 i 4 s’han d’entregar al mateix full de l’enunciat

Les notes sortiran el dia 21 de Gener

La revisió serà el 27 de Gener

Problema 1 (4 punts)

Queremos diseñar un termostato digital microprogramado encargado de regular el aire acondicionado

de una vivienda.

CAMBIO

ACK

bus datos

LEER

Termostato

8

CALOR

FRIO

El funcionamiento del termostato es el siguiente:

• El termostato ha de disponer de un registro interno con la temperatura deseada. Este registro se

ha de inicializar a 24oC.

• El termostato ha de mantener continuamente la temperatura ambiente en un rango de ± 2 oC

respecto a la temperatura deseada.

• Para leer la temperatura ambiente, hay que activar (a uno) la señal LEER durante 2 ciclos. La

temperatura está disponible en el bus de datos en el segundo ciclo de activación del ACK.

• Para activar la calefacción hay que activar (a uno) la señal CALOR, y mantenerla activa durante

dos ciclos.

• Para activar la refrigeración hay que activar (a uno) la señal FRIO y mantenerla activa durante

2 ciclos.

• Cuando el usuario quiere cambiar la temperatura deseada la señal CAMBIO se pone a 1. Para

leer la temperatura deseada el termostato ha de activar (a uno) la señal ACK durante 2 ciclos.

La temperatura deseada estará disponible en el bus de datos en el segundo ciclo de activación

del ACK. La señal CAMBIO, vuelve a cero cuando se desactiva el ACK.

Se pide que diseñéis el controlador del termostato utilizando la técnica de microprogramación. En

concreto se pide:

a) Diseño del camino de datos del controlador

b) Formato de la microinstrucción (describiendo los diferentes campos)

c) Diseño de la unidad de control (sobre todo del secuenciador)

d) Microprograma de Control

Notas:

• Podéis utilizar los registros, constantes y unidades funcionales que creáis más oportunos.

• Se valorará la EFICIENCIA, CLAREDAD y SIMPLICIDAD de la solución.