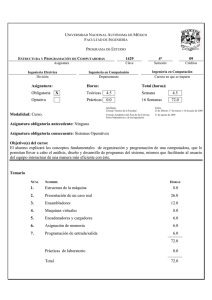

silabo 2014-i arquitectura de computadoras

Anuncio

UNIVERSIDAD NACIONAL PEDRO RUIZ GALLO FACULTAD DE INGENIERIA CIVIL DE SISTEMAS Y DE ARQUITECTURA ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS SYLLABUS DE LA ASIGNATURA DE ARQUITECTURA DE COMPUTADORAS I. DATOS INFORMATIVOS 1. 2. 3. 4. 5. 6. 7. 8. CODIGO DE ASIGNATURA PREREQUISITO SEMESTRE CICLO DE ESTUDIOS NUMERO DE CREDITOS CARGA HORARIA DURACION DOCENTE : : : : : : : : IS461 SISTEMAS DIGITALES 2014-I VIII Ciclo 04 HT: 03 HP:02 17 SEMANAS Ing. José Ramón Sandoval Jiménez II. SUMILLA DEL CURSO El curso brinda a los alumnos un conocimiento acerca de las arquitectura y organización de computadoras. El contenido abarca aspectos de arquitecturas de Von Neumann, RISC, Harvard y las actuales arquitecturas paralelas. Las clases teóricas se complementan con un laboratorio para familiarizar al alumno con el lenguaje de programación ensamblador, con el fin de que el alumno conozca las interioridades del microprocesador. III. OBJETIVOS GENERALES DEL CURSO - Dotar al estudiante de los conocimientos referentes a la organización y funcionamiento de las computadoras digitales. - Enseñar como está constituida la Unidad Central de Procesamiento (CPU) o microprocesador, analizando sus partes, funcionamiento, características y tendencia de la tecnología futura. - Brindar al alumno la capacidad de reconocer los componentes de una computadora su modo de operación y diseño - Brindar al alumno la capacidad de solucionar fallos en la computadora. - Enseñar la programación básica en lenguaje ensamblador. IV. PROGRAMACION ACADEMICA PRIMERA UNIDAD: ARQUITECTURA Y ORGANIZACIÒN DE UNA COMPUTADORA. OBJETIVOS ESPECIFICOS 1. Dar a conocer las diferencias existentes entre organización y arquitectura de computadoras 2. Dar a conocer como ha evolucionado las arquitecturas de computadoras a través del tiempo 3. Identificar las arquitecturas de computadoras actuales DURACIÓN 02 semanas SEMANA CONTENIDO TEMÁTICO 01 Organización y Estructura de una Computadora. Conceptos, Estructura y función. Evolución de la Arquitectura de Computadoras. 02 Rendimiento de las Computadoras. SEGUNDA UNIDAD: LA COMPUTADORA. MICROPROCESADOR. MEMORIA INTERNA Y EXTERNA LENGUAJE ENSAMBLADOR OBJETIVOS ESPECIFICOS 1. Dar a conocer los conceptos de funcionamiento de los microprocesadores 2. Hacer uso de herramientas como el lenguaje ensamblador para poder acceder a las interioridades de los microprocesadores DURACIÓN 06 semanas SEMANA CONTENIDO TEMATICO 03 Aritmética del procesador Unidad Aritmética y lógica. Sistema Binario. Representación entera: números naturales y números negativos: a)Módulo y signo b)C-1 c)C-2 d)Exceso 2n-1 Números en BCD. Números en punto flotante. 04 Operaciones aritméticas en C-2 Multiplicación y división Operaciones en punto flotante 05 Memoria Interna: Conceptos básicos sobre sistemas de memoria de computadora. Memoria principal semiconductora. Métodos de detección y corrección de errores: bit de paridad, Hamming y SEC-DEC. Memoria caché. Organización. Tipos. 06 y 07 Lenguaje ensamblador: Uso del Debug. Introducción. Uso y aplicaciones del lenguaje ensamblador. direccionamiento Interrupciones: Hardware. Software. Estructura de un programa enensamblador. Procedimiento de ensamble, ejecución. Entorno de programación. 08 Memoria Externa: Discos magnéticos, cintas magnéticas, discos magneto-ópticos, DVD. Organización. Estructura. Técnicas Raid. Niveles. EXAMEN PARCIAL I TERCERA UNIDAD: BUSES DEL SISTEMA Y FUNCIONAMIENTO DE LA E/S. LENGUAJE ENSAMBLADOR. OBJETIVOS ESPECIFICOS 1. Dar a conocer de que manera el computador se interconecta con los demas componentes de la computadora 2. Dar a conocer las técnicas para representar los datos en una computadora. 3. Identificar cómo realiza una CPU una operación aritmética; usando lenguaje ensamblador. DURACIÓN 04 semanas SEMANA CONTENIDO TEMÁTICO 09 Buses del sistema. Estructuras de interconexión. Jerarquías de buses múltiples. Estándares de buses: PCI, USB, IEEE 1394. 10 Montaje de una PC 11 Entrada/Salida. Dispositivos externos. Módulos de E/S E/S programada. E/S mediante interrupciones DMA 12 Instalación de Linux. Máquina virtual. Implementación RAID de disco CUARTA UNIDAD: UNIDAD DE CONTROL Y ARQUITECTURAS PARALELAS. OBJETIVOS ESPECIFICOS 1. Dar a conocer la técnica que utiliza la unidad de control para decodificar, interpretar y ejecutar instrucciones 2. Identificar las microinstrucciones que utiliza Pentium y Power PC. DURACIÓN 05 semanas SEMANA CONTENIDO TEMÁTICO 13 Unidad de Control. Microoperaciones. Control de la CPU. 14 15 Arquitectura RISC. La controversia CISC vs RISC Arquitecturas Superescalares. Supercomputadoras 16 EXAMEN PARCIAL II 17 PRESENTACION DE TRABAJO FINAL EXAMEN SUSTITUTORIO V. METODOLOGIA DE TRABAJO - Evaluación de entrada - Desarrollo de la clase en base a exposiciones y resúmenes en pizarra. Cada clase está acompañada de una práctica. - Exposición de software para la ensamblador. - Trabajos de Investigación Bibliográfica. - Evaluación de salida. resolución de problemas: Lenguaje VI. CRITERIO DE EVALUACION 6. 1. REQUISITOS DE APROBACION Asistencia a clases Los alumnos que tengan más del 30% de inasistencias serán inhabilitados en el curso. Examen de aplazados Rendirán examen de aplazados los alumnos que no alcanzarán la NOTA PROMOCIONAL APROBATORIA, tienen derecho a este examen aquellos alumnos cuyo promedio sea mayor o igual que 07. Otros Los exámenes prácticos y trabajos no presentados en la fecha señalada serán calificados con nota 0 y no serán sustituidos ni anulados. Las evaluaciones Parciales se rendirán de acuerdo al desarrollo del syllabus, y las evaluaciones prácticas se realizarán sin previo aviso. Los trabajos serán presentados una semana después de habérseles pedido. El examen sustitutorio reemplaza a la evaluación menor de uno de los 03 exámenes parciales siempre y cuando estos hayan sido rendidos. 6.2. SISTEMA DE CALIFICACION Nota promocional NF = 0,25EPI+0,25EPII + 0,15PT+0,15PL + 0,1EXPO+ 0,1TF NF EPI EPII PT PL EXPO TF : Nota Final : Examen parcial.I : Examen parcial.II : Practicas Teoria. : Practicas Laboratorio : Exposición : Trabajo Final ES : Examen Sustitutorio. Será evaluado la semana 17; y comprende la totalidad del curso VII. FUENTES BIBLIGRAFICAS [01] ORGANIZACIÓN DE LAS COMPUTADORAS Un Enfoque Estructurado ANDREW TANENBAUM Prentice-Hall.5ª edición. México, 2010 [02] ORGANIZACIÓN Y ARQUITECTURA DE LAS COMPUTADORAS Diseño para optimizar prestaciones. WILLIAM STALLINGS Edit. Prentice-Hall. 8a Edición. Mexico, 2008 [03] LOS MICROPROCESADORES DE INTEL BREY B. BARRY 7ma Edición [04] FUNDAMENTOS DE HARDWARE ISABEL Ma. JIMENEZ CUMBRERAS 1a Edición, IBERGARCETA, Madrid 2013 [05] LENGUAJE ENSAMBLADOR PARA MICROCOMPUTADORAS IBM GODFREY, J. TERRY Edit. Prentice-Hall. 2a Edición [06] ARQUITECTURA DE COMPUTADORAS ALCALDE, EDUARDO [07] Arquitectura de Computadores M. Morris Mano Prentice Hall Hispanoamericana, S.A. [08] Organización y Diseño de Computadoras Patterson, David A. Hennessy. Mc. Graw Hill, 4da Edición. España, 2011