Clase Práctica

Anuncio

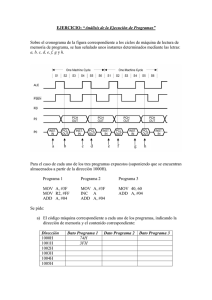

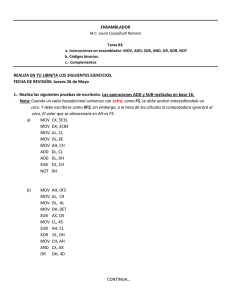

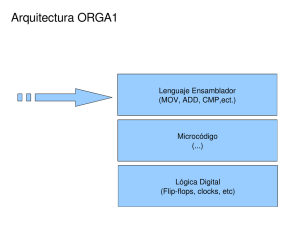

Clase Práctica - Seguimiento Organización del Computador 1 Segundo Cuatrimestre 2008 Ciclo de instrucción de la maquina Orga I Fech Buscar en memoria (PC) la instruccion a ejecutar y aumentar el PC. Decode Decodificar la instruccion e identificar las tareas que debe realizar. Data Fech (opcional) Buscar de memoria los datos requeridos por la instrucción decodificada. Execute Realizar el conjunto de tareas idicadas por la instrucción. Ejercicio 1 (26 de junio de 2007) Sean las siguientes rutinas en la arquitectura ORGA1, cargadas en la posicion de memoria 0x0010 y 0x0300 respectivamente. eti1: inicio: ciclo: fin: DW F0A4 MOV R1,0F4B MOV R2,FFFB CALL sumarR1R2 CMP R2,0 JZ fin SUB R2,1 JMP ciclo RET sumarR1R2: ADD R1, [et1] ADD [R1], R2 RET a) Indique las posiciones de memoria de cada línea de este código. Solución. 0x0010 0x0011 0x0013 0x0015 0x0017 0x0019 0x001A 0x001C 0x0013 / / / / / / / / / 0x0300 / 0x0302 / 0x0303 / [dgonzalez] eti1: inicio: ciclo: fin: sumarR1R2: DW F0A4 MOV R1,0F4B MOV R2,FFFB CALL sumarR1R2 CMP R2,0 JZ fin SUB R2,1 JMP ciclo RET ADD R1, [et1] ADD [R1], R2 RET 1 b) Escriba la decodificación detallada de la instruccion "JZ fin". Solución. [dgonzalez] 1 Cod OP 1 1 1 Salto Tipo 0 0 1 JZ=JE 0 0 0 Desplazamiento 0 0 0 1 0 4 0 c) Indicar todos los modos de direccionamiento para cada instrucción. Solución. 0x0011 0x0013 0x0017 0x0020 / / / / 0x0300 / 0x0302 / [dgonzalez] MOV MOV CMP DEC R1,0F4B R2,FFFB R2,0 R2 ADD R1, [et1] ADD [R1], R2 . . . . Registro - Inmediato Registro - Inmediato Registro - Inmediato Registro . Registro - Directo . Indirecto Registro - Registro d) Suponiendo que todos los registros empiezan en 0, PC=inicio y SP=0xFFEF hacer un seguimiento del programa hasta alcanzar una instrucción inválida. Solución. [dgonzalez] PC SP 0x0011 0x0013 0x0015 0xFFEF 0xFFEF 0xFFEF PC Post Fetch 0x0012 0x0014 0x0016 Instrucción 0x0300 0xFFEE 0x0301 ADD R1, [et1] 0x0302 0x0302 0xFFEE 0x0303 ADD [R1], R2 0x0303 0x0303 0xFFEE 0x0304 RET 0x0304 0x0012 0xFFEF 0x0013 - MOV R1,0F4B MOV R2,FFFB CALL sumarR1R2 PC Post Data 0x0013 0x0015 0x0017 - Cuentas R1 ← 0x0F4B R2 ← 0xFFFB PC ← 0x0300 SP ← SP-1 [0xFFEF] ← 0x0017 R1 ← R1+[et1] = 0x0F4B+[0x0010] = = 0x0F4B+0xF0A4 = 0xFFEF [R1] ← [R1]+R2 = [0xFFEF]+0xFFFB = = 0x0017+0xFFFB = 0x0012 PC ← [0xFFEF] = 0x0012 SP ← SP+1 INVALIDA Ejercicio 2 (6 de mayo de 2008) Sea el siguiente fragmento de código assembler de ORGA1. main: ADD ADD JNE MOV MOV ADD [0x0005],0x0F00 [0x0009],0x0002 main [0x000F],0xF0FE [0x000D],0x2848 [0x0003],[0x0006] Considerando que la etiqueta main se encuentra cargada a partir de la dirección 0x0000, que todos los registros inicialmente valen cero y que el P C también vale cero. a) Indicar la dirección de memoria que corresponde a cada instrucción. 2 Solución. [dgonzalez] 0x0000: 0x0003: 0x0006: 0x0007: 0x000A: 0x000D: main: ADD ADD JNE MOV MOV ADD [0x0005],0x0F00 [0x0009],0x0002 main [0x000F],0xF0FE [0x000D],0x2848 [0x0003],[0x0006] b) Realizar el seguimiento desde la etiqueta main, hasta llegar a una instrucción inválida. Solución. [dgonzalez] PC ZCVN Instrucción Dec. 0000 PC Post Fetch 0x0001 ADD [0x0005],0x0F00 0x2200 PC Post Data 0x0003 0x0000 0x0003 0000 0x0004 ADD [0x0009],0x0F02 0x2200 0x0006 0x0006 0x0007 0x000A 0x000D 1100 1100 1100 1100 0x0007 0x0008 0x000A 0x000E JNE main MOV [0x000F],0x0000 MOV [0x000D],0x2848 ADD R1, [0x0003] 0xF9F9 0x1200 0x1200 0x2848 0x0007 0x000A 0x000D 0x000F 0x000F 1100 0x0010 Inválida 0x0000 Cambios [0x0005]←[0x0005]+0x0F00 [0x0005]←0x0002+0x0F00 [0x0005]←0x0F02 [0x0009]←[0x0009]+0x0F02 [0x0009]←0xF0FE+0x0F02 [0x0009]←0x0000 [0x000F]←0x0000 [0x000D]←0x2848 R1←[0x0003] R1←0x2200 c) ¿Cuál es el valor de desplazamiento de la instrucción JNE? Solución. [dgonzalez] El valor de desplazamiento es −7, ya que deben saltar dos instrucciones que ocupan 3 direcciones de memoria cada una y considerar que ya se desplazo el PC. 3