Capitulo 5 Aula 2016_

Anuncio

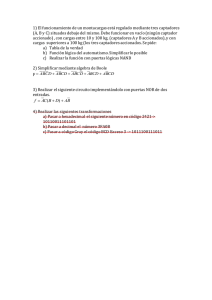

UTN-FRC TECNICAS DIGITALES I GUIA DE TRABAJOS PRACTICOS 2016 Ing. Francisco G. Gutiérrez MULTIPLEXORES CODIFICADORES Y DECODIFICADORES Objetivo: Al finalizar este práctico se espera que el estudiante comprenda el funcionamiento de los multiplexores, decodificadores y codificadores. Debe ser capaz de resolver funciones lógicas utilizando los dispositivos mencionados. En clase se deben resolver los ejercicios con sombra, en la carpeta de trabajos prácticos deben estar presentes todos los ejercicios de esta guía. 1. Determine las funciones lógicas correspondiente a los siguientes esquemas con multiplexores. Exprese la función como suma de miniterminos. FA=? 1 1 0 1 D0 D1 D2 D3 E E MUX 8 a 1 D0 0 0 0 1 A B C D D4 D5 D6 D7 1 MUX 2 a 1 F D1 S0 1K S0 S1 GND S2 FB=? 1/3 UTN-FRC TECNICAS DIGITALES I GUIA DE TRABAJOS PRACTICOS 2016 Ing. Francisco G. Gutiérrez U? 0 1 D0 D1 0 1 D2 D3 A B C S0 MUX 4a1 VCC D U? E S1 1K D0 F D1 S0 U? MUX 2 a 1 0 0 1 1 D0 D1 D2 D3 S0 MUX 4a1 S1 FC=? 2. Resolver las siguientes funciones lógicas con dos multiplexores de 4:1. Junto a cada función a resolver se encuentra la referencia a la combinación de multiplexores a utilizar. Con el tipo de MUX ver la tabla de verdad para la combinación de la salida. a) b) c) d) e) fa(ABC) = ∑ 0, 2, 3, 5, 7 [Mux1,Mux1],[Mux2,Mux2], [Mux3,Mux3] fb(ABC)=∑ 1, 3, 4, 6, 7 [Mux2,Mux2],[Mux3,Mux3],[Mux1,Mux2] fc(ABC)= ∑ 0, 2, 4, 5, 6, 7 [Mux3,Mux3],[Mux1,Mux2],[Mux3,Mux1] fd(ABCD)= ∑ 1,3, 4, 7, 10, 12, 14 [Mux3,Mux1], [Mux3,Mux2], [Mux1,Mux2] fd(ABCD)= ∑ 2,4, 8, 7, 10, 12, 14,15 [Mux1,Mux1], [Mux3,Mux3], [Mux2,Mux2] CE 1 0 0 0 0 Mux1 A B x x 0 0 0 1 1 0 1 1 out 1 In0 In1 In2 In3 CE 0 1 1 1 1 Mux2 A B x x 0 0 0 1 1 0 1 1 out 0 In0 In1 In2 In3 2/3 UTN-FRC TECNICAS DIGITALES I GUIA DE TRABAJOS PRACTICOS 2016 CE 1 0 0 0 0 Mux3 A B x x 0 0 0 1 1 0 1 1 Ing. Francisco G. Gutiérrez out Z In0 In1 In2 In3 3. Implementar las siguientes funciones utilizando un multiplexor de 8 a 1. a) b) c) d) e) f) g) h) fa(ABCD) = П 0, 2, 3, 5, 7,12,10,14 fb(ABCD)=∑ 1, 3, 4, 6, 7 fc(ABCD)= П 0, 2, 4, 5, 6, 7,10,11,12,15 fd(ABCD)= ∑ 1,2,3, 4, 8, 9,10, 12, 14 fe(ABCD) = П 0, 2, 3, 5, 7,8, 9, 12, 14,15 ff(ABCD)=∑ 1, 3, 4, 6, 7 fg(ABCD)= П 0, 2, 4, 5, 6, 7, 14, 15 fh(ABCD)= ∑ 0,1, 4, 7, 10, 12, 14 4. Implementar las siguientes funciones utilizando un multiplexor de 4 a 1. a) b) c) d) e) f) g) h) fa(ABCD) = ∑ 0, 2, 3, 5, 7,12,10,14 fb(ABCD)=∑ 1, 3, 4, 6, 7 fc(ABCD)= ∑ 0, 2, 4, 5, 6, 7,10,11,12,15 fd(ABCD)= ∑ 1,2,3, 4, 8, 9,10, 12, 14 fe(ABCD) =∑ 0, 2, 3, 5, 7,8, 9, 12, 14,15 ff(ABCD)= П 1, 3, 4, 6, 7 fg(ABCD)= ∑ 0, 2, 4, 5, 6, 7, 14, 15 fh(ABCD)= П 0,1, 4, 7, 10, 12, 14 5. Diseñar un decodificador BCD a 7 segmentos utilizando 1 multiplexor de 4 a 1 por cada segmento, tipo CD4052. En caso de que se presente a la entrada un dato erróneo inhibir la salida utilizando la señal de selección del chip. 6. Describir un multiplexor 8:1 y otro de 4:1 con control de salida para tercer estado en VHDL utilizando “WHEN ELSE”, utilizar una señal de habilitación que deje la salida en ‘0’ cuando la misma es ‘1’. <name> <= <expression> when <condition> else <expression> when <condition> else <expression>; 7. Resolver las siguientes funciones lógicas utilizando un codificador de 3 a 8. a) fa(ABC) = П 0, 2, 3, 5, 7 b) fb(ABC)= П 1, 3, 4, 6, 7 c) fc(ABC)= П 0, 2, 4, 5, 6, 7 d) fd(ABCD)= П 1,3, 4, 7, 10, 12, 14 e) fg(ABCD)= П 0, 2, 4, 5, 6, 7, 14, 15 3/3 UTN-FRC TECNICAS DIGITALES I GUIA DE TRABAJOS PRACTICOS 2016 Ing. Francisco G. Gutiérrez 8. Implementar el decodificador de errores para un código de Hamming de 9 bits de información utilizando decodificadores de 3 a 8. 9. Diseñar un sistema combinacional con dos entradas A y B de 8 bits cada una, las cuales representan un número entero sin signo, y una entrada de control extra MIN/MAX. La salida del sistema Z también es de 8 bits. La salida Z=0 si A=B, Z=min(A,B) si MIN/MAX=1, Z=max(A,B) si MIN/MAX=0. 9.1. Diseñar el sistema utilizando multiplexores. 9.2. Describir el sistema en VHDL. 9.2.1. Adjuntar la descripción. 9.2.2. Adjuntar la pantalla de simulación. 4/3