ARQUITECTURA DE COMPUTADORES Enero de 2009 El

Anuncio

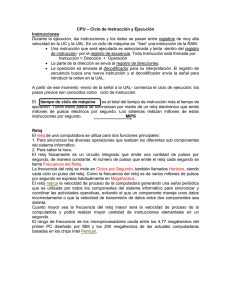

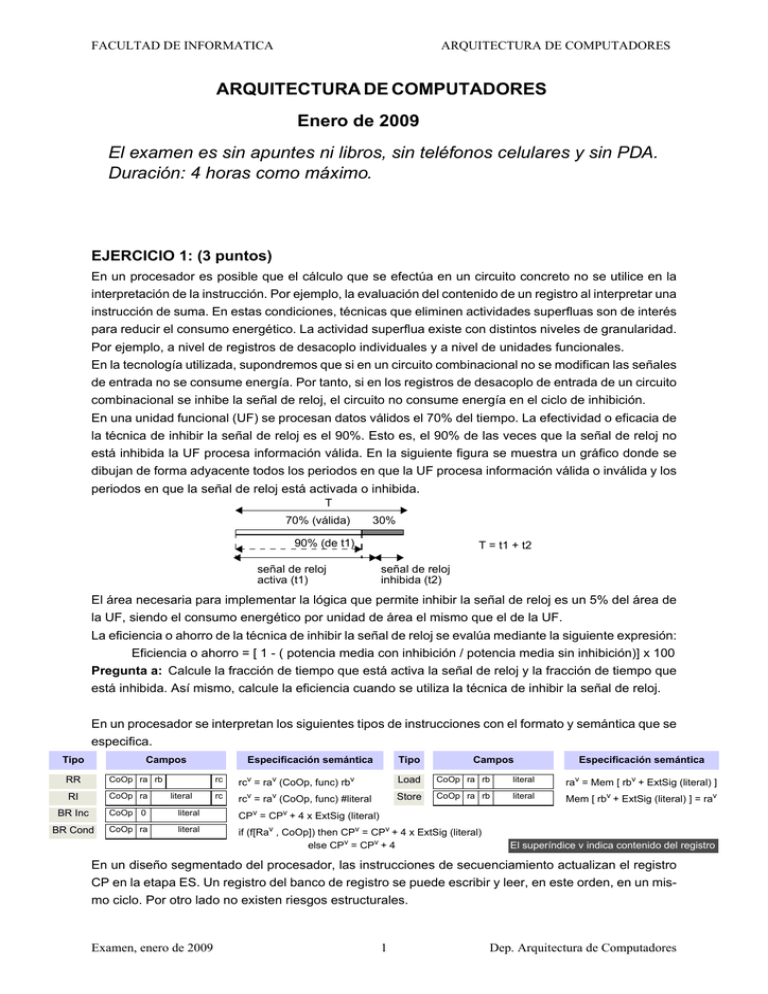

FACULTAD DE INFORMATICA ARQUITECTURA DE COMPUTADORES ARQUITECTURA DE COMPUTADORES Enero de 2009 El examen es sin apuntes ni libros, sin teléfonos celulares y sin PDA. Duración: 4 horas como máximo. EJERCICIO 1: (3 puntos) En un procesador es posible que el cálculo que se efectúa en un circuito concreto no se utilice en la interpretación de la instrucción. Por ejemplo, la evaluación del contenido de un registro al interpretar una instrucción de suma. En estas condiciones, técnicas que eliminen actividades superfluas son de interés para reducir el consumo energético. La actividad superflua existe con distintos niveles de granularidad. Por ejemplo, a nivel de registros de desacoplo individuales y a nivel de unidades funcionales. En la tecnología utilizada, supondremos que si en un circuito combinacional no se modifican las señales de entrada no se consume energía. Por tanto, si en los registros de desacoplo de entrada de un circuito combinacional se inhibe la señal de reloj, el circuito no consume energía en el ciclo de inhibición. En una unidad funcional (UF) se procesan datos válidos el 70% del tiempo. La efectividad o eficacia de la técnica de inhibir la señal de reloj es el 90%. Esto es, el 90% de las veces que la señal de reloj no está inhibida la UF procesa información válida. En la siguiente figura se muestra un gráfico donde se dibujan de forma adyacente todos los periodos en que la UF procesa información válida o inválida y los periodos en que la señal de reloj está activada o inhibida. T 70% (válida) 30% 90% (de t1) señal de reloj activa (t1) T = t1 + t2 señal de reloj inhibida (t2) El área necesaria para implementar la lógica que permite inhibir la señal de reloj es un 5% del área de la UF, siendo el consumo energético por unidad de área el mismo que el de la UF. La eficiencia o ahorro de la técnica de inhibir la señal de reloj se evalúa mediante la siguiente expresión: Eficiencia o ahorro = [ 1 - ( potencia media con inhibición / potencia media sin inhibición)] x 100 Pregunta a: Calcule la fracción de tiempo que está activa la señal de reloj y la fracción de tiempo que está inhibida. Así mismo, calcule la eficiencia cuando se utiliza la técnica de inhibir la señal de reloj. En un procesador se interpretan los siguientes tipos de instrucciones con el formato y semántica que se especifica. Tipo Campos RR CoOp ra rb RI CoOp ra BR Inc CoOp 0 literal BR Cond CoOp ra literal literal Especificación semántica Tipo Campos Especificación semántica rc rcv = rav (CoOp, func) rbv Load CoOp ra rb literal rav = Mem [ rbv + ExtSig (literal) ] rc rcv = rav (CoOp, func) #literal Store CoOp ra rb literal Mem [ rbv + ExtSig (literal) ] = rav CPv if = CPv + (f[Rav 4 x ExtSig (literal) , CoOp]) then CPv = CPv + 4 x ExtSig (literal) else CPv = CPv + 4 El superíndice v indica contenido del registro En un diseño segmentado del procesador, las instrucciones de secuenciamiento actualizan el registro CP en la etapa ES. Un registro del banco de registro se puede escribir y leer, en este orden, en un mismo ciclo. Por otro lado no existen riesgos estructurales. Examen, enero de 2009 1 Dep. Arquitectura de Computadores FACULTAD DE INFORMATICA ARQUITECTURA DE COMPUTADORES En la fase de decodificación de un procesador se conoce el tipo de instrucción y, por tanto, determinísticamente se conocen los recursos del camino de datos que se utilizan, excepto el sumador de la etapa CP. En estas condiciones, la información del tipo de instrucción, suministrada por el decodificador, se puede utilizar para gestionar la inhibición de la señal de reloj en algunos de los registros de desacoplo del camino de datos. A esta señal de inhibición la denominaremos señal de control de la señal de reloj (INH). En la siguiente figura se muestra parte de un camino de datos segmentado para interpretar los tipos de instrucciones especificados previamente. En esta implementación del procesador la lectura del banco de registros se efectúa concurrentemente con la decodificación. DL ALU BUS_DL DL_ALU +4 + ALU_MEM C rb 15..5 rc 1 ES MI 0 dir inst 1 B Reloj 1 Ed BR Rd Lb I 0 J D EsReg Rb Ra 2 1 0 MUXREG 0 func Reloj 1 EsMemDL K A E F G Ldm Edm EV L Reloj M N H 0 O EsMem Dec_CoOp CoOp 1 dir ALU La MD B 0 MEM_ES MUXBr 1 EXTSIG CP CoOp ra 0 MUXCP A MUXImp M MUXData BUS EsMemM CP EsRegM EsRegDL En un diseño segmentado, la señal INH se puede propagar a las siguientes etapas utilizando registros de desacoplo adicionales con la señal de reloj activada. A efectos de análisis de consumo de energía supondremos que todos los elementos del camino de datos actúan como si fuesen circuitos combinacionales (incluidos MI, MD y BR), excepto los registros de desacoplo. Por tanto, si se inhibe la señal de reloj en todos los registros de desacoplo que son entrada de un circuito o elemento, éste no consume energía. En el caso particular de los elementos MD y BR supondremos que ni la señal de reloj ni las señales provenientes de los registros N y Q respectivamente son entradas de estos elementos. Pregunta b: Sin que se modifique la semántica de la instrucción y una vez se ha decodificado una instrucción, indique para cada tipo de instrucción los registros de desacoplo superfluos (a los que se les puede inhibir determinísticamente la señal de reloj, aunque sea en ciclos distintos). En la etapa DL se dispone de las siguientes señales. Tipo de instrucción señal en DL RR RR RI RI Load LD Store ST BR Inc BRI BR Cond BRC Pregunta c: Diseñe la lógica de control para inhibir la señal de reloj en los registros de desacoplo. Para simplificar los cálculos supondremos que los multiplexores, el elemento EXTSIG y la lógica de interbloqueos no consumen energía. Así mismo, supondremos que todos los registros de desacoplo consumen lo mismo, aunque el número de bits de entrada sea distinto. Por otro lado, supondremos que los elementos MI, MD, BRL, BRE, ALU, EV, decodificador y sumador en la etapa CP consumen lo mismo (línea gruesa en la figura). Por BRL y BRE entendemos respectivamente las dos acciones de lectura y la acción de escritura en el banco de registros, lo cual es lo que hay que considerar desde el punto de vista del consumo. El consumo de los registros de desacoplo es un 5% del consumo de la ALU. Además suponga que un registro de desacoplo con la señal de reloj inhibida no consume. Consumo energético (julios) Examen, enero de 2009 Registros de desacoplo MI, MD, BRL, BRE, ALU, EV, decodificador, sumador en etapa CP RD = 0.05 x CE 1 x CE 2 Dep. Arquitectura de Computadores P Q FACULTAD DE INFORMATICA ARQUITECTURA DE COMPUTADORES Si no se inhibe la señal de reloj en los registros de desacoplo que son entrada de los elementos de almacenamiento MD y BR supondremos consumo aunque no se actualicen. Cuando no se inhibe la señal de reloj todos los dispositivos del camino de datos conmutan (no tendremos en cuenta la posibilidad de que una señal del camino de datos mantenga el mismo valor en ciclos consecutivos). Entonces, de la figura previa se obtiene que el consumo energético para cualquier instrucción es: Número de registros de desacoplo activos Número de elementos activos TOTAL (consumo energético) 18 8 8.9 x CE Sin inhibir el reloj Pregunta d: Calcule por tipo de instrucción el ahorro energético cuando se utiliza la técnica de inhibición de la señal de reloj en los registros de desacoplo. El decodificador identifica explícitamente las instrucciones nop de lenguaje máquina y activa la señal NOPD, la cual se puede utilizar para inhibir registros de desacoplo. Además, desactiva las señales EsMemDL y EsRegDL que se utilizan para indicar respectivamente actualización de la memoria y el banco de registros. Pregunta e: Al interpretar una instrucción nop indique los registros de desacoplo a los que se les puede inhibir la señal de reloj. Así mismo, calcule el consumo energético. En el procesador descrito, para adecuar la semántica del procesador a la semántica del lenguaje máquina, se emula un funcionamiento secuencial en los casos de riesgos de datos debidos a registros y riesgos de secuenciamiento. En el caso de riesgos de datos debido a registros se bloquea la instrucción que detecta el riesgo en la etapa DL y se propaga, en el mismo ciclo, el bloqueo a las etapas previas. En el caso de un riesgo de secuenciamiento, una vez se ha decodificado una instrucción de secuenciamiento se descartan las instrucciones más jóvenes que empiezan a interpretarse. Este descarte se mantiene mientras no se determina la dirección de la siguiente instrucción que debe interpretarse. En la siguiente figura se muestran las acciones que se efectúan en los dos tipos de riesgos. ciclos instrucción load R1, 0(R2) load R3, 0(R1) store R5, 0(R6) add R4, R4, #8 1 2 3 4 5 6 CP B DL A M E CP B DL CP 7 8 9 10 instrucción 11 100 bne R1,1$ nop nop nop 104 load DL 108 add nop nop nop DL A M E 112 sub B B B DL A M E CP CP CP B DL A M 116 xor E 1$: 200 add R5, R10, R30 13 14 15 16 17 18 CP B DL A M E CP B CP 19 20 nop nop nop nop B CP nop nop nop nop B CP nop nop nop nop B CP nop nop nop nop B DL A La lógica de interbloqueos activa las señales RD y/o RS en los ciclos en que se detecta respectivamente un riesgo de datos debido a registros y/o un riesgo de secuenciamiento. En el caso de detectar un riesgo de datos debido a registros, la inyección de una instrucción nop (NOPDEC) desde la etapa DL se implementa simplemente desactivando las señales EsMemDL y EsRegDL. Pregunta f: Calcule el consumo energético de gestionar 1 ciclo perdido en un riesgo de secuenciamiento (por ejemplo, el consumo en la 2ª fila del diagrama de la derecha). Note que en 1 ciclo perdido están involucradas todas las etapas (sombreadas en la figura). Pregunta g: Diseñe la lógica que inhibe la señal de reloj de los registros de desacoplo en los siguientes casos: a) al interpretar una instrucción nop, b) cuando se detecta un riesgo de datos y c) cuando se detecta un riesgo de secuenciamiento. Para simplificar los cálculos de energía, en un riesgo de datos debido a registros supondremos que todos los ciclos de estancia en DL menos el 1º ciclo (ciclo 4 en el diagrama de la izquierda) consumen lo mismo. Durante estos ciclos no tendremos en cuenta la posibilidad de que se escriba un registro que modifique una de las entradas de alguno de los caminos de lectura. En un ciclo de bloqueo la información en los registros de desacoplo de entrada de las etapas CP, BUS y DL no se modifica (sombreadas Examen, enero de 2009 3 Dep. Arquitectura de Computadores M E FACULTAD DE INFORMATICA ARQUITECTURA DE COMPUTADORES en la figura). Por tanto, el consumo energético de un ciclo perdido debido a un riesgo de datos es 0.3 x CE, ya que sólo consumen los registros no inhibidos. (No tenemos en cuenta que en todos los ciclos de bloqueo se inyecta la misma instrucción NOPDEC). En un conjunto de programas de prueba se mide la siguiente distribución de instrucciones, además a partir de ahora, supondremos los siguientes consumos energéticos cuando se inhibe la señal de reloj. Tipo de instrucción distribución consumo con inhibición RR 45% 6 x CE RI 15% 6 x CE Load 20% 7 x CE Store 5% 6 x CE BR Inc 5% 5 x CE BR Cond 10% 6 x CE Por otro lado, al ejecutar el conjunto de programas se pierden en media 0.8 ciclos por instrucción debido a riesgos de datos. Pregunta h: Calcule el ahorro energético, debido a la técnica que inhibe la señal de reloj en los registros de desacoplo, al ejecutar el conjunto de programas de prueba. EJERCICIO 2: (3.5 puntos) Un processador segmentat multicicle interpreta instruccions del següent repertori: ENT Rd = Ra op Rb CF Fd = Fa op Fb LDE Rd = M[Rb+d] LDF Fd = M[Rb+d] STE M[Rb+d] = Ra STF M[Rb+d] = Fa BCE si cond (Rb) llavors CP = CP+d altrament CP = CP+4 BCF si cond (Fb) llavors CP = CP+d altrament CP = CP+4 amb la següent segmentació: cicles 1 2 3 etapes CP B D 4 5 LE ALU EE LE @ LE 6 @ 7 8 M1 M2 EE LF X1 X2 M1/LF M2 EF 9 10 11 ENT, BCE LDE, STE X3 X4 EF CF, BCF LDF, STF El camí de dades corresponent a la part d'execució disposa de 3 ramificacions, tal com mostra la figura. La ramificació superior (ALU) executa les instruccions ENT i BCE. La ramificació del mig (MEM) executa les instruccions d'accés a memòria. La tercera ramificació (PF) executa les instruccions CF i BCF. El camí de dades disposa de suficients recursos per a que no es produeixin riscs estructurals. 1 0 (Ra) BRE Etapa D a XCE (Rb) literal b a BRE ALU a BRE EV @ M1 M2 a BRF mux (Fa) BRF a X1 XCF b (Fb) 3 2 FEV X2 X3 X4 a BRF Cada banc de registres (BRE, BRF) té 2 ports de lectura i 2 d'escriptura. En cada banc, un registre es pot escriure i llegir, en aquest ordre, en un mateix cicle. Observa que la lectura en el banc BRF es fa dues etapes després de la lectura del banc BRE. Els mòduls XCE i XCF contenen multiplexors per encaminar dades des de les sortides de les ramificacions cap als registres de desacoblament d'entrada de les ramificacions i de l'etapa M2 (només el mòdul XCF). Examen, enero de 2009 4 Dep. Arquitectura de Computadores FACULTAD DE INFORMATICA ARQUITECTURA DE COMPUTADORES Els riscs de dades RAW (lectura després d'escriptura) degut a registres es detecten en l'etapa D. Quan es detecta un risc, es bloquegen les etapes D, B i CP. El processador no utilitza cap mecanisme per gestionar riscs WAW (escriptura després d'escriptura) degut a registres. Les instruccions han d'estar ordenades convenientment per a que les dependències de sortida no produeixin risc. Per interpretar instruccions de tipus BCE, el processador utilitza predicció de sentit. En l'etapa D es fa la predicció, es calcula l'adreça destí de salt i es modifica el seqüenciament si el literal (d) és negatiu. La verificació de la predicció es fa en l'etapa ALU i s'estableix el seqüenciament en cas de detectar error. L'interpretació de les instruccions BCF s'explica més endavant. El processador executa el següent fragment de codi: for (i=1; i<N; i++) x[i] = x[i] + x[i-1]; for: Fload f0,0(r0) i1 Fload f1,-8(r0) i2 Fadd f1,f0,f1 i3 Fstore f1,0(r0) i4 Add r0,r0,r3 i5 Cmpgt r1,r0,r2 i6 Beq r1,for i7 Valors inicials: r3=8; r0=adreça primer element del vector; r2=adreça últim element del vector Pregunta a: Mostra el cronograma d'execució d'una iteració i de la primera instrucció de la següent iteració. Assenyala els curtcircuits utilitzats mitjançant la notació (x,y), on x i y representen les entrades i sortides, respectivament, dels mòduls XCE i XCF. Calcula el CPI. El compilador pot reordenar les instruccions i modificar els literals de les instruccions d'accés a memòria per reduir els cicles perduts. Pregunta b: Mostra el codi planificat i els literals de les instruccions d'accés a memòria. Per cada instrucció d'una iteració i la primera de la següent iteració, indica en quin cicle de rellotge la lògica de control detecta que està Llesta. Calcula el nou CPI i el Guany obtingut per la planificació. La figura mostra els multiplexors d'encaminament de dades del mòdul XCF. Els senyals de control dels multiplexors es calculen en l'etapa LF. 2 (Fa) c3 0 c1 0 1 (Fb) 3 1 a 0 0 1 b 1 XCF c4 c2 Pregunta c: Utilitzant comparadors i portes lògiques, dissenya el circuit de control del mòdul XCF. No cal considerar els bits de validesa. Per detectar els riscs de dades, la lògica de control utilitza dos vectors de marques, VME i VMF. El vector VME conté tants bits com registres enters i el vector VMF tants com registres de punt flotant visibles a nivell de llenguatge màquina. Cada entrada d'un vector indica si el registre associat està disponible (valor 0) o si s'està calculant (valor 1). L'escriptura en aquests vectors està sincronitzada amb el flanc de pujada del senyal de rellotge. En el cas de que el retard productor-us sigui igual a 1 cicle, la instrucció productora no actualiza els vectors de marques. Suposa que el contingut d'una entrada de qualsevol vector de marques es pot escriure i llegir, en aquest orde, en el mateix cicle. Examen, enero de 2009 5 Dep. Arquitectura de Computadores FACULTAD DE INFORMATICA ARQUITECTURA DE COMPUTADORES Pregunta d: Per cada tipus d'instrucció que modifica l'estat en registres, encercla els flancs de pujada del senyal de rellotge on s'escriuen els vectors de marques. Dedueix el nombre de ports d'escriptura dels vectors VME i VMF. Pregunta e: Dissenya la lògica per avaluar si la instrucció que ocupa l'etapa D està Llesta. No cal considerar els bits de validesa. Afegim un mecanisme que no requereix bloqueig per interpretar concurrentment instruccions amb dependència de sortida. El mecanisme es basa en que instruccions que s'executen en la mateixa ramificació no poden provocar risc WAW. Per tant, és suficient en anul•lar l'escriptura de la instrucció origen de la dependència quan s'executa en una ramificació distinta de la instrucció destí. Per cada banc, disposem d'un vector amb tantes entrades com registres lògics (VRE i VRF). Cada entrada indica la ramificació que calcularà el resultat en el registre associat. Suposarem la següent codificació per les ramificacions: 0 (ALU), 1 (MEM) 2 (PF). L'escriptura en aquests vectors està sincronitzada amb el flanc de pujada del senyal de rellotge. Un vector s'actualitza quan la lògica de control detecta que la instrucció que ocupa l'etapa D està llesta. L'avaluació del senyal del permís d'escriptura es fa en l'etapa d'escriptura tenint en compte el contingut de VRE o VRF (d1,d0). Suposa que el contingut d'una entrada de qualsevol vector es pot escriure i llegir, en aquest orde, en el mateix cicle. Observa que el mecanisme descrit també anul•la l'escriptura de la instrucció origen de la dependència de sortida fins i tot en ocasions on la instrucció destí no provoca risc. La figura mostra el circuit que controla les escriptures de la ramificació de punt flotant. Des de l'etapa D s'injecta per la cadena de registres l'identificador del registre lògic que actualitzarà (FdD). FdEF VRF '10' FdD d1d0 LlestaPF LF X1 X2 X3 X4 EF CTRL_PE PEF PEEF Pregunta f: Dissenya amb portes lògiques el circuit CTR_PE que avalua el senyal de permís d'escriptura de la ramificació de punt flotant (PEEF). L’incorporació d'aquest mecanisme per gestionar els riscs WAW requereix modificacions del mecanisme que gestiona els riscs RAW, en concret, l'actualització del vectors de marques VME i VMF. Pregunta g: Dedueix una seqüència de 3 instruccions de tipus CF que posi de manifest la necessitat de modificar el mecanisme de gestió dels riscs RAW. Es vol utilizar també predicció de sentit segons el signe del literal per interpretar eficientment les instruccions de salt condicional de tipus BCF. La predicció es fa en l'etapa D, modificant el seqüenciament si el literal és negatiu. La verificació de la predicció es fa en l'etapa X1 i s'estableix el seqüenciament en cas de detectar error. Pregunta h: Pel cas d'error de predicció, dedueix el nombre màxim d'instruccions que hauria de descartar la lògica de control. Indica també si és possible que alguna de les instruccions a descartar actualitzés l'estat abans de detectar un error de predicció. Si així fos, proposa un mecanisme per evitar-ho. Examen, enero de 2009 6 Dep. Arquitectura de Computadores FACULTAD DE INFORMATICA ARQUITECTURA DE COMPUTADORES EJERCICIO 3: (3.5 puntos) PSTOM es un procesador segmentado con planificación dinámica y algoritmo de control con renombre dinámico de registros (Tomasulo), que tiene 4 ramas de ejecución con segmentación lineal en todas. Tiene 9 estaciones de reserva (ER). Cada rama tiene una pareja de buses de difusión de datos y de etiquetas (BD y BE) que están conectados a toda ER y a todo BReg. En el mismo ciclo en que se escriben BD y BE se puede capturar su información. La rama ENT/BRC con 1 ciclo de ejecución y 2 ER numeradas 1 y 2 . La rama FSUM con 2 ciclos de ejecución y 2 ER numeradas 3 y 4 . La rama FDIV con 4 ciclos de ejecución y 1 ER numerada 5. La rama MEM con 3 ciclos de ejecución y 4 ER numeradas 6 y 7 (para FLD) , 8 y 9 (para FST). Ejecuta las instrucciones BRC con predicción fija (estática), apostando siempre por romper la secuencia. Tiene un sumador en la 3ª etapa para calcular direcciones destino de salto, comprueba la predicción en la 4ª etapa y en ella se establece el secuenciamiento en caso de detectar error. La instrucción se decodifica, y se decide si se emite o no y si se inicia o no, todo ello en la 3ª etapa. PSTOM ejecuta el código siguiente, que es un bucle que itera varias veces, y tiene 10 instrucciones 1 2 3 4 5 6 7 8 9 10 FLD FLD ENT FLD FSUM FSUM ENT FDIV FST BRC $: F1 <---- M[R1 + 0] F2 <---- M[R1 + 4] R0 <---- R0 - 1 F3 <---- M[R1 + 8] F1 <---- F1 + F2 F3 <---- F3 + F1 R1 <---- R1 + 12 F2 <---- F3 / 3 M[R1 - 4] <---- F2 saltar a $ según (R0) Pregunta a: Construya el grafo de dependencias de datos del código. Presente por separado el grafo de cada tipo de dependencia, e identifique cada instrucción por su número del 1 al 10. Preguntas b, c: Suponemos que PSTOM tiene dos subramificaciones en la rama MEM y puede adelantar las FLD cuando no tengan riesgo de lectura de datos en memoria. Presente el cronograma de ejecución de la primera iteración y las 4 primeras instrucciones de la segunda iteración. Debe identificar el nº de la ER que ocupa cada instrucción al emitirse (p.ej. EL6). Calcule el número de ciclos que transcurren entre los ciclos en que se completa la 1ª instrucción de la primera y de la segunda iteración. Diga en qué ciclos se escribe en el registro F2 del BReg. Pregunta d: Indique en qué ciclos se producen capturas de la información que transportan los buses de difusión. Para cada captura debe señalar el nº de la ER que produce la información capturada. Pregunta e: Indique el número que identifica a cada ER que está ocupada durante el ciclo 11 de la ejecución. Pregunta f: Sin presentar ningún cronograma, calcule el número de ciclos que transcurren entre los ciclos en que se completa la 1ª instrucción de la primera y de la segunda iteración , suponiendo ahora que PSTOM no puede adelantar las FLD y mantiene estricto orden de programa en la ejecución de todas las instrucciones de la rama MEM. Examen, enero de 2009 7 Dep. Arquitectura de Computadores FACULTAD DE INFORMATICA ARQUITECTURA DE COMPUTADORES PSMAR es un procesador segmentado con planificación dinámica y algoritmo de control Marcador (Scoreboard) , que tiene 4 ramas de ejecución no segmentadas. Cada rama tiene 2 caminos de lectura y 1 de escritura con su Banco de Registros (BReg). No tiene ningún cortocircuito. Ningún registro de BReg puede ser escrito y leído en el mismo ciclo. Cada rama tiene estas latencias de ejecución: rama 1 : MEM , 3 ciclos ; rama 2 : FMUL , 3 ciclos ; rama 3 : FSUM , 2 ciclos ; rama 4 : ENT , 1 ciclo La instrucción se decodifica, y se decide si se emite o no y si se inicia o no, todo ello en la 3ª etapa. PSMAR ejecuta el código siguiente, con 7 instrucciones: 1 2 3 4 5 6 7 FLD FMUL FLD FSUM ENT FST ENT F2 <---- M[R1 + 0] F4 <---- F2 x F0 F6 <---- M[R2 + 0] F6 <---- F4 + F6 R1 <---- R1 + 4 M[R2 + 0] <---- F6 R2 <---- R2 + 4 Pregunta g: Construya el grafo de dependencias de datos del código. Presente por separado el grafo de cada tipo de dependencia, e identifique cada instrucción por su número del 1 al 7. Preguntas h, i: Presente el cronograma de ejecución del código. Debe identificar el nº de la rama cuando se emite cada instrucción (p.ej. EL1). Escriba en qué ciclos está desocupada la rama 1, y en qué ciclos están simultáneamente ocupadas las ramas 3 y 4. Pregunta j: Identifique cada ciclo de bloqueo (en los que no se emite ninguna instrucción) y explique el motivo de cada uno de ellos. Examen, enero de 2009 8 Dep. Arquitectura de Computadores