Diseño e Implementación de una Tarjeta PCI Basada en una FPGA

Anuncio

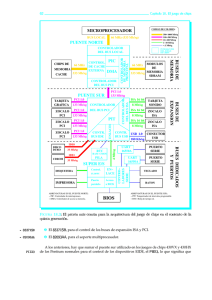

DISEÑO E IMPLEMENTACIÓN DE UNA TARJETA PCI BASADA EN UNA FPGA C. E. Torres, R. Nieto, A. Bernal camiloe@hotmail.com; rnieto@univalle.edu.co; alvaro@univalle.edu.co Grupo de Arquitecturas Digitales y Microelectrónica Universidad del Valle SUMMARY In this work all necessary steps for interfacing the PCI bus ( Peripheral component interconnect ) is presented. The required conditions for transferring data using this bus were taken in count and quietly discussed. An interface that let program a FPGA was developed and tested. Using this capacity the card is able to execute any function required for the user keeping the availability of continuous programming. Other important points consists in allowing to the user to establish a bus PCI interface in order to program the FPGA and transfer data through the bus PCI. High frequencies design require some careful when the interconnections between the different devices signals are done, this kind of requirements are also discussed. RESUMEN En este trabajo están todos los pasos necesarios para realizar una interfaz con el bus PCI. Se discuten y se tienen en cuenta las condiciones requeridas para realizar transferencias de datos en este bus. Se desarrolló y se probó una interfaz que permite la programación de una FPGA. Usando esta capacidad la tarjeta puede ejecutar cualquier función que sea requerida por el usuario y mantener la disponibilidad para una continua programación. Otro punto importante consiste en permitir al usuario establecer una interfaz con el bus PCI para programar la FPGA y para transferir datos a través del bus PCI. También se discuten los cuidados requeridos para la interconexión de las diferentes señales entre dispositivos que operan a alta frecuencia. DISEÑO E IMPLEMENTACIÓN DE UNA TARJETA PCI BASADA EN UNA FPGA C. E. Torres, R. Nieto, A. Bernal camiloe@hotmail.com; rnieto@univalle.edu.co; alvaro@univalle.edu.co Grupo de Arquitecturas Digitales y Microelectrónica Universidad del Valle ABSTRACT In this paper the principal problems for interfacing the PCI bus are discussed. Also different approaches oriented to solve these obstacles are discussed. One of the implemented strategies consists in developing an interface based on FPGAs which becomes an intelligent interface that can be used to general purposes, more specifically in data acquisition. 1. INTRODUCCIÓN Uno de los principales componentes de hardware en los computadores personales es su arquitectura de bus de expansión. Por lo general esta es la forma básica con la cual se ensamblan los elementos de hardware en la tarjeta madre. Los tres tipos principales de arquitecturas de bus que se usaron son: la arquitectura estándar de la industria (ISA), la arquitectura estándar de la industria extendida (EISA), y la arquitectura microcanal (MCA). Además de estas tres arquitecturas se encontraban: el bus de la asociación de estándares de la electrónica de video (VLB o VL-Bus), la interfaz de sistemas de computadoras pequeñas (SCSI) y el bus de interconexión de periféricos (PCI). En un principio había varias desventajas en el bus de expansión original del PC de IBM. Cada vez que se iban efectuando mejoras se tenía como base fundamental la compatibilidad hacia atrás. Esto permitió que los usuarios conservaran el hardware existente y los fabricantes continuaran produciendo sus tarjetas de expansión. En consecuencia, el estándar IBM se convirtió en el estándar de la industria, y la arquitectura de bus llegó a ser conocida como la arquitectura estándar de la industria o ISA. INTEL empezó a trabajar en 1990 en el bus PCI pensando en sus sistemas basados en el PENTIUM. Muy pronto INTEL cedió sus patentes al dominio público y promovió la creación de una asociación industrial, la PCISIG, para continuar el desarrollo y mantener la compatibilidad de las especificaciones del PCI. El resultado ha sido que el PCI ha sido ampliamente adaptado y se esta incrementando su uso en los computadores personales, estaciones de trabajo y servidores de sistema [1]. La gran adaptación del bus PCI en los computadores personales, lo ha convertido en el bus estándar. En este trabajo se desarrolló una tarjeta que permitiera el uso del bus PCI para diferentes aplicaciones y que se adaptara a diferentes tipos de interfaces. Se realizó el estudio del protocolo de comunicación y una minuciosa inspección del sistema de interconexión entre los dispositivos. Se analizaron todos los detalles y criterios de ingeniería que implicaban el diseño de sistemas digitales de alta velocidad para el desarrollo de una tarjeta PCI que permite la configuración de la FPGA para aplicaciones genéricas, conservando las características del bus PCI para la transmisión y recepción de datos. 2. EL BUS PCI El bus PCI (“Peripheral Component Interconnect”), es un bus de ancho de banda elevado, independiente del procesador que se emplee como bus de periféricos. Comparado con otras especificaciones comunes de bus, el PCI proporciona mejores prestaciones para los subsistemas de E/S de alta velocidad (Por ejemplo los adaptadores de pantalla gráfica, los controladores de interfaz de red, los controladores de disco, etc) [2][3]. Unas de las principales ventajas que trae consigo el diseño sobre el bus PCI son el bajo costo, la flexibilidad y la arquitectura de bus estándar con el más alto rendimiento. Algunas de sus características mas relevantes son: • • Proporciona un conjunto de funciones de uso general. Utiliza temporización síncrona y un esquema de arbitraje centralizado. • • • • • • • • • • • Presenta independencia del procesador, soportando diferentes familias. Bajo consumo de potencia, un objetivo principal de la especificación PCI, es dar soporte a la creación de diseños donde los requerimientos de corriente sean mínimos. Las transferencias burst se pueden realizar en lectura y escritura, un bus de 32 bits soporta hasta 132 Mbytes/s como rata de transferencia pico en lectura o escritura y 264 Mbytes/s en transferencias de 64 bits. Si el bus pertenece a la versión 2.2. puede alcanzar picos de transferencia hasta 528 Mbytes/s a 66 MHz. Velocidad del bus: Versión 2.0 tope de velocidad 33 MHz. Versión 2.2 tope de velocidad 66 MHz. Versión 2.3 tope de velocidad 66 MHz. PCI-X Tope de velocidad 1 Ghz. Tiempo de acceso de 60 ns. a 33 MHz. Soporta dispositivos maestros, un maestro PCI puede acceder a otros dispositivos del bus, a memoria principal o a periféricos dentro de otros buses. Arbitración oculta, lo cual significa que la tenencia del bus se resuelve mientras un maestro efectúa transferencias y sin necesidad de entrar en tiempos muertos. Revisión de la integridad: todas las direcciones, datos y comandos tienen asociado un bit de paridad. Tres espacios direccionables: memoria, puertos y configuración. Autoconfiguración, el espacio de configuración permite la operación del dispositivo como Plug and Play. La especificación define un tamaño de conectores y tres tamaños de tarjeta. 2.1. Inicialización Ninguno de los elementos que conforma un sistema PCI se encuentra configurado al ser energizado, es decir, no hay rangos de direcciones de memoria o puertos asignados, y tampoco tiene interrupciones disponibles. Para que un dispositivo opere en el bus PCI, sea un dispositivo maestro o esclavo, debe estar configurado. Para realizar las operaciones de configuración se requiere de un elemento que transmita la información que caracteriza al dispositivo hacia el host, para posteriormente realizar la lectura de la información que el host ha asignado a este elemento. La información del espacio de configuración es guardada en una memoria nVRAM que se encuentra comunicada con un controlador PCI, el cual es el encargado de la transmisión / recepción de datos a través del bus PCI. La configuración se realiza a través de lecturas del espacio de configuración hechas por el controlador. Este proceso se realiza para cumplir con los requerimientos del dispositivo, los cuales fueron hechos durante la etapa de escrituras en el espacio de configuración y consisten en la transmisión de los datos contenidos en la memoria nVRAM de la tarjeta hacia el espacio de configuración, para posteriormente realizar un proceso de lectura de este espacio y determinar los recursos asignados por el sistema como lo son el espacio de memoria asignado, las direcciones de puertos disponibles y la asignación de interrupciones. Estas acciones hacen parte de las principales características de los dispositivos plug and play. Debido a su condición de bus estándar es muy fácil encontrar equipos con el bus PCI en su arquitectura. En el momento que se requiera realizar interfaces compatibles y portátiles, con casi cualquier equipo, el bus PCI sería la primera opción a tener en cuenta. 3. CONSIDERACIONES DE DISEÑO PARA EL HARDWARE Las consideraciones de diseño a tener en cuenta en la implementación de la tarjeta PCI son los siguientes: potencia consumida, compatibilidad de las familias de los integrados, análisis de tiempos, geometría y ubicación de los dispositivos, desacople y el espacio de configuración. 3.1 Potencia Las tarjetas PCI poseen un límite máximo de suministro de potencia de 25 W. De acuerdo a la potencia consumida por cada uno de los elementos, se debe calcular la potencia máxima que puede disipar el empaquetado de cada uno de los integrados. Con el cálculo de la potencia máxima disipada se puede establecer la máxima temperatura ambiente en que puede operar la tarjeta sin daños a los integrados que la componen y justificar el uso de disipadores. La FPGA por ser un dispositivo reprogramable, posee características diferentes a los demás circuitos integrados. El consumo de potencia en las FPGAs Spartan II depende del número de transiciones lógicas en su interior y es proporcional a la frecuencia del reloj de operación. Los valores de potencia consumida, resistencia térmica del empaquetado, flujo de aire y temperatura ambiente se deben tener en cuenta en el momento que se selecciona el tipo de encapsulado del dispositivo. Sin el adecuado análisis térmico, el calor generado puede exceder la temperatura máxima soportada por el dispositivo y provocar daños permanentes. El consumo de potencia en la FPGA depende en gran medida del diseño configurado en su interior (core). Se debe realizar una estimación precisa de los requerimientos de la FPGA para brindar al sistema un suministro de potencia adecuado a estos. La familia de FPGAs Spartan II requiere un suministro de corriente mínimo, al cual se hace referencia en sus hojas de datos como Iccpo, con una valor de 500 mA a temperaturas por encima de 0 ºC para garantizar una activación satisfactoria. Los requerimientos solo se aplican durante el período de activación (normalmente, unos cuantos milisegundos). Ya en funcionamiento las valores de corriente son considerablemente bajos en comparación con los valores de inicialización. Al aplicar potencia a la FPGA durante la inicialización, el dispositivo exige una intensidad de corriente considerablemente alta en comparación con la exigencia de corriente en pleno uso. Esta característica se debe fundamentalmente a que es un dispositivo que se basa en celdas SRAM. Las FPGAs son elementos que se programan por el almacenamiento de datos de configuración en celdas tipo SRAM que se encargan de desactivar o activar las líneas de interconexión internas. Antes de la inicialización las celdas SRAM almacenan valores aleatorios, lo que provoca colisiones, que motiva a un elevado consumo de corriente durante la inicialización. Para la utilización de este tipo de dispositivos se requiere contar con reguladores especiales, que cumplan con las siguientes características: • • Reguladores tipo LDO (Low Drop Out) los cuales se caracterizan por tener fugas de corriente mínimas. Protección contra sobre corriente mayor a 1A para que el regulador logre suministrar la suficiente corriente para que el dispositivo se active y comience con la fase de configuración. 3.2 Compatibilidad de integrados Al realizar la interconexión con diferentes familias de dispositivos, se debe asegurar una compatibilidad en sus niveles umbrales. Estas especificaciones se pueden encontrar en las hojas de datos de cada uno de los elementos y son decisivos para determinar que circuitos integrados serían utilizados en la tarjeta. VOHmin,VOLmax,VIHmin,VILmax constituyen los valores que se deben considerar en los niveles de voltaje. De acuerdo con estas definiciones un circuito integrado compatible entregaría un valor de voltaje a su salida mayor que VOHmin para un nivel alto y menor que VOLmax para un nivel bajo y aceptaría en sus entradas un voltaje mayor que VIHmin para un nivel alto y un voltaje menor que VILmax para un nivel bajo. Para resolver este problema de compatibilidades la FPGA cuenta con una entrada de polarización (Vcco) que permite ajustar sus valores umbrales. Para una correcta relación de niveles umbrales la entrada de polarización es Vcco =3.3 V, lo que permite que la FPGA sea compatible con los niveles umbrales del controlador PCI S5920 que presenta los valores VOHmin=2.4V, VOLmax=0.4V, VIHmin=2.0V, VILmax=0.8V. En relación con estos valores se escogió el nivel de polarización de 3.3V para obtener las características de entrada y salida dadas por VOHmin=2.4V, VOLmax=0.4V, VIHmin=2.0V, VILmax=0.8V. Al poseer los mismos valores umbrales para las entradas y salidas estos dispositivos son totalmente compatibles, sin olvidar que la FPGA es un dispositivo que esta alimentado a 2.5 V, es tolerante a las entradas de 5V y tolera un valor máximo de 5.5 V en sus entradas. [4][5] 3.3 Análisis de tiempos Cada una de las señales transmitidas debe cumplir con tiempos de establecimiento que aseguren la captura de las señales en su nivel correcto. Estos valores son determinantes a la hora de la elección de los dispositivos para el establecimiento de una interfaz completamente funcional. Todas las operaciones de los circuitos son realizadas, en su mayoría, de manera síncrona. En cada período de reloj se deben tener en cuenta varios eventos ocurridos en esta transición, debido a que nada ocurre instantáneamente. Los principales tiempos a tenerse en cuenta para la realización de una interfaz síncrona son el tiempo sostenido del dato después de terminado el período (TSD) y el tiempo para obtener un dato válido (TVD). En la figura 1 se observan los tiempos que deben ser tenidos en cuenta para realizar la comunicación entre dispositivos sincronizados con una misma señal de reloj. Figura 1. Identificación de los tiempos críticos para la captura de un dato • La conexión de los trazos de la señal de reloj del S5920 al bus PCI debe ser de 2.5 pulgadas +/-0,1 pulgadas en longitud y se pueden rutear únicamente a una carga. Se debe asegurar que todas las esquinas de estos trazos son redondeadas y no usar ángulos de 90º. • La impedancia de los trazos de la señal PCI en la tarjeta de expansión debe ser mantenida dentro del rango de los 60 y 100 Ohms. Teniendo en cuenta el tiempo TVD de un dispositivo que suministra una salida, el dispositivo que captura el dato debe hacerlo después de transcurrido este tiempo TVD para obtener un dato válido. Algunos dispositivos que realizan la captura de datos por flancos de reloj, requieren que los datos sean sostenidos por un tiempo mínimo después del flanco de reloj, en este instante es fundamental tener en cuenta el tiempo TSD. Este tiempo TSD debe ser mayor en el elemento transmisor que el tiempo mínimo requerido por el dispositivo receptor para el almacenamiento de un dato válido. Estando de acuerdo con estos dos conceptos, se debe determinar que tiempos corresponden a cada uno de estos valores para asegurar la captura de los datos transmitidos. Este concepto es aplicable a todas las señales de control y de datos durante una transferencia síncrona, lo cual se debe tener en cuenta a la hora de la elección de los circuitos integrados. 3.4 Geometría y ubicación de los dispositivos Cada uno de los elementos que componen la tarjeta deben cumplir con unos requerimientos de espacio máximo para que la tarjeta este catalogada en los tamaños de tarjeta PCI. Por ser un diseño con componentes que trabajan a una frecuencia mayor de 25 MHz es considerado un diseño de alta frecuencia. Teniendo en cuenta las ratas de transmisión de datos se observa claramente que el tiempo que toma un dato en llegar de un dispositivo a otro es comparable con los valores de los tiempos de transición de la señal de reloj, por lo cual los dispositivos no pueden ser ubicados en cualquier parte de la tarjeta y deben cumplir con una longitud e impedancia máxima en las líneas de datos / control y otras condiciones para la señal de reloj. Las operaciones de transferencias del bus PCI pueden ocurrir en 30 ns con señales de rizado y tiempos de caída de 3 ns. Se tiene especial cuidado con la longitud de los trazos y el ruteamiento para prevenir problemas de impedancia y preservar el rizo de la señal y los tiempos de caída. Las especificaciones PCI requieren seguir los criterios de diseño para todos los controladores de bus PCI: • La longitud de los trazos para cada una de las interfaces de datos de 32 bits del S5920 al bus PCI está limitada a un máximo de 1.5 pulgadas para todas las tarjetas de 32 bits. 3.5 Desacople Uno de los principales aspectos a diseñar es el relacionado con el desacople. A través del desacople se suministra un medio por el cual se separan las funciones de los circuitos integrados de los eventos ocurridos en el suministro de potencia. Esto se realiza a través de capacitores de desacople. La falta de un correcto desacople incrementará la generación de ruido y el circuito será susceptible a fallas. Para la determinación de los valores de los capacitores a utilizarse en el desacople, se debe calcular la frecuencia de resonancia de estos, los capacitores tienen un modelo RLC serie con el cual se determina la frecuencia de resonancia, este valor de frecuencia es el que nos permite establecer en que rango de frecuencias los capacitores cumplen con su función de desacople, un valor errado de estos haría que el capacitor solo ocupara espacio en el circuito impreso. 3.6 Espacio de configuración Todas las funciones PCI deben permitir la implementación de un espacio de configuración en el que deben residir los registros de configuración. El puente host / PCI puede contener estos registros en espacio de configuración PCI, en espacio de puertos o en espacio de memoria. Cada dispositivo PCI posee un bloque de 64 palabras de configuración. Se realizó un estudio detallado del espacio de configuración PCI para determinar sus principales características y la manera cómo determinan el funcionamiento del sistema. En este espacio se almacenan los valores que identifican a cada uno de los dispositivos en el bus PCI, sus fabricantes, funciones soportadas, espacio asignado por el sistema entre otros [6]. En la figura 2 se muestra un diagrama del espacio de configuración PCI. Figura 3. Diagrama de bloques del sistema 5. FUNCIONAMIENTO DEL HARDWARE Figura 2. Espacio de configuración PCI 4. DESCRIPCIÓN DE LA TARJETA La tarjeta se compone de los siguientes elementos que hacen parte de su arquitectura: • • • • • Controlador PCI S5920, realiza la comunicación con el procesador central a través del bus PCI.. Microcontrolador AT90S2313 se encarga de realizar el control sobre las señales de programación de la FPGA, recibiendo órdenes enviadas por el procesador central que se comunican a el microcontrolador a través del bus de datos del S5920. La FPGA XC2S100 que se configura para realizar las acciones necesarias para el desarrollo de diferentes proyectos, además de la lógica de control para la transmisión de datos hacia el host por medio de los canales de comunicación que suministra el S5920. Conversores A/D y D/A para realizar acciones de adquisición de datos y transmisión de señales de control. Controlador de Interfaz ICL-232 para la implementación del protocolo RS-232 para comunicación de datos. En la figura 3 se puede observar un diagrama de bloques de los elementos que componen el sistema. Un sistema que se conecte al bus PCI debe implementar su espacio de configuración de acuerdo con las especificaciones de la aplicación que se quiere implementar. Una vez se energiza el sistema se realiza una comunicación entre los dispositivos PCI y el sistema operativo. A través de esta comunicación el sistema operativo reconoce los dispositivos, valida sus funciones y asigna el espacio físico en donde será ubicada la tarjeta. El dispositivo S5920 cuenta con dos líneas de comunicación con una memoria nvRAM, en donde se guardan todos los datos que el usuario requiere en el espacio de configuración PCI. Esta interfaz permite cargar al sistema operativo los valores requeridos para operación de la tarjeta; dejándose abierta la posibilidad de modificarse según la aplicación lo exija. El bus PCI se caracteriza por soportar dispositivos maestros y esclavos. Por lo tanto el sistema de arbitración asigna permanentemente la posesión del bus a diferentes maestros que lo hallan requerido. Por tal motivo el S5920 no puede apropiarse del bus permanentemente y realizar una transmisión continua de los datos. Debido a esta situación se opta por configurar la FPGA en modo esclavo paralelo. El modo esclavo paralelo permite realizar la transmisión de las tramas de configuración de la FPGA en paquetes e ignorando transiciones del reloj de configuración. El control de la interfaz de programación se realiza a través de el microcontrolador AT90S2313 de Atmel, quien se encarga de controlar la transmisión de los datos de configuración hacia la FPGA. Esta función la realiza activando las señales de programación de la FPGA ( CS#, WRITE# y PROGRAM# ) durante el tiempo necesario para la inicialización de los dispositivos y captura de los datos de configuración por parte de la FPGA. Las principales AT90S2313 son: funciones del microcontrolador • Activar los modos de programación o readback de la FPGA • Dar información sobre el estado de los dispositivos al host a través de los canales de comunicación del S5920. 6. 7. SOFTWARE DE INTERFAZ MODO DE OPERACIÓN La tarjeta puede ser utilizada en diversos campos para los cuales se deben seguir los siguientes pasos para implementar diferentes tipos de proyectos. • dispositivos de transmisión/adquisición de datos y los controladores de interfaces. Diseño del núcleo digital: desarrollo de toda la interfaz digital que se va a programar en la memoria de configuración de la FPGA. Para realizar este proceso se cuenta con el uso de diferentes herramientas CAD. El fabricante suministra diferentes tipos de software de implementación como el Fundation, Alliance y Web-pack (Software que distribuye Xilinx.), este último de libre distribución. El software utilizado para el desarrollo de los diseños digitales es el Web-pack. Este cuenta con un navegador de proyectos que permite la utilización de interfaces de programación, tales como: VHDL, Verilog, ABEL, captura esquemática, diagramación de estados. Se puede implementar cualquier tipo de diseño digital utilizando cualquiera de las interfaces anteriormente mencionadas. Una vez realizada la descripción del diseño digital, utilizando alguna de las interfaces, se procede a corroborar la posibilidad física de cumplir con las especificaciones dadas en el diseño. • Síntesis del diseño: en este proceso se realizan la compilación del diseño y se verifica el cumplimiento de los estándares. • Generación del archivo de configuración: corresponde a las acciones hechas por el compilador seleccionado para la optimización del diseño en la FPGA que termina con la generación del archivo de configuración. • Programación: proceso que tiene como función realizar la configuración de la FPGA para el cumplimiento de una tarea específica. • Evaluación y test del sistema: se evalúa el comportamiento y funcionalidad del sistema para la aplicación especifica. Con la posibilidad de implementar diferentes alternativas de control en la FPGA para los El software de interfaz permite al diseñador encontrar la ubicación de la tarjeta en el PC, ya sea en puertos o en memoria. Además de contar con las funciones que permiten realizar escrituras/lecturas en las direcciones de puertos o memoria asignados a la tarjeta por el espacio de configuración PCI. Contiene las opciones necesarias para realizar el proceso de configuración de la FPGA a través de la transmisión del archivo de configuración resultado de la síntesis del diseño digital que se quiere implementar en al FPGA. Con las opciones de lectura de los registros mailbox del chipset S5920, se puede verificar los estados de la FPGA, es decir, las operaciones de inicialización y arranque de este dispositivo. Crea una interfaz de comunicación con el microcontrolador AT90S2313 a través de del canal mailbox del S5920 para la activación de los diferentes modos operación que tiene el S5920 que sólo pueden ser activados a través del hardware. 8. POSIBLES APLICACIONES El sistema, debido a su capacidad de reprogramación, puede ser usado para los siguientes tipos de aplicaciones: • • • • • • • Adquisición de datos Transmisión de señales de control Implementación de protocolos comunicaciones. Conversión de protocolos Prototipado de arquitecturas digitales Instrumentación. Sistemas en tiempo real. de En la figura 4 se muestra una fotografía del sistema implementado en donde se observa claramente la ubicación de cada uno de sus componentes. En los procesos de adquisición de datos, se determina si la palabra de configuración del conversor A/D es el caso óptimo para la aplicación que se esta haciendo, teniéndose la opción de implementar diferentes alternativas para la optimización del proceso de adquisición de datos. Figura 4. Fotografía del sistema. Se observan las ventajas de poseer dos modos de operación, lo que permite al usuario la implementación de sistemas autónomos para la transmisión de datos o sistemas que dependen de las condiciones o eventos ocurridos exteriormente a la tarjeta. 10. RESULTADOS 9. CONSIDERACIONES Se experimentó con los diferentes anchos de bus que permite el S5920 para la transmisión de datos y evaluar su comportamiento, al ubicar la tarjeta en espacio de memoria y en el espacio de puertos. Al ubicar la tarjeta en el espacio de memoria, se requiere de un conocimiento profundo en la estructura del sistema operativo que se esta utilizando, debido al manejo que este le da a la memoria, lo cual puede provocar retardos en la transmisión de los datos. Al verificarse la funcionalidad con diseños combinacionales en la FPGA, se puede observar una gran potencia en procesamiento de las señales liberando de carga al procesador central. La interfaz de configuración opera a una frecuencia de 10 MHz, lo cual no implica que no se pueda realizar operaciones de adquisición de datos a mayor frecuencia. Se probaron operaciones de muestreo a 20 MHz que almacenan los datos en registros internos implementados en la FPGA para después ser transmitidos hacia el host. Se evaluaron diferentes clases de diseños digitales, tanto combinacionales como secuenciales demostrándose el amplio rango de aplicación que tiene la tarjeta. La importancia de las características genéricas se fortalecen al utilizar la FPGA para la configuración de los conversores A/D y D/A, que son dispositivos programables, a través de protocolos seriales de comunicación por medio de los cuales se configuran estos dispositivos aumentando más la flexibilidad de la tarjeta. Entre otros, los resultados obtenidos mas relevantes están relacionados con la concepción, diseño, implementación y verificación del sistema de desarrollo de la tarjeta para bus PCI basada en una FPGA Este objetivo final requirió del análisis y estudio de la estructura de interconexión del sistema , de los modos de programación de la memoria de configuración PCI, de la programación y evaluación de diferentes tipos de diseños digitales combinatoria. de lógica secuencial y De igual forma se diseñó e implementó el software de interfaz, se hizo reconocimiento del software de aplicación, asó como la validación final del prototipo de la tarjeta. 11. CONCLUSIONES Se estudió y utilizó el protocolo de transmisión de datos a través del bus PCI a fin de diseñar, implementar y verificar el funcionamiento de una tarjeta PCI para adquisición de datos basada en una FPGA. Se desarrolló un software de interfaz capaz de realizar lecturas del espacio de configuración PCI, de programar una FPGA y de ejecutar las tareas de transmisión y recepción de datos. La funcionalidad del sistema se validó mediante el uso de herramientas de diseño digital (VHDL, captura esquemática.) Se validó la operación de la FPGA como interfaz maestra que se adapta a los diferentes modos de operación de los dispositivos con los cuales se requiere establecer comunicación. 12. BIBLIOGRAFÍA Se implementó una herramienta reprogramable que se conecta directamente con el PC. La capacidad de reprogramación suministra una gran cantidad de posibilidades para la implementación de diferentes sistemas, sean para adquisición de datos o para el prototipado de diferentes arquitecturas digitales. Se elaboró una interfaz de programación que permite la utilización del bus PCI para otras aplicaciones, una vez se halla programado la FPGA, asociando el potencial de cálculo de los computadores personales con la capacidad de reprogramación que ofrece la FPGA. [1] SHANLEY Tom; ANDERSON Don-1999. PCI SYSTEM ARCHITECTURE ,Fourth Editions,Ed: Addison Wesley Mayo de 1999. [2] MESSMER, Hans-1997. The indispensable PC hardware book. pag 586-643. Tercera edición. Addison Wesley.1997. [3] JIMÉNEZ, Henry; ACOSTA, Carlos-2001] Tarjeta genérica PCI – Interfaz GPIB. Santiago de Cali: 2001. Trabajo de grado (Ingeniería electrónica). Universidad del Valle. Facultad de ingeniería. Escuela de Ingeniería Eléctrica y Electrónica. [4] PCIPROD-AMCC-1998. PCI PRODUCTS DATA BOOK: 1998. Applied Micro Circuits Corporation. [5] XILINX-2002. THE PROGRAMMABLE LOGIC DATA OOK; San José, CA: 2002. [6] PCI REV. 2.2-1998. PCI LOCAL SPECIFICATION REV. 2.2. PCISIG: 1998. BUS

![Descargar - [ [ [ ANSEL ] ] ]](http://s2.studylib.es/store/data/005807843_1-39498269826d9ab30dac33202061ffe6-300x300.png)