(C) Mario Medina C. 1 Estructura de una CPU 8088

Anuncio

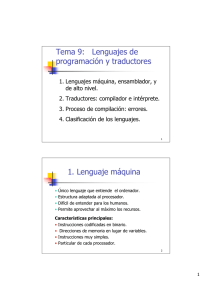

Procesadores Intel x86

Familia de microprocesadores desarrollados

por Intel que son la base de los PCs

Arquitectura Intel x86

Sistemas Computacionales

Mario Medina C.

mariomedina@udec.cl

z

Procesadores de la familia x86

z

z

z

z

z

z

Leer instrucción de memoria y colocarla en la

CPU (Fetch)

Decodificar la instrucción (Decode) y actualizar el

contador de programa

Ejecutar la instrucción (Execute), devolviendo los

resultados a los registros o a memoria

tienen conjunto básico común de registros

tienen conjunto básico común de instrucciones

mantienen la arquitectura del conjunto de

instrucciones (Instruction Set Architecture)

Estructura de una CPU 8088

Operación básica de un 8088

Tres pasos básicos:

Intel 8088 (1980) a Intel Quad Core (2009)

EU ejecuta las instrucciones

BIU realiza operaciones de bus bajo control de

la EU

z

Lee instrucciones y operandos, escribe resultados

Dos unidades internas

z

z

Unidad de ejecución (Execution Unit)

Unidad de interfaz de bus (Bus Interface Unit)

Estructura de una CPU 8088

Estructura de una CPU 8088

EU y BIU operan en paralelo

Mientras EU procesa una instrucción, la BIU

está leyendo las instrucciones siguientes

z

Almacenadas en una cola de instrucciones de 4

bytes

Segmentación del trabajo (pipelining)

z

z

z

Minimiza tiempos de inactividad

Aumenta instrucciones procesadas por unidad de

tiempo

Desacopla la EU del acceso a memoria

(C) Mario Medina C.

1

Bus Interface Unit (BIU)

Realiza los accesos a memoria

Implementa el modelo de memoria

Contiene

z

z

z

z

z

Memoria segmentada de 8088

Intel 8088 direcciona memoria física de 1 MiB

z

genera direcciones físicas de 20 bits usando 2

registros de 16 bits

Los registros de segmento CS, DS, SS y ES

Puntero a instrucción IP

Bloque de suma de direcciones ∑

Cola de instrucciones de 4 bytes

Buses de datos internos de 16 bits

Segmentos

Decodifica las instrucciones leídas por la BIU

Ejecuta las instrucciones

Contiene

Segmento: bloque de

memoria de 64 KiB

8088 puede direccionar 4

segmentos en un instante

dado

z

z

z

z

Unidad Aritmético-Lógica (ALU)

z

4 registros de datos

z

4 registros punteros e índices

Operandos de 8 ó 16 bits

Estos segmentos pueden ser

disjuntos, traslapados o iguales

z

Execution Unit (EU)

Accesibles como registros de 8 ó 16 bits

CS: Code segment

DS: Data segment

SS: Stack segment

ES: Extra segment

Usados en operaciones de transferencias de datos

Usados con registros de segmentos

z

Registros 8088

(C) Mario Medina C.

9 flags o bits de estado y de control

Bits de condición 8088

2

Registros 80386 y posteriores

Tipos de datos Intel x86

Palabras (words): 16 bits

Registros de

propósito general

extendidos a 32 bits

2 registros de

segmento extras

Cola de instrucciones

de 6 instrucciones

Más flags de

condición

z

Herencia del 8086

Palabras dobles (doublewords): 32 bits

Palabras cuádruples (quadwords): 64 bits

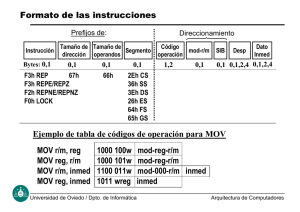

Instrucción mov: movimiento de datos

z

z

z

movb (move byte)

movw (move word)

movl (move doubleword)

Punteros: 32 bits

Registros de 32 bits Intel x86

Registros enteros

z

Almacenan datos y

direcciones

8 registros de 32 bits

z

Registro %eax

Accesibles como 8

registros de 16 bits

z

Registro %ax

%ax

%ah

%al

%ebx

%bx

%bh

%bl

%ecx

%cx

%ch

%cl

%edx

%dx

%dh

%dl

%esi

%si

%edi

%di

%esp

%sp

%ebp

%bp

Ejemplo: addl S, D

z

z

Registros %ah y %al

Formato ensamblador GNU Assembler (GAS)

Partes de una instrucción

Operación: qué hacer (addl)

Operandos fuente (S) y destino (D)

Suma S + D y almacena resultado en D

z

Los 4 primeros son

accesibles como bytes

z

%eax

Instrucciones

Qué son S y D?

Datos en registros

Constantes

Datos en memoria

Modos de Direccionamiento

Modo Inmediato

Usado para definir constantes

z

z

Formato: $Imm

Valor: Imm

Modo Registro

z

z

z

Especifica el registro de 8, 16 ó 32 bits a usar

Formato: Ea

Valor: R[Ea]

Modos de Direccionamiento

Modos de direccionamiento a memoria

z

Modo Absoluto

z

z

z

Especifica una dirección absoluta de memoria

Formato: Imm

Valor: M[Imm]

Modo Indirecto

z

z

z

(C) Mario Medina C.

Indican cómo calcular la dirección efectiva del

operando

Dirección dada por el contenido de un registro

Formato: (Ea)

Valor: M[R[Ea]]

3

Modos de Direccionamiento

Modo Indexado

Modo Base + Desplazamiento

z

z

z

Modos de Direccionamiento

Útil para acceso a vectores

Formato: Imm(Eb)

Valor: M[Imm + R[Eb]]

z

z

Modo Indexado escalado

Modo Indexado

z

z

z

Formato: Imm(Eb, Ei)

Valor: M[Imm + R[Eb] + R[Ei]]

z

Dirección se calcula como registro base + índice

Formato: (Eb, Ei)

Valor: M[R[Eb] + R[Ei]]

z

z

s: factor de escala 1, 2, 4 ó 8

Formato: (, Ei, s)

Valor: M[R[Ei]*s]

Modo Indexado escalado

z

z

Formato: Imm(, Ei, s)

Valor: M[Imm + R[Ei]*s]

Modos de Direccionamiento

Modo Indexado escalado

z

z

Tipo

Formato: (Eb, Ei, s)

Valor: M[R[Eb] + R[Ei]*s]

Modo Indexado escalado

z

z

z

Resumen Modos

Modo más complejo

Formato: Imm(Eb, Ei, s)

Valor: M[Imm + R[Eb] + R[Ei]*s]

Formato

Valor operando

Imm

Inmediato

Registro

Ea

R[Ea]

Registro

Memoria

Imm

M[Imm]

Absoluto

Memoria

(Ea)

M[R[Ea]]

Indirecto

Memoria

Imm(Eb)

M[Imm +R[Eb]]

Base + Desp.

Memoria

(Eb, Ei)

M[R[Eb] +R[Ei]]

Indexado

Memoria

Imm(Eb, Ei)

M[Imm +R[Eb] +R[Ei]]

Indexado

Memoria

(, Ei, s)

M[R[Ei]*s]

Indexado escalado

Memoria

Imm(, Ei, s)

M[Imm +R[Ei]*s]

Indexado escalado

Memoria

(Eb, Ei, s)

M[R[Eb] +R[Ei]*s]

Indexado escalado

Memoria

Imm(Eb, Ei, s)

M[Imm+R[Eb]+R[Ei]*s]

Indexado escalado

Ejemplo

Dados

Evalúe

Dirección

0x100

0x104

0x108

0x10C

Valor

0xFF

0xAB

0x13

0x11

Registro

%eax

%ecx

%edx

Valor

0x100

0x1

0x3

(C) Mario Medina C.

z

z

z

z

z

z

z

z

z

z

%eax

0x104

$0x108

(%eax)

4(%eax)

9(%eax, %edx)

260(%ecx, %edx)

0xFC(,%ecx, 4)

(%eax, %ecx, 4)

2(%eax, %ecx, 2)

Nombre

Inmediato $Imm

Movimiento de datos

Operando fuente S

z

z

z

Inmediato

Registro

Memoria

Operando destino D

z

z

Registro

Memoria

No se pueden mover

datos entre posiciones

de memoria

z

z

Memoria a registro

Registro a memoria

movl S, D

z

z

Mueve doubleword

D ←S

movw S, D

z

z

Mueve word

D ←S

movb S, D

z

z

Mueve byte

D ←S

Instrucciones no

modifican otros bits

4

Movimiento de datos

Instrucciones de manejo

movsbl S, D

de pila

Mueve byte extendido en

signo

pushl S

Copia bit 7 en bits 31-8

z Almacena S en la pila

z D ←SignExtend(S)

z R[%esp] ← R[%esp]-4

movzbl S, D

z M[R[%esp]] ←S

z Mueve byte extendido a

popl

D

cero

z Retira D de la pila

Bits 31-8 son 0

z D← M[R[%esp]]

z D ←ZeroExtend(S)

z R[%esp] ← R[%esp]+4

z

Pila del procesador

Área de memoria utilizada para almacenar y

recuperar rápidamente datos

Vital para manejo de funciones

Acceso via instrucciones especiales popl y

pushl

Indexada por registro dedicado %esp

Crece hacia direcciones bajas de memoria

Pila y registro “Stack Pointer”

Ejemplo: exchange()

Código C

Inicialmente

Direcciones

de Memoria

%eax

0x123

%edx

0

%esp

0x108

pushl %eax

%eax

%edx

%esp

popl %edx

0x123

0

0x104

%eax

%edx

%esp

0x123

0x123

0x108

Comienzo de pila

Comienzo de pila

Comienzo de pila

•

•

•

•

•

•

•

•

•

0x108

0x108

Tope de pila

0x104

0x108

0x123

Tope de pila

0x123

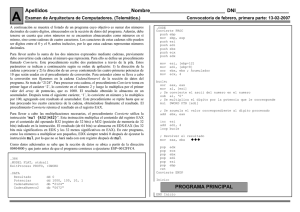

int exchange(int *xp, int y){

int x = *xp;

*xp = y;

return x;

}

Código intercambia dato apuntado por xp y dato

contenido por y

Código utiliza variable intermedia x

Tope de pila

Ejemplo: exchange()

Código Assembly

Parámetros de funciones se

movl 8(%ebp), %eax

pasan a través de memoria,

movl 12(%ebp), %edx indexados por el puntero

movl (%eax), %ecx

base (base pointer) %ebp

movl %edx, (%eax)

movl %ecx, %eax

Convención: parámetros xp e y de la función están a 8

y 12 bytes de (%ebp), respectivamente

Convención: funciones retornan resultados en %eax

(C) Mario Medina C.

Operaciones aritmético-lógicas

Instrucción

Efecto

Descripción

leal S, D

D ← &S

Carga dirección

incl D

D←D+1

Incrementa D

decl D

D←D-1

Decrementa D

negl D

D ← -D

Niega D

notl D

D ← ~D

Complementa D

addl S, D

D←D+S

Suma S y D

subl S, D

D←D-S

Resta S a D

imull S, D

D←D*S

Multiplica S y D

xorl S, D

D←D^S

XOR S y D

orl S, D

D←D|S

OR S y D

andl S, D

D←D&S

AND S y D

5

Instrucción leal S, D

Variante de movl

z

z

z

Calcula la dirección en memoria de S (&S)

Almacena la dirección calculada en D

Usada para generar punteros y cálculos aritméticos

z

1.

3.

movl 10(%ecx), %eax

%eax ← M[%ecx + 10]

4.

leal 10(%ecx), %eax

5.

%eax ← %ecx + 10

Ejemplo: %edx contiene variable x

z

Suponga que %eax contiene x, y %ecx

contiene y. Qué calculan:

2.

Ejemplo de puntero

z

Ejemplos de leal

6.

leal

leal

leal

leal

leal

leal

6(%eax), %edx

(%eax, %ecx), %edx

(%eax, %ecx, 4), %edx

7(%eax, %eax, 8), %edx

0xa(, %ecx, 4), %edx

9(%eax, %ecx, 2), %edx

Qué hace leal 7(%edx, %edx, 4), %eax?

%eax almacena 5x+7

Operaciones aritméticas

Dados

Evalúe

Dirección

0x100

0x104

0x108

0x10C

Valor

0xFF

0xAB

0x13

0x11

1.

Registro

%eax

%ecx

%edx

Valor

0x100

0x1

0x3

6.

2.

3.

4.

5.

addl %ecx, (%eax)

subl %edx, 4(%eax)

imull $16, (%eax,

%edx, 4)

incl 8(%eax)

decl %ecx

subl %edx, %eax

Operaciones de desplazamiento

Instrucción

Efecto

Descripción

sall k, D

D ← D << k

Desp. izquierda

shll k, D

D ← D << k

Desp. izquierda

sarl k, D

D ← D >> k

Desp. derecha aritmético

shrl k, D

D ← D >> k

Desp. derecha lógico

Desplazamientos

Desplazamiento va de 0 a 31

z

Generalmente operando inmediato o %cl

Operaciones sall y shll son iguales

Operaciones sarl y shrl son diferentes

z

sarl hace desplazamiento aritmético a la derecha

z

shrl hace desplazamiento lógico a la derecha

Ejemplo: código C

int arith(int x, int y, int z){

int t1 = x + y;

int t2 = z*48;

int t3 = t1&0xFFFF;

int t4 = t2*t3;

Extensión de signo mantiene el signo del resultado

Rellena con 0s

(C) Mario Medina C.

return t4;

}

6

Ejemplo: código ensamblador

Suponga que x, y y z están a 8, 12 y 16 bytes de

(%ebp), respectivamente

movl 12(%ebp), %eax

//

movl 16(%ebp), %edx

//

addl 8(%ebp), %eax

//

leal (%edx, %edx, 2), %edx

sall $4, %edx

//

andl $65535, %eax

//

imull %eax, %edx

//

movl %edx, %eax

//

Lee y

Lee z

Calcula t1

Calcula

Calcula

Calcula

Retorna

Multiplicación de enteros

imull S, D: Multiplica 2 operandos

z

z

Cada operando tiene 32 bits

Resultado truncado a 32 bits

imull S: Multiplicación de 1 operando

z

Operando S tiene 32 bits

z

Resultado tiene 64 bits

Se multiplica con contenido de %eax

t2

t3

t4

t4

32 bits más significativos en %edx

32 bits menos significativos en %eax

mull S: multiplica enteros sin signo

División

idivl realiza división de 64 bits con signo

z

z

z

z

Dividendo: concatenación de %edx:%eax

Divisor: operando de la instrucción

Cuociente de la división queda en %eax

Resto de la división queda en %edx

divl realiza división de 64 bits sin signo

cltd convierte contenido de %eax a 64 bits

con signo

z

Ejemplos

Suponga x en 8(%ebp) e Suponga x en 8(%ebp)

y en 12(%ebp)

e y en 12(%ebp)

Multiplica x e y, retorna Divide x por y, retorna

resultados en la pila

resultados en la pila

movl 8(%ebp), %eax

imull 12(%ebp)

pushl %edx

pushl %eax

movl 8(%ebp), %eax

cltd

idivl 12(%ebp)

pushl %eax

pushl %edx

Extiende signo de %eax en %edx

Operaciones aritméticas

Bits de condición

CPUs Intel mantienen flags o bits de condición

Instrucción

Efecto

Descripción

imull S

R[%edx]:R[%eax]←S×R[%eax]

Multiplica con signo

mull S

R[%edx]:R[%eax]←S×R[%eax]

Multiplica sin signo

z

cltd

R[%edx]:R[%eax]←

SignExtend(R[%eax])

Convierte a quad

word

z

idivl S

R[%edx]←R[%edx]:R[%eax] mod S

División con signo

z

z

z

R[%eax]←R[%edx]:R[%eax]÷S;

divl S

R[%edx]←R[%edx]:R[%eax] mod S

División sin signo

Describen resultados de últimas operaciones de ALU

Carry Flag (CF): Última operación generó un rebalse

Zero Flag (ZF): Última operación generó un cero

Sign Flag (SF): Última operación generó un número

negativo

Overflow Flag (OF): ÚItima operación generó un

rebalse de complemento a 2

R[%eax]←R[%edx]:R[%eax]÷S;

(C) Mario Medina C.

7

Ejemplo: resta

Calcular 0xE4534980 – 0x94533443

z

Equivalente a 0xE4534980+[0x94533443]

Restar B es sumar el complemento a 2 de B

z

z

z

Equivalente a 0xE4534980+0x6BACCBBD

Resultado es 0x15000153D

Cómo quedan los bits de condición?

ZF = 0

CF = 1

SF = 0

OF = 1

Ejemplo: t = a + b

Implementado con instrucción addl

z

z

z

z

CF: (unsigned t) < (unsigned a)

ZF: (t == 0)

SF: (t < 0)

OF: (a < 0 == b < 0) && (t < 0 != a < 0)

Instrucción leal no modifica bits de condición

Operaciones lógicas hacen CF y OF igual a 0

Desplazamientos hacen OF 0 y modifican CF

Instr. Comparación

•Modifican los códigos de condición

•No modifican operandos

Acceso a códigos de condición

Instrucción Sinónimo

Efecto

Condición

sete D

setz

D←ZF

cero

setne D

setnz

D←~ZF

No cero

sets D

D←SF

Negativo

D←~SF

No negativo

Instrucción

Basado en

Descripción

setns D

cmpb S2, S1

S1 - S 2

Compara bytes

setg D

setnle

D←~(SF^OF)&~ZF

Mayor (signed)

testb S2, S1

S1 & S 2

Test bytes

setge D

setnl

D←~(SF^OF)

Mayor o igual

cmpw S2, S1

S1 - S 2

Compara palabras

setl D

setnge

D←SF^OF

Menor

setle D

setng

D←(SF^OF)|ZF

Menor o igual

testw S2, S1

S1 & S 2

Test palabras

seta D

setnbe

D←~CF &~ZF

Superior (unsigned)

cmpl S2, S1

S1 - S 2

Compara palabras dobles

setae D

setnb

D←~CF

Superior o igual

testl S2, S1

S1 & S 2

Test palabras dobles

setb D

setnae

D←CF

Inferior

setbe D

setna

D←CF|ZF

Inferior o igual

Instrucciones setX

Resultado de instrucciones setX es 1 byte de

valor 0 ó 1

z

Destino de instrucción es un registro de 8 bits ó un

byte en memoria

Usar movzbl para convertir resultado a 32 bits

z

Ejemplo: si a está en %eax y b en %edx

cmpl %eax, %edx

setl %al

movzbl %al, %eax

(C) Mario Medina C.

a < b?

Bits 0-7 %eax son 0 ó 1

Extiende valor a 32 bits

Ahora %eax es 0 ó 1

Instrucciones de salto

•Cambio en secuencia de ejecución de instrucciones

•Saltos condicionales e incondicionales

Instrucción

Sinónimo Condición Descripción

jmp Rótulo

1

Salto directo

jmp *Operando

1

Salto indirecto

je Rótulo

jz

ZF

Cero

jne Rótulo

jnz

~ZF

No cero

js Rótulo

SF

Negativo

jns Rótulo

~SF

No negativo

8

Instrucciones de salto

Instrucción

Sinónimo

Condición

Descripción

jg Rótulo

jnle

~(SF^OF)&~ZF

Mayor (signed)

jge Rótulo

jnl

~(SF^OF)

Mayor o igual

jl Rótulo

jnge

SF^OF

Menor

jle Rótulo

jng

(SF^OF)|ZF

Menor o igual

ja Rótulo

jnbe

~CF &~ZF

Superior (unsigned)

jae Rótulo

jnb

~CF

Superior o igual

jb Rótulo

jnae

CF

Inferior

jbe Rótulo

jna

CF|ZF

Inferior o igual

•Rótulo es una referencia en el código fuente

jmp L1

.L1: pop %edx

(C) Mario Medina C.

9