Cap™tulo 00 (In) (Quark) bueno - Circuitos Eléctricos y Electrónicos

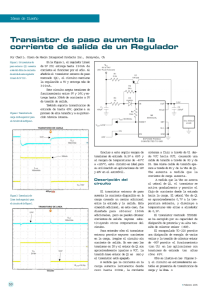

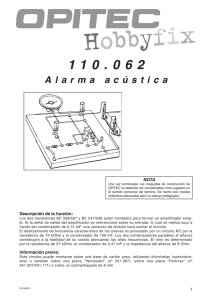

Anuncio