Presentación de PowerPoint - Universidad Tecnológica Nacional

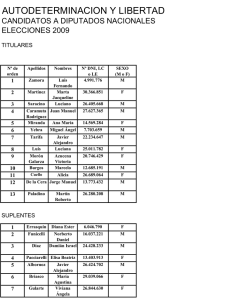

Anuncio

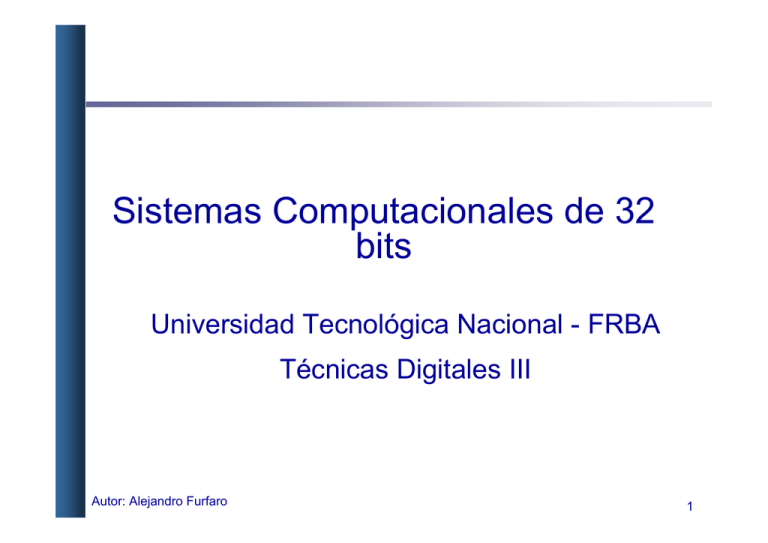

Sistemas Computacionales de 32 bits Universidad Tecnológica Nacional - FRBA Técnicas Digitales III Autor: Alejandro Furfaro 1 Introducción 1 Sistemas Computacional: 2 2 2 1 Conjunto de dispositivos lógicos de Hardware y Software que se utilizan para procesar datos, señales, o cualquier información digital. Dedicados: Cumplen una única función o un grupo determinado de funciones específicas De propósito general: Sirven para ejecutar todo tipo de aplicaciones. El único límite es el número máximo de aplicaciones que pueden albergar en un mismo momento, y la capacidad de procesamiento para poder ejecutar aplicaciones de determinada envergadura. Componentes 2 Hardware Procesador i Periféricos i Memoria i 2 Software Programas de control aplicado para computadoras dedicadas i Sistemas Operativos para computadoras de propósito general o de tipo embedded. Su complejidad varía entre ambos casos Autor: Alejandro Furfaro i 2 Ejemplos mas comunes 1 Sistemas de propósito General 2 Antecedentes i Durante los 70’s aparecen Commodore 64 / 128, Amiga, Talent MSX, etc. 4 Procesadores de 8 bits. Z80 en el mejor de los casos, 4 Cantidad de memoria reducida. 4 Dispositivos de almacenamiento mínimos. 2 Principios i IBM de los 80’s introduce su modelo de Personal Computer PC. 4 Procesador de 16 bits: 8088, 4 Dispositivos de almacenamiento, y cantidad de memoria levemente mejores a sus antecesores 4 Introduce junto con Intel el concepto de diseños escalables por compatibilidad ascendente i Al mismo Autor: Alejandro Furfaro tiempo Apple lanza la Machintosh (“Mac”) 3 Ejemplos mas comunes 1 Computadoras 2 Sistemas dedicadas. de tipo Embedded. i Diseños single board con procesadores compatibles con los de la IBM PC a medida que esta gana popularidad. i Al principio se desarrollaron versiones de DOS para ROM i Evolución tecnológica => PC-104. Standard Industrial i SBC => Single Board Computer 4 Aprovechan la base instalada de PC’s para integrar módulos muy compactos para aplicaciones dedicadas desarrollables en una PC. 4 Tienen los mismos recursos en las mismas direcciones. 4 Versiones de Linux, QNX, y otros con imágenes mínimas para el control de las aplicaciones requeridas para cada solución. => Sistemas multitarea dedicados i SOM =>System On Module 4 Son CPU’s listas para usar, con firmware embebido. Pueden hostear una imagen de un Sistema Operativo. 4 Son una versión mucho mas compacta de un SBC Autor: Alejandro Furfaro 4 Ejemplos de SOM: IA-32 1 144 mm 95 mm 1 1 1 1 1 Autor: Alejandro Furfaro Procesador Embedded Pentium M o Dothan 1.6 GHz/1.1 GHz con 64KB de memoria cache L1. Memoria DRAM 2 x 200 pin SODIMM sockets, ECC Double Data Rate (DDR)128 MB to 1GB. 1MB de memoria cache L2. 1000Base-T Ethernet Intel 855GME GMCH/ ICH4 Chipset 400 MHz FSB Interfaces PCI & AGP 6 ports host USB 2.0 5 Ejemplos SOM: XScale 1 102 mm 1 68 mm 1 Autor: Alejandro Furfaro 1 1 1 Procesador Xscale PXA 255 de 400MHz. Memoria DRAM de 32 / 64 /128 MBytes On board 1MB Flash ROM. Expandible externamente hasta 64MB. Ethernet 10 / 100 BaseT 2 ports host USB 1.1. 1 port USB device side Interfaz LCD 1024x768 6 Ejemplos SBC: PC-104 96 mm 1 115 mm 1 1 1 1 1 Autor: Alejandro Furfaro Procesador Embedded Pentium M 1.6 GHz/1.1 GHz con 64KB de memoria cache L1. Memoria DRAM 2 x 200 pin SODIMM sockets, ECC Double Data Rate (DDR)128 MB to 1 GB. 1MB cache L2. 100Base-T Ethernet Intel 855GME GMCH/ ICH4 Chipset 400 MHz FSB. Interfaces PCI & AGP 6 ports host USB 2.0 7 Componentes de una PC XT Autor: Alejandro Furfaro 8 0009FFFF 000A0000 000BFFFF 000C0000 000FFFFF 00100000 Vector de Int Modo Real BIOS Data Area Area de datos y programas 640 Kbytes 00000000 1 Kbyte Mapa de Memoria FFFFFFFF Autor: Alejandro Furfaro 9 Mapa de Memoria 0009FFFF 000A0000 000BFFFF 000C0000 Buffers de Video Modos Texto y Gráfico 128 Kbytes 00000000 000FFFFF 00100000 FFFFFFFF Autor: Alejandro Furfaro 10 Mapa de Memoria 0009FFFF 000A0000 Zona de Extensión de BIOS 000BFFFF 000C0000 000FFFFF 00100000 000EFFFF 000F0000 000FFFFF POST BIOS 192 Kbytes 000C0000 64 Kbytes 00000000 FFFFFFFF Autor: Alejandro Furfaro 11 Mapa de E/S en una PC Autor: Alejandro Furfaro 12 Hardware de Soporte de E/S 1 8253 / 8254: 2 2 2 2 Timer 0: Dirección 40h. Base de tiempos del sistema. A la entrada CLK0 se conecta un cristal de 1,193,180 MHz. Se programa para generar por OUT0 un pulso cada 55 mseg. Este pin se conecta a la línea IRQ0 del PIC 8259: así se genera una interrupción a dicho intervalo, o como se refiere en la jerga, “genera 18,2 (¿?) interrupciones por segundo”. Timer 1: Dirección 41h. Se programa del mismo modo que Timer 0 pero se lo utiliza para activar el sistema de refresco de memoria DRAM. Para ello, OUT1 va conectado a la entrada DREQ0 del 8237. A partir del modelo AT 286 se utilizará un hardware dedicado al refresco de memoria. Timer 2: Dirección 42h. Se programa para generar a su salida una señal cuadrada de 50% de duty cycle y OUT2 se conecta al parlante del sistema. Registro de comando y status. Dirección 43h. Autor: Alejandro Furfaro 13 Hardware de Soporte de E/S 18255: Fue inmediatamente reemplazado en el modelo siguiente (AT 286). Sin embargo los ports A y B, siguen presentes 2 2 2 Port A: Dirección 60h. La lógica de control de teclado al recibir los códigos de las teclas los almacena en este port. Port B: Dirección 61h. Sus líneas trabajan como salidas de control individuales. 2 Envío de la salida del Timer0 al parlante de la PC 2 Envío de un pulso a la línea IRQ1 del PIC 8259 cada vez que se recibe un código de tecla desde el teclado. Port C: Dirección 62h. Cuatro de estas líneas se utilizan como información de configuración del sistema. El sistema de configuración en los modelos originales PC y PC-XT era sumamente rudimentario (trabajaba con dip switches). Autor: Alejandro Furfaro 14 Interrupciones en los procesadores x86 Notas: 1 La instrucción UD2 fue introducida con el procesador Pentium Pro. 1 Los procesadores IA-32 posteriores al Intel386 no generan esta excepción. 1 Esta excepción fue introducida en el procesador Intel486. 1 Esta excepción fue introducida en el procesador Pentium y mejorada en la familia de procesadores P6. 1 Esta excepción fue introducida en el procesador Pentium III. Autor: Alejandro Furfaro 15 Interrupciones en la PC Autor: Alejandro Furfaro 16 Controlador de Interrupciones de Hardware: el PIC 8259 INTA D0 - D7 DATA BUS BUFFER INT LOGICA DE CONTROL BUS DE DATOS INTERNO RD IRQ0 WR READ WRITE LOGIC A0 IRQ1 IN SERVICE REGISTER (ISR) PRIORITY RESOLVER CS INTERRUPT IRQ2 REQUEST REGISTER (IRR) IRQ3 IRQ4 IRQ5 IRQ6 IRQ7 CAS0 CAS1 CAS2 CASCADE BUFFER COMPARATOR INTERRUPT MASK REGISTER (IMR) SP/EN Autor: Alejandro Furfaro 17 Configuración del PIC 8259 en la PC Timer Timer Tick Tick Data Bus Autor: Alejandro Furfaro CAS2 CAS1 CAS0 SP/EN 0 Disponibles en los buses de expansión IRQ3 IRQ4 IRQ5 IRQ6 IRQ7 IRQ8 IRQ9 IRQ10 IRQ0 IRQ1 INT IRQ2 IRQ3 INTA IRQ4 IRQ5 8259 Slave IRQ6 A0h-A1h IRQ7 SP/EN CAS2 Procesador 80x86 8042 Keyb Cont CAS1 INTA OUT CAS0 INTR 8259 Master IRQ0 20h-21h IRQ1 INT IRQ2 IRQ3 INTA IRQ4 IRQ5 IRQ6 IRQ7 8254 40h-43h Este 2do. 8259 fue agregado a partir de la PC-AT286 IRQ11 IRQ12 IRQ13 IRQ14 IRQ15 Vcc Nombre de las líneas del Sub-sistema de Interrupciones de la PC 18 Asignación y Tipo de las IRQ’s Autor: Alejandro Furfaro 19 Interrupción No Enmascarable (NMI) 80x86 Error de paridad en Memoria Error de paridad en el Bus Error del Coprocesador 8087 NMI 7 6 5 4 3 2 1 0 Port de E/S 0A0h 80x86 Error de paridad en Memoria Error de paridad en el Bus NMI 7 6 5 4 3 2 1 0 Port de E/S 070h Autor: Alejandro Furfaro 20 Programación del PIC 8259 1 El 8259, presenta al procesador una interfaz de programación a través de dos direcciones de E/S. 2 2 2 1 La primer PC tenía un solo PIC en las direcciones de port 20h y 21h. La PC AT 286, incluyó un segundo PIC, ya que la PC original ya había agotado la asignación de IRQ’s, y seguían apareciendo nuevos dispositivos: Placas de red, placas de sonido, etc. Este PIC es accesible en las direcciones de port A0h y A1h. Palabras de Comando de Inicialización: 2 2 2 Son una secuencia de entre dos y cuatro bytes que envía el procesador al 8259A antes de comenzar la operación normal, a fin de configurarlo. A los efectos del PIC 8259, la secuencia de Inicialización es una operación atómica, es decir, que no puede dividirse El 8259 detecta la secuencia de inicialización cuando recibe en la dirección de port par (A0 = 0), una palabra con el bit D4=1. Palabras de Comando de Operación: Una vez inicializado el 8259A, estas palabras le definen diversas operaciones a realizar. Luego de la inicialización, se pueden enviar en cualquier momento. Autor: Alejandro Furfaro 21 Programación del PIC 8259 ;;Inicialización InicializaciónPIC PIC#1 #1 mov mov al,11h al,11h ;ICW1: ;ICW1:IRQs IRQsactivas activaspor porflanco, flanco,Modo Modocascada, cascada,ICW4 ICW4Si. Si. out 20h,al out 20h,al mov ;ICW2: mov al,8 al,8 ;ICW2:INT INTbase basepara parael elPIC PICN#1 N#1Tipo Tipo8. 8. out out 21h,al 21h,al mov mov al,04h al,04h ;ICW3: ;ICW3:PIC PICN#1 N#1Master, Master,tiene tieneun unSlave Slaveconectado conectadoaaIRQ2 IRQ2(0000 (00000100b) 0100b) out out 21h,al 21h,al mov al,01h mov al,01h ;ICW4: ;ICW4:Modo ModoNo NoBuffered, Buffered,Fin Finde deInterrupción InterrupciónNormal, Normal,procesador procesador8086 8086 out 21h,al out 21h,al ;;Antes Antesde deinicializar inicializarel elPIC PICN#2, N#2,deshabilitamos deshabilitamoslas lasInterrupciones Interrupcionesdel delPIC PICN#1 N#1 mov mov al,0FFh al,0FFh:OCW1: :OCW1:Set SetooClear Clearel elIMR IMR out out 21h,al 21h,al ;;Inicialización InicializaciónPIC PICNN#2 #2 mov al,11h ;ICW1: mov al,11h ;ICW1:IRQs IRQsactivas activaspor porflanco, flanco,Modo Modocascada, cascada,ICW4 ICW4Si. Si. out 0A0h,al out 0A0h,al mov mov al,070h al,070h;ICW2: ;ICW2:INT INTbase basepara parael elPIC PICN#1 N#1Tipo Tipo070h. 070h. out out 0A1h,al 0A1h,al mov mov al,02h al,02h ;ICW3: ;ICW3:PIC PICN#2 N#2Slave, Slave,IRQ2 IRQ2es esla lalínea líneaque queenvía envíaal alMaster Master(010b) (010b) out 0A1h,al out 0A1h,al mov mov al,01h al,01h ;ICW4: ;ICW4:Modo ModoNo NoBuffered, Buffered,Fin Finde deInterrupción InterrupciónNormal, Normal,procesador procesador8086 8086 out out 0A1h,al 0A1h,al Autor: Alejandro Furfaro 22 Power On Self Test 1 1 1 1 1 Antes de iniciar su operación el sistema verificará el correcto funcionamiento de la CPU Chequea si el contenido de la ROM es el correcto (realiza un checksum del contenido de la ROM completa que en fábrica se ajusta de modo que el resultado del check sea cero). Detecta el tipo de adaptador de video instalado. Lo inicializa en modo texto 80x25. Escribe en la BIOS DATA AREA los principales datos de interés para el sistema que proporciona este controlador. Comprueba la correcta interacción con el 8042 y setea el modo de trabajo con los diferentes ports de E/S que proporciona este chip. Si el Timer 1 funciona correctamente se lo programa para generar un pulso al final de la cuenta, cuenta cíclica, y duración de la misma 15 mseg. Autor: Alejandro Furfaro 23 Power On Self Test Comprueba el correcto funcionamiento para el canal de DMA 0. 7. Si los test descriptos indican que el Timer 1 y el canal 0 de DMA funcionan correctamente, entonces se dispara el refresco de memoria. 8. Comprueba el 8259 y lo inicializa con los valores default de los vectores de Interrupción. A los que usa, los apunta a las rutinas de la ROM correspondientes. 9. Cuenta la memoria RAM y comprueba su funcionamiento 10. Una vez finalizada la cuenta de memoria, chequea los restantes timers y canales de DMA. Si funcionan correctamente los inicializa de acuerdo a la forma en la que van a trabajar cada uno de ellos. 11. Funcionando correctamente el teclado y el timer tick, habilita sus interrupciones en el 8259 6. Autor: Alejandro Furfaro 24 Power On Self Test 12. 13. 14. 15. 16. Testea el funcionamiento de las unidades de disco flexible y rígido. Una vez comprobado las inicializa, y escribe los resultados y principales parámetros en la BIOS DATA AREA. Chequea si existen ports serie. Inicializa a los que encuentra y guarda resultados en BIOS DATA AREA. Chequea si existen ports paralelo. Inicializa a los que encuentra y guarda resultados en BIOS DATA AREA. Establece si existen extensiones BIOS. Esto es: La ROM BIOS de las PC provee un camino para integrar adaptadores de E/S con su propia ROM on-board. Llama a la rutina Bootstrap loader para la carga del sistema operativo Autor: Alejandro Furfaro 25 Detección de extensiones BIOS 1 1 1 1 1 1 1 1 El POST busca extensiones de BIOS. El rango de direcciones de memoria en las que se pueden mapear estas ROMs va desde la C0000h hasta la EFFFFh. Se busca dentro de este rango cada 2K una firma fija e igual a 55AAh. Si la encuentra asume que en esa página de 2k comienza una extensión de BIOS. Si el POST detecta alguna ROM adicional, le transfiere temporariamente el control. La extensión de BIOS: Inicializará el hardware para el que fue diseñada Realizará, del mismo modo que el POST de la ROM del sistema) un checksum, cuyo resultado debe ser 0 para que la ROM se considere de contenido válido. Interceptará las interrupciones que necesite, enganchándose a sí misma en el sistema. Devolverá al POST el control del sistema (RET) dejando al hardware asociado a la extensión BIOS, listo para su uso. Autor: Alejandro Furfaro 26 Extensiones BIOS: Mapa de Memoria 00000000 0009FFFF 000A0000 000BFFFF 000C0000 000FFFFF 00100000 000C0000 2Kbytes 2Kbytes Extensión de BIOS 000EFFFF 000F0000 POST 000FFFFF BIOS Encabezado Código y datos de la extensión Formato del encabezado de la de extensión BIOS: FFFFFFFF Autor: Alejandro Furfaro 27 Arranque del sistema operativo 1 La rutina Boostrap Loader del BIOS solo se limita a 2 Leer el primer sector físico del disco. 2 Cargar los 512 bytes en memoria RAM (0000h:7C00h) 2 Saltar al primer byte (debe haber allí una instrucción válida) 1 La unidad de disco que lee es la que tiene configurada el equipo en la secuencia de arranque. 1 En ese sector debe residir un programa que sepa cargar al Sistema Operativo. 2 Debe leer del disco los archivos necesarios para bajar a la memoria. Para ello deben conocer la forma en que está organizada la información en el disco 2 Debe descargarlos en memoria y en algún momento transferirles la ejecución. Autor: Alejandro Furfaro 28 Acceso Directo a Memoria (DMA) CPU DREQ0 HRQ HLDA HLDA Address Bus HOLD DACK0 DREQ1 DACK1 Controlador de DMA (8237A)DREQ DRAM 2 DACK2 Address Bus DREQ3 DACK3 Device Device 1 1 Device Device 2 2 Device Device 3 3 Device Device 4 4 Data Bus Autor: Alejandro Furfaro 29 Subsistema de DMA en la PC y PCXT 5Vcc RAS OUT 1 CL A0 A1 A2 A3 A4 A5 A6 A7 DREQ0 Q 74LS74 DREQ1 DREQ2 DREQ3 DREQ 1 DREQ2 DREQ3 HRQ HLD A RDY TO DMA CLK RES Y4 RAS 3 NC DACK0 DACK1 DACK2 DACK3 EOP AEN XIOR XIO W XMEM R XMEMW IOR IOW MEMR MEMW D0 Q0 D1 Q1 D2 Q2 Q3 D3 WA WB74LS670 RB RA ADSTB A16 A17 A18 A19 Bus 74LS243 DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 de Bus de Control 8288 RD W GND DMA AEN WRT DMA PG RG 74LS32 Fig. 6. Circuito de Control de DMA en una IBM PC XT Autor: Alejandro Furfaro 2 74S08 “ Buffereado” IO IOW R MEMR MEMW AEN RAS 74S08 Datos Señales de Status del 8088 74LS138 S2 8237A 1 2G EOP G2A G2B S0 S1 CS Y0 A B C 1G DACK0 DACK1 DACK2 DACK3 de XA9 HLDA RDY CL K RES Bus AEN XA5 XA6 XA7 XA8 HRQ 74LS24 4 RAS RAS A0 A1 A2 A3 A4 A5 A6 A7 Direcciones 8253 0 Al Slot ISA del Sistema CL Bus de Direcciones “ Buffereado” D S XD0 XD1 XD2 XD3 XD4 XD5 XD6 XD7 OE 74LS37 3 A8 A9 A10 A11 A12 A13 A14 A15 LE 30 Subsistema de DMA: Direcciones de E/S DMA Page Registers: El 8237 solo direcciona 64 Kbytes (bus de address de 16 bits) En la XT, se agregan estos Registros para llegar al Mbyte de espacio de direccionamiento. Por lo tanto son registros de 4 bits. En las AT286 se extendieron a 8 bits, ya que el 80286 agrega al bus de direcciones las líneas A20 a A23 Autor: Alejandro Furfaro 31 Subsistema de DMA a partir de la PC AT286 Autor: Alejandro Furfaro 32 Subsistema de DMA a partir de la PC AT286 Autor: Alejandro Furfaro 33 Subsistema de DMA PC AT286: Limitaciones Este subsistema introdujo mejoras en la performance de una PC XT con un disco rígido de 10 Mbytes. 1 En las máquinas modernas con discos de 100 Gbytes, la combinación 8237 mas Bus ISA, se transformaría en un cuello de botella. 1 Los chipsets que acompañan a los procesadores Pentium, aún los mas modernos siguen incluyendo la lógica equivalente a este subsistema (8237 like). La única razón: COMPATIBILIDAD. A este montaje se lo denomina DMA de terceras partes. 1 las PCs modernas utilizan DMA de primera parte. Se refiere a controladores de dispositivos de E/S (como disco por ejemplo) capaces de requerir por si solos el DMA y manejarlo. Este concepto se conoce como Bus Mastering y en él se basa la tecnología Ultra DMA (UDMA) de los controladores IDE para discos rígidos. Autor: Alejandro Furfaro 34 1 Alternativas al Subsistema de DMA legacy E/S Programada (PIO) Esquema de acceso a la E/S mediante instrucciones de E/S del procesador (IN, OUT, INS, y OUTS) y algún hardware adicional. Arranca para Bus ISA. De acuerdo a la implementación se consiguieron diferentes velocidades de acceso. Estas se conocen como Modos de E/S Programada o PIO Modes. La solución resultó mas que aceptable para los primeros discos rígidos de tecnología IDE/ATA, de modo que estos PIO modes fueron incluidos en las respectivas especificaciones de los estándares ATA-1 y ATA-2. Cantidad de nano segundos para que se lleve a cabo la transferencia Autor: Alejandro Furfaro 1/Tiempo de Ciclo 35 Subsistemas de DMA modernos 1 Bus Mastering 2 2 2 1 Para los discos rígidos el método PIO, demanda demasiada CPU. El Bus PCI aumenta las velocidades de transferencia, y permite acceder al bus del sistema de manera transparente al procesador. Por este motivo se desarrollo el método de Bus Mastering para reemplazar al PIO en transferencias masivas de datos de modo de liberar al procesador Para habilitar Bus Mastering en un sistema, se requiere que el hardware del chipset, y el BIOS, lo soporten, que el dispositivo periférico soporte Bus Mastering, y trabajar con un sistema operativo de 32 bits: Windows 2000, Windows XP, Linux, etc. En algunas ocasiones se requiere la instalación de un driver. Ultra DMA 2 2 Esta tecnología corresponde al concepto de DMA de primera parte, y se implementó en los discos rígidos en reemplazo de la PIO. Nos referiremos en mas detalle al abordar el tema de Discos Rígidos, ya que no es un control de DMA abierto a cualquier periférico que lo requiera sino que se encuentra embebido en el hardware del controlador de disco y es exclusivo para éste. Autor: Alejandro Furfaro 36 Teclado Un Microcontrolador se encarga del barrido de la matriz de teclas con la implementación del control de antirrebote. Una vez detectada la pulsación o liberación de una tecla se transmite por línea serie a la PC el código de la misma. ¿Qué código? Cada tecla se identifica con un código de acuerdo con su posición dentro del layout del teclado. En el caso de la tecla ESC su código es 1. Este valor se denomina SCAN CODE (o código de rastreo en algunas traducciones) Autor: Alejandro Furfaro 37 Teclado MAKE BREAK Autor: Alejandro Furfaro El SCAN CODE se transmite cada vez que se pulsa una tecla acción conocida como MAKE, razón por la cual se denomina MAKE CODE Cuando se libera la tecla pulsada (acción conocida como BREAK), se vuelve a transmitir el SCAN CODE de la tecla a la PC para generar una segunda interrupción por IRQ1. La PC detecta tanto la pulsación como la liberación de cada tecla. De otro modo no se podría por ejemplo actuar ante CTRL+ALT+DEL Para diferenciar la acción de BREAK de un MAKE el código que se transmite es el mismo SCAN CODE pero con el MSB en 1. Este código se denomina BREAK CODE 38 Controlador de Teclado A partir de la AT 286 del lado PC un microcontrolador 8042 es quien se encarga de recibir el Make o el Break code. Es un miembro especial de la familia MCS- 51, denominado Universal Peripheral Interface: Dispone de una interfaz para que sus propios ports integrados sean accesibles desde el exterior por otro microprocesador. En este caso ese microprocesador es el de la PC. Recibe los datos desde el teclado por una interfaz serie, chequea paridad, traduce los scan codes y los deja disponibles en un port interno que visto desde el exterior se accede en la dirección 60h del mapa de E/S de la PC. Registros accesibles desde la PC 1 Registro de status (Read) o comandos (Write). Se accede en la dirección 64h de E/S de la PC 1 Output Buffer (Read only), para leer el código de la tecla pulsada o liberada. Se accede en la dirección 60h de E/S 1 Input Buffer (Write only). En la dirección 64h se escribe un comando al controlador (Command Register, visto anteriormente). En la dirección 60h se escribe un dato, que será enviado al teclado. Autor: Alejandro Furfaro 39 Controlador de Teclado Autor: Alejandro Furfaro 40 BIOS Data Area: Bytes de Estado de teclas modificadoras Address 0040:0017 Address 0040:0018 Autor: Alejandro Furfaro 41 Rutina de Atención de Int. de Teclado Detección Detección de de SCAN SCAN SI Actualiza Actualiza Bytes Bytes de de Estados Estados en en BIOS BIOS Data Data Area Area NO Analiza Analiza estado estado de de Teclas Teclas Modificadoras Modificadoras Es Es una una Tecla Tecla Modificadora? Modificadora? NO Es Es un un Break Break Code? Code? SI Es Es un un Break Break Code? Code? SI SI Es Es la la Tecla Tecla INS? INS? Traduce Traduce el el Scan Scan Code Code aa ASCII ASCII desde desde una una Tabla Tabla Es Es un un ASCII ASCII Extendido? Extendido? NO NO SI Escribe Escribe ASCII ASCII Extendido Extendido en en el el buffer buffer de de teclado teclado NO Escribe Escribe Scan Scan Code Code yy ASCII ASCII en en el el Buffer Buffer de de Teclado Teclado Autor: Alejandro Furfaro FIN FIN 42 BIOS Data Area: Buffer circular de teclado Autor: Alejandro Furfaro 43 Reloj en Tiempo Real A partir de la AT 286, se incluyó en el diseño un chip de Motorola con un Real Time Clock y una RAM CMOS de 64 bytes: El MC146818. Los registros internos de la RAM CMOS, se detallan a continuación: Registros del MC 146818 00 01 Segundos Segundos de alarma 10 11 Byte de tipo de drive de disquete (A y B) Reservado 02 03 04 05 Minutos Minutos de alarma Horas Horas de alarma 12 13 14 15 Byte de tipo de hard disk (C y D) Reservado Byte de equipo Byte bajo de memoria base 06 07 08 09 Día de la semana Fecha del Mes Mes Año 16 17 18 19-2D Byte alto de memoria base Byte bajo de expansión de memoria Byte alto de expansión de memoria Reservado 0A 0B 0C 0D Status Register A Status Register B Status Register C Status Register D 2E-2F 30 31 32 Checksum del CMOS (registros 10h a 2Fh) Byte bajo de expansión de memoria Byte alto de expansión de memoria Byte de siglo de fecha 0E 0F Byte de estados de diagnóstico Byte de estado de Shutdown 33 34-3F Flag de información (seteado durante power on) Reservado Autor: Alejandro Furfaro 44 Reloj en Tiempo Real 1 1 1 1 Al tener 64 registros internos, utiliza el modo de direccionamiento indirecto para evitar consumir demasiadas direcciones de E/S. Se muestra al procesador como dos ports: Uno de direcciones (en donde escribimos el número del registro interno con el cual queremos transaccionar), y otro de datos (en donde realizamos la transacción). READ: mov al,Memory_location out 70h, al in al,71h Autor: Alejandro Furfaro WRITE: mov out mov out al,Memory_location 70h,al al,New_contents 71h,al 45 Reloj en Tiempo Real Status Register A 7 6 UIP UIP 5 4 3 DV DV0-2 0-2 Update Update in in progress. progress. 2 RS RS3-0 3-0 1: 1: Indica Indica ciclo ciclo de de actualización actualización del del reloj reloj en en proceso. proceso. 0: 0: Indica Indica fecha fecha yy hora hora listas listas para para su su lectura lectura Autor: Alejandro Furfaro 1 0 RS : Rate Selection bits. RS3-0 3-0: Rate Selection bits. Seleccionan Seleccionan el el divisor divisor de de frecuencia frecuencia de de salida. salida. El El sistema sistema inicializa inicializa este este valor valor en en 0110. 0110. Esto Esto selecciona selecciona una una señal señal cuadrada cuadrada de de salida salida de de 1024 1024 Hz, Hz, oo lo lo que que es es igual igual un un período período de de 0,976562 0,976562 mseg. mseg. DV : DV2-0 2-0: Divisor Divisor de de 22 22 etapas etapas que que permite permite setear setear la la frecuencia frecuencia de de la la base base de de tiempos tiempos del del sistema. sistema. El El power power on on self self test test lo lo coloca coloca en en 010 010 de de modo modo de de establecer establecer 32,768 32,768 Khz. Khz. 46 Reloj en Tiempo Real Status Register B 7 6 5 4 3 2 1 0 SQWE DM Set 24/12DSE Set PIE DM 24/12 DSE PIE AIE AIE UIE UIESQWE Update-Ended Update-Ended Interrupt Interrupt Enable. Enable. Habilita Habilita (activo (activo alto) alto) el el envío envío de de interrupción interrupción cada cada vez vez que que actualiza actualiza fecha fecha yy hora. hora. Alarm Alarm Interrupt Interrupt Enable. Enable. Activo Activo alto. alto. Habilita Habilita el el envío envío de de una una interrupción interrupción en en la la fecha fecha yy hora hora de de alarma alarma programada. programada. Periodic Periodic Interrupt Interrupt Enable. Enable. Activo Activo alto. alto. Habilita Habilita el el envío envío de de una una señal del señal de de interrupción interrupción aa períodos períodos establecidos establecidos en en los los bits bits RS RS3-0 3-0 del Status Status Register Register A. A. 0: 0: Se Se actualiza actualiza el el reloj reloj aa razón razón de de una una cuenta cuenta por por segundo. segundo. 1: 1: Se Se detiene detiene la la actualización actualización permitiendo permitiendo inicializar inicializar los los 14 14 registros registros sin sin interrupción interrupción hasta hasta que que vuelva vuelva aa ponerse ponerse en en ‘0’. ‘0’. Autor: Alejandro Furfaro 47 Reloj en Tiempo Real 7 Status Register B 6 5 4 3 2 1 0 SQWE DM Set 24/12DSE Set PIE DM 24/12 DSE PIE AIE AIE UIE UIESQWE Daylight Daylight Saving Saving Enable. Enable. El El POST POST lo lo inicializa inicializa en en 0, 0, indicando indicando que que no no está está habilitado habilitado 0: 0: Modo Modo 12 12 hs. hs. 1: 1: Modo Modo 24hs. 24hs. (El (El POST POST lo lo inicializa inicializa de de este este modo) modo) Date Date Mode. Mode. 0: 0: Fecha Fecha yy hora hora se se actualizan actualizan en en BCD BCD (El (El POST POST lo lo inicializa inicializa de de este este modo). modo). 1: 1: Fecha Fecha yy hora hora se se actualizan actualizan en en Binario. Binario. Square Square Wave Wave Enable. Enable. Activo Activo alto. alto. Habilita Habilita la la generación generación de de una una onda onda cuadrada cuadrada aa intervalos intervalos establecidos establecidos en en el el Status Status Register Register A. A. Autor: Alejandro Furfaro 48 Reloj en Tiempo Real 7 6 Status Register C 5 4 3 2 1 0 PF PF AF AF UF UF Bits Bits Read Read only, only, que que reflejan reflejan el el estado estado de de los los bits bits PIE, PIE, AIE, AIE, yy UIE UIE del del Status Status Register Register BB Status Register D Valid Valid RAM RAM and and Time. Time. Indica Indica con con un un 00 que que el el sistema sistema no no tiene tiene alimentación alimentación suficiente suficiente (batería (batería de de Litio Litio baja) baja) Autor: Alejandro Furfaro 7 6 5 4 3 2 1 0 VRT VRT 49 El Bus de expansión ISA Motherboard Memoria Microprocesador Vista frontal del conector del bus ISA Autor: Alejandro Furfaro 50 El Bus de expansión ISA: Señales Pin A1 Conector Bus PC y PC XT S eñal E/S Pin S eñal *I/O CH CK E B1 GND E/S P Pin C1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20 A21 A22 A23 A24 A25 A26 A27 A28 A29 A30 A31 SD7 SD6 SD5 SD4 SD3 SD2 SD1 SD0 IO CH RDY AEN SA19 SA18 SA17 SA16 SA15 SA14 SA13 SA12 SA11 SA10 SA9 SA8 SA7 SA6 SA5 SA4 SA3 SA2 SA1 SA0 S P E P E P E P P S S E/S E/S S E S E S S E E E E E S S S P S P C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17 C18 Autor: Alejandro Furfaro E/S E/S E/S E/S E/S E/S E/S E/S E S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15 B16 B17 B18 B19 B20 B21 B22 B23 B24 B25 B26 B27 B28 B29 B30 B31 *RESET + 5V IRQ 2 - 5V DRQ 2 - 12V CRDSEL + 12V GND *SM EM W *SM EM R *IOW *IOR *DACK 3 DRQ 3 *DACK 1 DRQ 1 *DACK 0 CLK IRQ 7 IRQ 6 IRQ 5 IRQ 4 IRQ 3 *DACK 2 T/C ALE + 5V OSC GND Conector adicional Bus IS A (AT 286 y superiores) S eñal E/S Pin S eñal E/S *SBHE S D1 *M EM CS16 E LA23 LA22 LA21 LA20 LA19 LA18 LA17 *M RDC *M WTC SD8 SD9 SD10 SD11 SD12 SD13 SD14 SD15 E/S E/S E/S E/S E/S E/S E/S S S E/S E/S E/S E/S E/S E/S E/S E/S D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18 *IO16 IRQ10 IRQ11 IRQ12 IRQ15 IRQ14 *DACK 0 DRQ 0 *DACK 5 DRQ 5 *DACK 6 DRQ 6 *DACK 7 DRQ 7 + 5V *M ASTER16 GND E E E E E E S E S E S E S E P E P Conectores del BUS IS A. Distribución de señales 51 El Bus de expansión ISA: Ejemplo A0 34 33 32 31 30 29 28 27 A1 1 2 3 A2 A3 A6 A7 A8 A9 AEN Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 VCC A4 A5 A B C 6 4 5 1 2 6 4 5 G1 G2A G2B 15 14 13 12 11 10 9 7 VCC 74LS138 13 12 74LS21 1 8 3 10 9 2 2 3 4 5 6 7 8 9 19 1 IOWR A1 A2 A3 A4 A5 A6 A7 A8 G DIR B1 B2 B3 B4 B5 B6 B7 B8 18 17 16 15 14 13 12 11 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 4 3 2 1 40 39 38 37 18 19 20 21 22 23 24 25 14 15 16 17 13 12 11 10 8255 8 7 6 5 4 3 2 1 22 23 19 20 21 RESET RD WR A0 A1 RESET CS PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7 74LS245 IORD PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7 74LS21 74ALS32 D0 D1 D2 D3 D4 D5 D6 D7 5 36 9 8 35 6 D0 D1 D2 D3 D4 D5 D6 D7 D0 D1 D2 D3 D4 D5 D6 D7 RD WR A0 A1 CLK0 G0 OUT0 CLK1 G1 OUT1 CLK2 G2 OUT2 9 11 10 15 14 13 18 16 17 CS 8254 IRQ9 Autor: Alejandro Furfaro 52 SIMM Single In-Line Memory Module. Anchos de bus Un SIMM de 30 contactos soporta ocho bits de datos; un SIMM de 72 contactos soporta 32 bits de datos. Autor: Alejandro Furfaro 53 Small Outline DIMM (de contorno pequeño) o SO DIMM. Tipo de memoria que se usa comúnmente en laptops y portátiles DIMM Dual In-Line Memory Module. Autor: Alejandro Furfaro 54 Controlador de memoria 1 1 1 1 Microprocesadores dedicados a la supervisión de la transferencia de datos hacia y desde la memoria. Desempeñan un rol activo en el proceso de corrección de errores, por medio de ciertos métodos, tales como paridad y ECC(Error Correction Code). La diferencia entre ECC y paridad es que ECC es capaz de detectar y corregir los errores de un bit sin que el usuario se dé cuenta de que se ha producido un error. Ciertos tipos de controladores de memoria implementan algoritmos ECC capaz detectar errores en 2, 3 ó 4 bits de memoria. Sin embargo, aún cuando ECC puede detectar estos errores de múltiples bits, sólo puede corregir los errores de un bit. Si se presenta el caso de un error de múltiples bits, el circuito ECC devuelve un error de paridad. Autor: Alejandro Furfaro 55 Tecnologías de DRAM 1A fines de los 80’s y principios de los 90`s las CPU 80486 ejecutaban a 33 MHz, velocidad similar a la del bus del sistema. 1 Se utilizaban memorias DRAM de Página Rápida (FP = Fast Page), montada en módulos SIMM (Single Inline Memory Modules), cuya latencia o tiempo de acceso era de 100 nseg y su velocidad de 16 MHz, es decir la mitad aproximadamente de la velocidad del bus. Autor: Alejandro Furfaro 56 Tecnologías de DRAM 1 Memoria EDO 2 1 La memoria de Extended Data Output, o EDO, permite la salida de datos aún cuando la señal CAS haya terminado. De este modo se pudo progresar de velocidades de 33 MHz, a 66 MHz, alcanzando la mitad de la velocidad de los procesadores Pentium que en ese momento trabajaban a 133 MHz. En ancho del bus se llevó a 64 bits, y el tiempo de acceso o latencia standard de esta tecnología fue de 70 nseg. (10 a 15% más rápida que los chips de modalidad de paginación rápida). SDRAM 2 2 2 La DRAM sincrónica es una tecnología de DRAM que utiliza un reloj para sincronizar la entrada y la salida de señales en un chip de memoria. El reloj está coordinado con el reloj de la CPU, para que la temporización de los chips de la memoria y de la CPU estén sincronizados. Permite temporizar las address y los datos en un solo ciclo de clock, hecho que redujo el tiempo de acceso a 58 nseg. ( un 20% superior a la de la memoria EDO). La organización de estos subsistemas de memoria pasó del montaje SIMM al DIMM conservando el ancho de bus en 64 bits. Posteriormente llegaron a velocidades de 100 MHz. corriendo detrás de los requerimientos de los procesadores Pentium, y su tiempo de acceso bajó a 56 nseg. Autor: Alejandro Furfaro 57 Tecnologías de DRAM 1 RAMBus 2 2 1 En 1999 Intel anunció la tecnología Rambus que permitiría partir de 1,6 Gbps de velocidad de transferencia, y agregando un segundo canal Rambus, llegar a 3,2 Gbps. Sin embargo su elevado costo, la complejidad que introducía en el diseño de los mother boards, y varios problemas en su implementación llevaron a los fabricantes de DRAMs a descartar esta solución, ya que los beneficios de performance no eran significativos cuando se efectuaban benchmarks frente a las otras tecnologías. Esto demostró que la performance del sistema en lo que a la memoria se refiere, no depende tanto del ancho de banda del bus, como de la latencia (tiempo de acceso) que de acuerdo a la práctica es lo que manda. “Ahora que el ancho de banda del bus ha llegado hasta donde queremos y que el caché está en su máximo, ¿qué debemos hacer a continuación?. El siguiente paso natural es acelerar el propio array de DRAM . Dataquest estima que las actuales tecnologías serán reemplazadas por otras de acceso rápido en el largo plazo. En el 2005, la mitad del mercado de u$s50 Billones de DRAM consistirán en DRAMs de acceso rápido” . Jim Handy, Principal Analyst, Dataquest. Dataquest Perspective: “Defining the Market For Low Latency” 15 de Mayo de 2000 Autor: Alejandro Furfaro 58 Tecnologías de DRAM Chip típico de 256 Mbits de DRAM, organizado en 4 bancos internos de 64 Mbits cada uno de los cuales se compone de dos mitades de 8192 líneas de word (8 K líneas) y 4096 líneas de bits (4 Klíneas). La salida de información tiene lugar mediante las líneas de datos globales Autor: Alejandro Furfaro 59 Tecnologías de DRAM Arquitectura DRAM Standard comparada con el array SRAMDRAM combinado. El caché SRAM toma la función de los Sense Amplifiers (SA) secundarios. A pesar de mover sólo los datos desde las celdas especificadas por la señal CAS a través de las líneas de bit en los sense amps secundarios, la cantidad total de datos dentro de una fila activada se mueve al caché de fila. En consecuencia un requerimiento de lectura llamará los datos desde las celdas rápidas de SRAM. Al mismo tiempo el array DRAM volverá al estado idle tan pronto como se haya ejecutado el comando “auto precharge all”. Autor: Alejandro Furfaro 60 Tecnologías de DRAM Diagrama detallado de la ESDRAM. Reemplazando los sense amps secundarios con un registro SRAM se reduce el riesgo de pasar por los sense amps primarios cuando se transmite la señal a las líneas globales de datos. Esto resulta en mayor velocidad de lectura que compensa con creces el tiempo que se toma el sistema en volcar los datos en el caché de fila. Autor: Alejandro Furfaro 61 Tecnologías de DRAM 1 DDR or SDRAM II 2 Double Data Rate SDRAM es la siguiente generación a la SDRAM. La DDR se basa en el diseño de la SDRAM, con mejoras que suponen un aumento de la velocidad de transferencia. Como resultado de esta innovación, la DDR permite la lectura de datos tanto en la fase alta como baja del ciclo del reloj, con lo que se obtiene el doble de ancho de banda que con la SDRAM estándar. La DDR duplica la velocidad respecto a la tecnología SDRAM sin aumentar la frecuencia del reloj. Autor: Alejandro Furfaro 62