Práctica 2 - Universitat de les Illes Balears

Anuncio

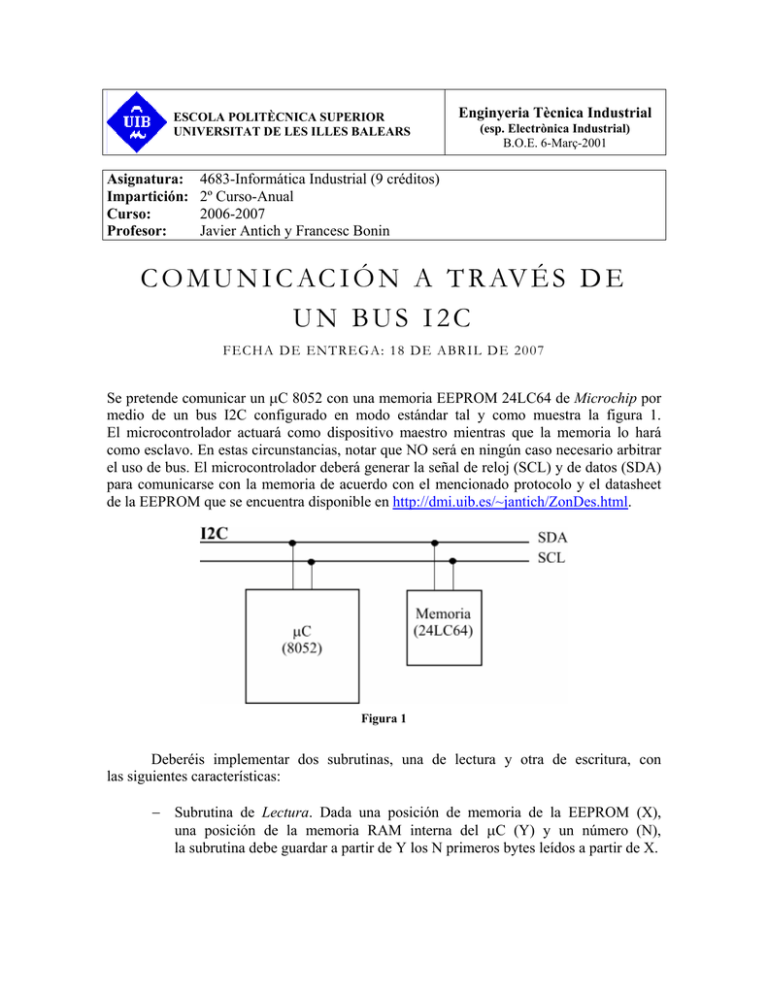

ESCOLA POLITÈCNICA SUPERIOR UNIVERSITAT DE LES ILLES BALEARS Asignatura: Impartición: Curso: Profesor: Enginyeria Tècnica Industrial (esp. Electrònica Industrial) B.O.E. 6-Març-2001 4683-Informática Industrial (9 créditos) 2º Curso-Anual 2006-2007 Javier Antich y Francesc Bonin C O M U N I C AC I Ó N A T R AV É S D E UN BUS I2C FECHA DE ENTREGA: 18 DE ABRIL DE 2007 Se pretende comunicar un μC 8052 con una memoria EEPROM 24LC64 de Microchip por medio de un bus I2C configurado en modo estándar tal y como muestra la figura 1. El microcontrolador actuará como dispositivo maestro mientras que la memoria lo hará como esclavo. En estas circunstancias, notar que NO será en ningún caso necesario arbitrar el uso de bus. El microcontrolador deberá generar la señal de reloj (SCL) y de datos (SDA) para comunicarse con la memoria de acuerdo con el mencionado protocolo y el datasheet de la EEPROM que se encuentra disponible en http://dmi.uib.es/~jantich/ZonDes.html. Figura 1 Deberéis implementar dos subrutinas, una de lectura y otra de escritura, con las siguientes características: − Subrutina de Lectura. Dada una posición de memoria de la EEPROM (X), una posición de la memoria RAM interna del μC (Y) y un número (N), la subrutina debe guardar a partir de Y los N primeros bytes leídos a partir de X. Comunicación a través de un bus I2C Javier Antich, Francesc Bonin La memoria EEPROM permite la lectura de datos de acuerdo con tres tipos de operaciones básicas denominadas Current Address Read, Random Read y Sequential Read. Se deberán implementar tres versiones de la mencionada subrutina, cada una de ellas haciendo uso de un tipo de operación. Notar que, de forma excepcional, la implementación de la subrutina mediante operaciones de tipo Current Address Read podrá hacer uso de una única operación Random Read. Antes de llevar a cabo la lectura, deberéis realizar las siguientes comprobaciones/validaciones: • La posición de memoria X (X + N) debe encontrarse dentro del rango de posibles direcciones de la EEPROM. • La posición de memoria Y (Y + N) debe pertenecer a los 128 bytes altos de la memoria RAM interna del μC (80h<=Y<=FFh). • N debe ser un número positivo mayor que cero. La velocidad de las transferencias de datos I2C será de 50 Kbps, y la generación de las señales SCL y SDA se hará haciendo uso de temporizadores. − Subrutina de Escritura. Dada una posición de memoria de la EEPROM (X), una posición de la memoria RAM interna del μC (Y) y un número (N), la subrutina debe escribir a partir de X los N primeros bytes leídos a partir de Y. La memoria EEPROM permite la escritura de datos de acuerdo con dos tipos de operaciones básicas denominadas Byte Write y Page Write. Se deberán implementar dos versiones de la mencionada subrutina, cada una de ellas haciendo uso de un tipo de operación. Se realizarán las mismas comprobaciones/validaciones que para la subrutina de lectura. La velocidad de las transferencias de datos I2C será, en este caso, de 100 Kbps, y la generación de las señales SCL y SDA se hará SIN la ayuda de temporizadores. 2 Comunicación a través de un bus I2C Javier Antich, Francesc Bonin ENTORNO DE DESARROLLO La práctica se llevará a cabo haciendo uso del entorno de desarrollo Pinnacle 52. Para ello, deberemos configurar adecuadamente dicho entorno. Por un lado, debemos seleccionar el microcontrolador sobre el que queremos trabajar (μC 8052). Esta operación se realiza desde el menú “Project ⇒ Project Options ⇒ Microcontroller Options”. Por otro lado, para simular el esquema de la figura 1, debéis seguir los siguientes pasos: 1. Acceder a “Project ⇒ Project Options ⇒ I2C Bus Configuration”. Os aparecerá la ventana de la figura 2 desde donde podréis configurar las líneas de los puertos de E/S del microcontrolador que representarán las líneas SDA y SCL del bus I2C. Aunque se pueden simular dos buses denominados 1 y 2, realizar únicamente la configuración para el primero de ellos. 2. Acceder a “Project ⇒ Project Options ⇒ Serial I2C EEPROM 24LC64”. Os aparecerá la ventana de la figura 3 desde donde podréis asignar una dirección al dispositivo esclavo conectándolo, además, al bus 1 previamente configurado. A partir de aquí, SÓLO queda implementar el algoritmo que cumpla con la funcionalidad descrita generando las señales SDA y SCL a través de las líneas de E/S definidas en el paso 1. Por otro lado, notar que la funcionalidad de la EEPROM está ya implementada por Pinnacle 52. Finalmente, si durante la ejecución de vuestro programa queréis observar las transferencias que circulan por el bus así como el contenido de la memoria, lo podréis hacer accediendo al menú “View ⇒ I2C Devices” (ver figura 4). Figura 2 3 Comunicación a través de un bus I2C Javier Antich, Francesc Bonin Figura 3 Figura 4 4 Comunicación a través de un bus I2C Javier Antich, Francesc Bonin NOTA IMPORTANTE Cada alumno deberá entregar un informe en donde se explique claramente la solución dada al problema, y se presente el programa resultante comentado así como varios resultados de simulación obtenidos con la herramienta Pinnacle 52 que demuestren la validez de la solución aportada. En la primera página del informe deberá constar el nombre de la asignatura, el título de la práctica, el curso académico, el número asignado al grupo de prácticas, el nombre del autor del informe (en negrita) y, finalmente, el nombre del otro miembro del grupo (texto normal). Tras la entrega de la práctica, se acordará una fecha con cada grupo para la defensa de la misma con una duración aproximada de 30 minutos. La nota final se calculará de la siguiente forma: 10 % – Defensa 20 % – Informe 70 % – Solución al problema planteado No se aceptará ninguna práctica después del plazo de entrega establecido!!! 5