EJERCICIO Se dispone de un módulo de entrada/salida conectado

Anuncio

EJERCICIO

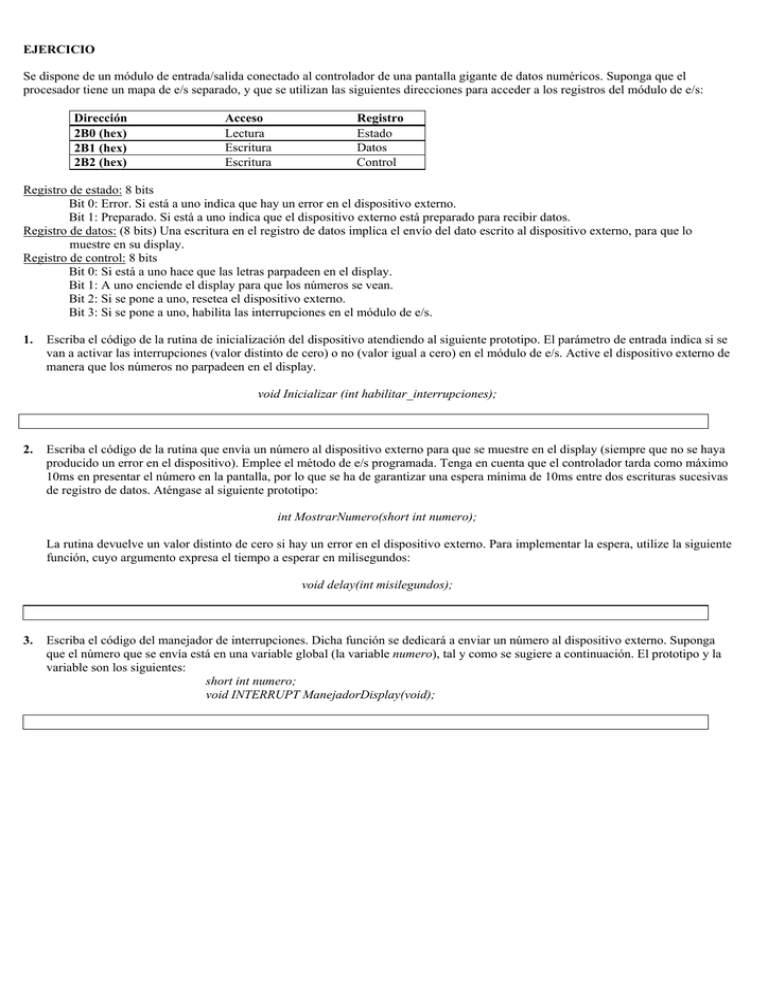

Se dispone de un módulo de entrada/salida conectado al controlador de una pantalla gigante de datos numéricos. Suponga que el

procesador tiene un mapa de e/s separado, y que se utilizan las siguientes direcciones para acceder a los registros del módulo de e/s:

Dirección

2B0 (hex)

2B1 (hex)

2B2 (hex)

Acceso

Lectura

Escritura

Escritura

Registro

Estado

Datos

Control

Registro de estado: 8 bits

Bit 0: Error. Si está a uno indica que hay un error en el dispositivo externo.

Bit 1: Preparado. Si está a uno indica que el dispositivo externo está preparado para recibir datos.

Registro de datos: (8 bits) Una escritura en el registro de datos implica el envío del dato escrito al dispositivo externo, para que lo

muestre en su display.

Registro de control: 8 bits

Bit 0: Si está a uno hace que las letras parpadeen en el display.

Bit 1: A uno enciende el display para que los números se vean.

Bit 2: Si se pone a uno, resetea el dispositivo externo.

Bit 3: Si se pone a uno, habilita las interrupciones en el módulo de e/s.

1.

Escriba el código de la rutina de inicialización del dispositivo atendiendo al siguiente prototipo. El parámetro de entrada indica si se

van a activar las interrupciones (valor distinto de cero) o no (valor igual a cero) en el módulo de e/s. Active el dispositivo externo de

manera que los números no parpadeen en el display.

void Inicializar (int habilitar_interrupciones);

2.

Escriba el código de la rutina que envía un número al dispositivo externo para que se muestre en el display (siempre que no se haya

producido un error en el dispositivo). Emplee el método de e/s programada. Tenga en cuenta que el controlador tarda como máximo

10ms en presentar el número en la pantalla, por lo que se ha de garantizar una espera mínima de 10ms entre dos escrituras sucesivas

de registro de datos. Aténgase al siguiente prototipo:

int MostrarNumero(short int numero);

La rutina devuelve un valor distinto de cero si hay un error en el dispositivo externo. Para implementar la espera, utilize la siguiente

función, cuyo argumento expresa el tiempo a esperar en milisegundos:

void delay(int misilegundos);

3.

Escriba el código del manejador de interrupciones. Dicha función se dedicará a enviar un número al dispositivo externo. Suponga

que el número que se envía está en una variable global (la variable numero), tal y como se sugiere a continuación. El prototipo y la

variable son los siguientes:

short int numero;

void INTERRUPT ManejadorDisplay(void);

EJERCICIO

Imagínese por un momento que trabaja como ingeniero de sistemas informáticos en una famosa compañía

aeronáutica y desea diseñar el sistema de control de vuelo de un nuevo avión dedicado al transporte de patitos de

goma desde Murcia a Hong Kong. Según sus superiores, el sistema constará de los siguientes elementos:

•

CPU con entrada / salida separada. Interrupciones vectorizadas del tipo x86 (INTR + INTA) y una entrada de

interrupción no enmascarable (NMI).

• Memoria dinámica y ROM. En esta última se ubica el programa.

• Caché separada para datos e instrucciones.

• Tres interfaces de periféricos programables 8255. Estos se utilizarán para manejar los siguientes elementos.

• Dos controladores de motores. Uno de ellos controla los dos motores destinados a mover las superficies

móviles de las alas, y el otro los de los timones de profundidad del aparato. Cada controlador recibe 8 bits

de datos correspondientes a la posición deseada de cada uno de sus motores, y no necesita de señales de

protocolo de comunicación para recibir dichos datos. El dato enviado al controlador es instantáneamente

procesado por éste.

• Un controlador de palanca de mando. Dicho controlador envía continuamente dos datos de 8 bits,

correspondientes a los valores de X e Y de la palanca de mando. No necesita protocolo de comunicación.

• Un controlador de pulsadores de cabina. El controlador envía un dato de 8 bits correspondiente al código

del pulsador que ha sido pulsado, y señales de protocolo de comunicación. Es necesario que la pulsación

de la tecla genere una interrupción de tratamiento de pulsador.

• Un controlador de detección de alarmas y emergencias. Este envía un dato de 8 bits correspondiente al

código de alarma, y dispone de señales de protocolo de comunicación. Es necesario que cuando se

produzca una alarma se genere una interrupción de gestión de alarma, que debe de ser servida

obligatoriamente por el procesador.

• Controlador de interrupciones 8259A.

a) (1,75 puntos) Suponga que otro ingeniero ha conectado dichos elementos al bus del sistema y ha realizado

toda la lógica de selección de direcciones del sistema. Conecte los controladores a los 8255. Indique a qué puerto

conecta las señales de los controladores, e indique el modo de funcionamiento de los grupos de los 8255, y si

utilizan o no interrupciones. En el caso de que algún grupo utilice interrupciones, saque la señal del puerto donde

se generará la señal correspondiente y conéctelo a donde le parezca. Acompañe su solución de una explicación y

tenga en cuenta que no se puede añadir ningún elemento más al sistema (ni siquiera puertas lógicas).

b) (0,5 puntos) ¿Tendría alguna utilidad un módulo DMA en dicho sistema? Razone la respuesta.

c) (0,25 puntos) Suponga que el software del sistema consiste en una rutina de configuración del sistema y otra

(la rutina principal) que ejecuta un bucle infinito como el siguiente:

Hacer {

Leer valores de la palanca de mando;

Consultar parámetros de funcionamiento de la memoria del sistema;

Calcular posición deseada de los motores en función de los valores de la palanca de mando y de los

parámetros de funcionamiento;

Escribir posición deseada en los puertos de entrada/salida de las alas y los timones;

}Mientras (verdadero):

¿Qué tipo de programación de la entrada /salida se está aplicando con este bucle?

d) (1 punto) ¿Cómo se las arreglaría para introducir las dos rutinas enunciadas a continuación? No se puede

alterar el código de la rutina principal. ¿Qué necesitaría hacer en la rutina de configuración? Razone la respuesta.

• Gestión de pulsadores: cuando un pulsador ha sido pulsado, se recoge el código del pulsador y en función del

mismo se alteran los parámetros de funcionamiento del sistema.

Gestión de alarmas: cuando se produce una alarma, se recoge el valor de la alarma y se altera el valor de los

parámetros de funcionamiento del sistema.

EJERCICIO

Se desea construir una caché para un computador. Para implementarla se ha construido un sistema con un microcontrolador asociado a

un sistema de E/S que se comunica con el computador principal de esta forma:

1 ms

(*)AS

No determinado. Hay que esperar a la MP.

(+)Mem Op OK

(*)A0-A15

1 ms

Sistema Caché

CPU

Dirección

Datos de MP

(+)Data In 0-7

Ciclo

de

lectura

(*)W/R#

(*)Data Out 0-7

Datos de la CPU a MP

Ciclo de

escritura

(*)W/R#

Leyenda:

(*) Generada por la CPU.

DataIn,

DataOut

8255 (1)

8255 (3)

8255 (2)

8255 (4)

µC

MP del

µC

A0-15, W/R#, AS,

MemOpOK

DataIn,

DataOut

MP

de la

CPU

A0-15, W/R#,

AS,

MemOpOK

Bus del

sistema

(+) Generada por la memoria.

8255

La CPU es un procesador con E/S mapeada en memoria y un bus asíncrono no multiplexado de direcciones de 16 bits y datos de 8 bits,

con las señales que se indican en el cronograma. Téngase en cuenta que existen dos grupos de señales para datos: Data in 0-7, que se

dedica a enviar los datos de la memoria a la CPU y Data out 0-7 que lleva los datos de la CPU a la memoria principal. El

microcontrolador (µC) es un procesador con un bus compatible con el del 8088-6 (con E/S separada), pero con una diferencia: sólo

tiene una línea de interrupción (sin aceptación), y no es vectorizada. La dirección base del 8255(1) es la 100hex y la del 8255(2) es la

200hex. La del 8255(3) es la 300hex y la del 8255(4) es la 400hex. La caché es serie, totalmente asociativa y tiene 256 líneas con bloques de

16bytes. La gestión de la caché la realiza un programa del µC, de manera que las líneas de la caché están implementadas como variables

globales del programa del µC.

1. (0.25 pto) Dibuje la conexión entre la CPU y el sistema caché, indicando exactamente los puertos y señales que utiliza, así como los

modos de funcionamiento de cada 8255. No se utilizan interrupciones.

2. (0.25 pto.) Indique las señales y los modos de funcionamiento del 8255(3) y 8255(4), indicando exactamente los puertos y señales

que utilizan. No se utilizan interrupciones.

3. (0.25 pto.) Declare las variables globales que necesite para implementar y manejar las líneas del sistema caché. Escriba en C la

función void Inicializacion(void) en el que se realiza la inicialización del sistema.

4. (0.75 pto.) Escriba en C la función int localizar(short int direccion) en la que se implementa la estrategia de localización de la

caché. La función da un número de línea como resultado: si el número es negativo indicará que no se ha podido localizar el dato

correspondiente a la dirección especificada. Esta función sólo intenta localizar el bloque, no a subir bloques de MP a caché. Use el

operador x >> n que desplaza los bits de la variable x, n bits a la derecha.

5. (0.75 pto.) Escriba en C la función int dondeubicar(short int direccion) en la que se implementa la estrategia de ubicación de la

caché. La función da un número de línea como resultado. Esta función decide dónde ubicar un bloque, sin subir el bloque a caché.

Utilice la estrategia de reemplazo aleatoria. Apóyese en la sentencia rand()%n que genera un número aleatorio entre 0 y n-1.

6. (1 pto.) Escriba en C la función void subirbloque(shor int direccion). La función sube el bloque a caché, correspondiente a la

dirección que se pasa como parámetro (que no tiene porqué ser la primera dirección del bloque). Apóyese en la función y los

operadores anteriormente descritos.

7. (1 pto.) Escriba en C la función void procesarLecturaCPU(void). La función se encarga de esperar a que la CPU realice un ciclo de

bus de lectura, recoger la dirección, gestionar la caché y devolverle el dato a la CPU. Apóyese en las funciones anteriores y en la

función C, void delay(int x), que retrasa la ejecución el programa x milisegundos. Realice la función con E/S programada.

8. (0.25 pto.) Imagínese que se conecta un módulo de E/S al bus del sistema principal y que no se utiliza DMA para la transferencia de

datos entre la E/S y la memoria principal. ¿Habría que realizar algún cambio en el sistema de caché? Justifique la respuesta.

9. (0.5 pto.) Se desea implementar la gestión de la caché por interrupciones. Enumere los cambios necesarios, tanto hardware como

software para implementar dicha estrategia. Justifique la respuesta.

EJERCICIO

7. Un sistema basado en 8086 está conectado a un 8255, para la recepción de datos provenientes de un

dispositivo externo. El esquema de conexión se indica a continuación:

8255-A

D0-D7

A0

A1

A2...A11

WR#

RD#

IO/M#

D0-D7

Decodificación

Pto. A

A0

A1

CS#

Pto. CH

WR#

RD#

Pto. CL

Pto. B

Datos

Protocolo

Señales de control

Dispositivo externo

CPU

Señales de estado

La decodificación de direcciones activa la señal CS# en el rango de direcciones 0A00-0A03. Sabiendo que los

datos se reciben de acuerdo a un protocolo de señales (implementado mediante las señales de la parte alta del

puerto C del 8255), y que no se necesita un protocolo de comunicación para enviar o recibir las señales de

control o estado, responda a las siguientes cuestiones:

a) (0.5pto.) Escriba en C la rutina de inicialización del 8255, teniendo en cuenta que no se activan

interrupciones.

b) (0.5pto.) Escriba en C una rutina que le envíe las señales de control al dispositivo externo y recoja del

mismo las señales de estado, y las devuelva como resultado de la función. Aténgase al siguiente

prototipo:

unsigned char EnviarControl(unsigned char s_control);

c) (1pto.) Imagine que se quieren implementar interrupciones en dicho sistema. Explique qué cambios

se tendrían que producir tanto en el hardware como en el software de los apartados anteriores.

d) (1pto.) Con las interrupciones habilitadas, escriba en C la rutina de servicio de interrupción que

recoge un dato del puerto A, y guarda el valor recogido en una variable global.

EJERCICIO.

Se desean transferir 4096 bytes desde la memoria a un determinado dispositivo. Para ello se han de observar las

siguientes consideraciones:

1.

2.

3.

4.

La CPU tiene un reloj de 1Mhz y ejecuta una instrucción cada ciclo de reloj.

El dispositivo es capaz de transferir 1 byte cada 10ms.

Se necesitan 200 instrucciones de la CPU para transferir un byte desde la CPU hasta el dispositivo.

La CPU necesita hacer 20 instrucciones para entrar en una rutina de interrupción y otras 20 para salir de la

misma.

5. Se necesitan 20 instrucciones para programar la órden de transferencia del DMA.

6. Se necesitan 80 instrucciones para chequear la operación del DMA.

Se pide:

(1) Especificar cuanto tiempo tiene que dedicar el procesador a la transferencia de los datos si se supone que

dicha operación se hace por entrada salida programada. Supóngase que el número de instrucciones del bucle de

chequeo del periférico es 0.

(1) Especificar cuanto tiempo tiene que dedicar el procesador a la transferencia de los datos si se supone que

dicha operación se hace por interrupciones.

(1) Especificar cuanto tiempo tiene que dedicar el procesador a la transferencia de los datos si se supone que

dicha operación se hace por DMA. Se supone que se hace toda la transferencia en una sola orden y que el DMA la

realiza con éxito.

(0,5) ¿Qué método de programación de la E/S es el más eficiente? ¿Porqué?

SEGUNDO EJERCICIO.

Dado un sistema compuesto por CPU, E/S y memoria, se le pide diseñar un DMA para dicho sistema que trabaje

con el único módulo de E/S que tiene éste. Para ello dispone de un pequeño microcontrolador (que hará las veces

de DMA) y un banco de registros conectados al bus del sistema (el bus tiene una palabra de 32 bits) tal y como

aparece en la siguiente figura:

CPU

Módulo de E/S

DATOS

ST_ES

MicroC

(DMA)

Memoria

CTRL

INT

Banco de registros

ESTADO

CONTROL_0

CONTROL_1

CONTROL_2

Considere los siguientes registros: los bits que no se comentan no son importantes para el ejercicio.

• ESTADO: (8 bits, R/W). Registro dedicado a indicar el resultado de una operación del DMA.

o Bit 0: a cero indica que la operación se ha realizado correctamente, y a 1 que ha ocurrido un error.

• CONTROL_0: (32 bits R/W) Contiene la dirección de memoria (de origen o destino) de la operación de

transferencia.

• CONTROL_1: (32 bits R/W) Contiene el tamaño en bytes de la operación de transferencia, codificado

como un entero sin signo.

• CONTROL_2: (8 bits R/W) Utilizado por la CPU para indicar el sentido de la operación.

o Bit 0: a 1 indica que la transferencia es desde memoria a E/S, y a cero lo contrario.

o Bit 1: a 1 indica al DMA que debe de comenzar una operación de transferencia con los datos que

se le indican en los registros de control. El DMA pondrá este bit a cero cuando finalice ésta.

• DATOS: (32 bits R/W) Se utiliza para leer o escribir datos en el módulo de E/S, por parte de la CPU o del

DMA.

• ST_ES: (8 bits R). Si tiene algún bit distinto de cero indica error en la última operación del módulo E/S.

• CTRL.: (8 bits W). Indica que tipo de operaciones se van a realizar sobre el módulo de E/S.

o Bit 0: a cero, operaciones de escritura. A uno, operaciones de lectura.

o

El módulo de E/S produce una señal de interrupción cuando está preparado para recibir un nuevo dato desde la

CPU o el DMA (ops. de escritura) o cuando ha llegado un nuevo dato al módulo desde el exterior (ops. de lectura)

y puede leerse por la CPU o el DMA.

(1 pto.) Implemente en C la siguiente función:

EsperarOrdenDMA(void *dir_memoria, int *sentido, unsigned int *size)

Dicha función se ejecutará dentro del DMA, y esperará a que la CPU principal indique que quiere realizar una

transferencia DMA (utilice para ello el bit 1 del registro CONTROL_2). Utilice E/S programada para ello.

Después de que la CPU haya indicado que quiere dar comienzo la transferencia, la función retornará mediante sus

parámetros de entrada la dirección de memoria de la transferencia, el sentido de ésta (0 para transferir al módulo

de E/S y 1 para transferir a la memoria), y el tamaño en bytes de la misma. Puede considerar los nombres de los

registros como constantes en su código. Si lo cree conveniente, utilice las siguientes funciones, que son capaces

de operar con palabras completas:

void outportb32(unsigned int valor, unsigned int puerto)

unsigned int inportb32(unsigned int puerto)

(1 pto.) Desde el punto de vista de la programación del propio DMA, ¿Con qué tipo de programación de E/S

debería de implementarse la transferencia de datos entre la E/S y la memoria? Sea cual sea la opción, ¿Qué

acciones tendrían que realizarse para realizar una SOLA transferencia desde memoria a E/S? Razone la respuesta.

(0.5 pto.) Escribir el código C necesario para que la CPU principal le pida al DMA que transfiera 1024 bytes

desde la dirección FFAD0 al módulo E/S. No olvide hacer que este código sea compatible con la función

EsperarOrdenDMA().

EJERCICIO

Imagine que el ordenador tiene un módulo de E/S que se encarga de controlar la torre de radar, y que dicho

módulo tiene una señal de interrupción que va dirigida a la CPU y que le avisa de cuando se ha producido un

nuevo contacto de radar. En ese momento, la CPU tiene que recoger del registro de datos del dispositivo 1024

bytes, que son los datos pertenecientes al nuevo contacto. Consideraciones:

•

•

•

•

La CPU tiene un reloj de 100Mhz y ejecuta una instrucción cada ciclo de reloj.

El dispositivo es capaz de transferir 1 byte cada microsegundo.

Se necesitan 200 instrucciones de la CPU para transferir un byte desde la CPU hasta el dispositivo.

La CPU necesita hacer 20 instrucciones para entrar en una rutina de interrupción y otras 20 para salir de la

misma.

(1 pto.) Especifique cuanto tiempo tardaría la CPU en gestionar una interrupción proveniente del radar. Razone la

respuesta.

Imagine ahora que la CPU dispone de 4 líneas de interrupción diferentes (INT0 ... INT3), de manera que la CPU

las gestiona por prioridad (mayor prioridad cuanto menor es el número de la línea de interrupción). Cada linea de

interrupción está conectada a un módulo de E/S de radar como el anteriormente comentado, de manera que

puedan controlarse simultáneamente 4 radares diferentes (Radar0 ... Radar3). Supóngase que la rutina de

interrupción hace que el procesador no atienda nuevas interrupciones durante su ejecución, y que la ejecución

completa de una rutina de interrupción dura 3 microsegundos aproximadamente.

Teniendo en cuenta que se producen los siguientes eventos:

•

•

•

•

Nuevo contacto en radar 3 en el instante t.

Nuevo contacto en radar 1 en el instante t+2µs.

Nuevo contacto en radar 3 en el instante t+3µs.

Nuevo contacto en radar 0 en el instante t+4µs.

(2 ptos.) Especifique gráficamente el orden de ejecución de las diferentes rutinas de interrupción, indicando el

instante en el que se inicia y termina su ejecución. Indique además el instante en el que se activa cada una de las

líneas de interrupción. Razone la respuesta.

EJERCICIO

5) (2,5 pto.) Se desea controlar el funcionamiento de un horno microondas utilizando un microprocesador de bajo costo. Para esto, es

necesario controlar el “programa de cocción”, el motor del plato giratorio y la luz interna. Un “programa de cocción” es una pareja

(duración, potencia), que indica el tiempo y la potencia de las microondas para la cocción.

Cuando se desea utilizar el horno el usuario selecciona la duración, la potencia y oprime la tecla comenzar. Toda vez que se abra la

puerta debe detenerse el programa en curso inmediatamente. La luz debe encenderse cuando el horno está en funcionamiento o la

puerta del mismo está abierta. El motor del plato debe girar sólo cuando el horno está en funcionamiento.

Puertos de E/S para acceso a los dispositivos:

MECANISMOS (sólo escritura.):

o Bit 0: Encender (1) o apagar la luz.

o Bit 1: Encender (1) o apagar el motor del plato giratorio.

MICROONDAS (sólo escritura): potencia a generar por el microondas. Para apagar el generador de microondas se debe

escribir un 0 en este puerto.

U_POTENCIA (sólo lectura): potencia del programa seleccionado por el usuario.

U_DURACION (sólo lectura): duración en segundos del programa seleccionado por el usuario.

ENTRADA (sólo lectura):

o Bit 0: Estado de la puerta (0 abierta, 1 cerrada).

o Bit 1: Estado de la tecla comenzar (0 no pulsada, 1 pulsada). Este bit se pone a cero automáticamente después de

una lectura en este puerto.

Nota:

Se dispone de un reloj que genera una interrupción cada segundo, que es atendida por la rutina TIEMPO.

Se pide:

Implemente la rutina de interrupción TIEMPO. Suponga que los puertos de e/s definidos anteriormente

son constantes ya definidas en el programa.