File - Laboratorio de Electrónica

Anuncio

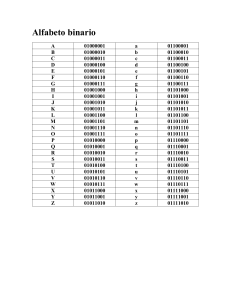

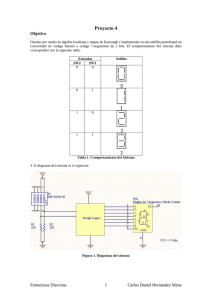

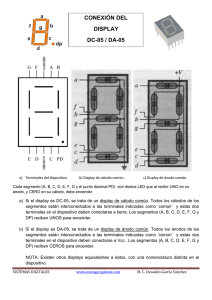

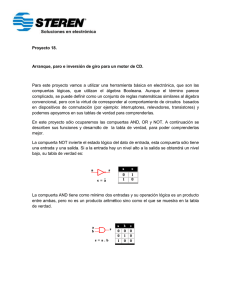

Práctica 1 Transistor BJT Región de Corte Saturación Aplicaciones Universidad de San Carlos de Guatemala, Facultad de Ingeniería, Escuela de Mecánica Eléctrica, Laboratorio de Electrónica 1, Segundo Semestre 2016 OBJETIVOS Utilizar el transistor de Unión Bipolar BJT. Operar en la región de corte/saturación del transistor. Aprender a construir compuertas lógicas con transistores. Comprender los niveles lógicos de voltajes. Lograr diferenciar entre Electrónica Análoga y Digital. MARCO TEÓRICO Electrónica digital: se trata de valores de corrientes y tensiones eléctricas que solo pueden poseer dos estados en el transcurso del tiempo. Encendido o apagado, alto o bajo, 1 o 0, etc. CMOS 3.3V Como su nombre lo indica opera hasta 3.3V, conforme la tecnología ha ido avanzado, los requerimientos de baja potencia se han puesto muy populares, aquí se observa como un nivel de voltaje ha disminuido de 5V a 3V aproximadamente. Para asegurar la compatibilidad, notará que la lógica es compatible con una lógica a 5V un dispositivo 3.3V puede conectarse directamente a uno de 5V y funcionará correctamente, no así en caso contrario. Electrónica analógica: se trata de corrientes y tensiones que varían continuamente de valor en el transcurso del tiempo, para cualquier instante de tiempo. En la actualidad existen dos niveles lógicos muy utilizados, TTL y CMOS 3.3V Niveles lógicos TTL Los niveles lógicos vienen definidos por el rango de tensión comprendida entre 0,0V y 0,8V para el estado L (bajo) y los 5,4V y Vcc para el estado H (alto). Compuertas Lógicas Las computadoras digitales utilizan el sistema de números binarios, que tiene dos dígitos 0 y 1. Un dígito binario se denomina un bit. La información está representada en las computadoras digitales en grupos de bits. La lógica binaria tiene que ver con variables binarias y con operaciones que toman un sentido lógico. La manipulación de información binaria se hace por circuitos lógicos que se denominan compuertas. Produce el NOT, o función complementaria. El símbolo algebraico utilizado para el complemento es una barra sobra el símbolo de la variable binaria. Si la variable binaria posee un valor 0, la compuerta NOT cambia su estado al valor 1 y viceversa. Tabla de Verdad Una tabla de verdad, o tabla de valores de verdad, es una tabla que muestra el valor de verdad de una proposición compuesta, para cada combinación de verdad que se pueda asignar. Compuerta AND cada compuerta tiene dos variables de entrada designadas por A y B y una salida binaria designada por x. La compuerta AND produce la multiplicación lógica AND: esto es: la salida es 1 si la entrada A y la entrada B están ambas en el binario 1: de otra manera, la salida es 0. Compuerta YES un símbolo triángulo por sí mismo designa un circuito separador, el cual no produce ninguna función lógica particular puesto que el valor binario de la salida es el mismo de la entrada. Numeración Binaria Compuerta OR produce la función sumadora, esto es, la salida es 1 si la entrada A o la entrada B o ambas entradas son 1; de otra manera, la salida es 0. El sistema binario es un sistema de numeración en el que los números se representan utilizando solamente dos cifras: cero y uno (0 y 1). Es uno de los sistemas que se naturalmente se utilizan en la electrónica y la computación, debido a que estas trabajan internamente con dos niveles de voltaje (encendido 1, apagado 0). Bit (digito binario) es la unidad de información más básica de este sistema de numeración. Para un sistema de numeración binaria de 𝑛 bits se pueden diferenciar hasta 2𝑛 combinaciones distintas. Por ejemplo si se tienen 4 bits se tendrán 24 = 16 números que se pueden diferenciar entre sí, basta asignarles un código a cada uno. Compuerta NOT el circuito NOT es un inversor que invierte el nivel lógico de una señal binaria. Decimal 0 Binario 0000 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 Se toman los ‘1’ de la tabla y se trasladan a la posición correspondiente en el mapa. Se agrupan en grupos de 2𝑛 , es decir, en conjuntos de 1, 2, 4, 8, etc Se tratan de juntar la mayor cantidad de bits ‘1’ para reducir la función resultante. Compuertas Lógicas con Transistores. Al tener conocimiento de las 3 regiones de operación de un transistor BJT, se aprovecha las regiones de corte y saturación, donde el comportamiento del transistor es idealizado como un switch donde deja pasar o no. Mapas de Karnaugh Los mapas de Karnaugh reducen la necesidad de hacer cálculos extensos para la simplificación de expresiones booleanas, aprovechando la capacidad del cerebro humano para el reconocimiento de patrones y otras formas de expresión analítica, permitiendo así identificar y eliminar condiciones muy inmensas. Para un mapa de Karnaugh de 2 variables se tendrá por lo tanto 2 entradas (2 bits) y N salidas deseadas Entradas MSB LSB B A 0 0 0 1 1 0 1 1 Salidas x 1 1 0 0 y 0 0 0 1 z 0 0 0 0 Donde A es el bit menos significativo (LSB) y B es el bit más significativo (MSB) y x,y,z son las salidas con los valores deseados. Los valore de la tabla de verdad se trasladan al mapa en las posiciones correspondientes, para un mapa de 2 bits. Reglas: La forma correcta es realizando el diseño del transistor para utilizarlo en esas dos regiones mencionadas, lo cual queda para alguna de la prácticas siguientes. Construcción de Compuertas con Transistores DESCRIPCIÓN Esta práctica consiste en realizar un contador binario a decimal de 2 bits (0 a 3) con transistores, utilizando un display de 7 segmentos. El transistor debe trabajar en la región de corte/saturación. Se utilizará el transistor 2N3904 (NPN), los grupos que posean otros tipos de transistores pueden utilizarlos para reducir costos. El display a utilizar es 7 segmentos ánodo o cátodo común, y todas las compuertas se hacen con transistores. Para generar las combinaciones de las entradas se permite utilizar un contador binario 74161 y un oscilador de onda cuadrada CI555. FORMATO DE ENTREGA Entregar la hoja de calificación que se encuentra al final del documento y todo lo que se le solicita engrapado. Entregar el circuito en Protoboard, se puede adelantar fuera del Laboratorio. Realizar el diagrama esquemático y de placa (la entrega es en protoboard ¡no en placa!) del circuito completo de la placa, pero se debe utilizar un software de diseño profesional: Eagle, KiCad o Proteus. Imprimir cada uno a una escala adecuada. Debe desarmar el circuito frente al auxiliar. UNIVERSIDAD SAN CARLOS DE GUATEMALA FACULTAD DE INGENIERIA ESCUELA MECANICA ELECTRICA LABORATORIO DE ELECTRONICA ELECTRONICA 1 SEGUNDO SEMESTRE 2016 AUXILIAR: RODRIGO DE LEON #GRUPO:____________ DÍA:______________ HORA:____________ Práctica 1: Hoja de Calificación Nombres Completos Carnet Asistencia Si / No Si / No Si / No Numero de transistores utilizados: Para uso exclusivo del Auxiliar HORA QUE ENTREGÓ Nombre de auxiliar que recibe la práctica, firma y sello. USO EXCLUSIVO AUXILIAR DEL CURSO Desarmó el circuito frente al auxiliar Si / No Nota Estudiante 1 /100 Nota Estudiante 2 /100 Nota Estudiante 3 /100 Debe de adjuntar lo siguiente a la hoja de calificación -Diseño Esquemático -Diseño de Placa -Debe completar todos los segmentos y adjuntarlos a la hoja de calificación. Circuito del contador binario Las salidas del circuito A y B, son las entradas de las compuertas con transistores. Hay 2 tipos de display 7 segmentos, ánodo común y cátodo común. La diferencia radica en que el pin común del display ánodo se conecta a Vcc, en cambio el display de cátodo común se conecta a referencia (GND). Por lo tanto para ánodo común los segmentos a,b,c,…,g se encienden al tener potencial de referencia (GND). Para cátodo común los segmentos a,b,c,…,g se encienden al conectarlos al potencial Vcc. Para esta práctica se tomará la convención que los ‘1’ lógicos (Vcc) encienden los segmentos y ‘0’ lógicos apagan los segmentos. Si se utiliza cátodo común, se conectan las salidas de las compuertas de los segmentos a los display directamente. Si se utilizan ánodo común, se debe de negar la salida de las compuertas de cada segmento al display. Tabla de verdad Display 7 Segmentos No. 0 1 2 3 B 0 0 1 1 A 0 1 0 1 a 1 0 1 1 b 1 1 1 1 c 1 1 0 1 d 1 0 1 1 e 1 0 1 0 f 1 0 0 0 Segmento a B\A 0 1 0 1 0 1 1 1 𝑎 = 𝐴′ + 𝐵 Segmento b B\A 0 1 0 1 1 1 1 1 𝑏 = 1 (𝑣𝑐𝑐) g 0 0 1 1 Segmento c B\A 0 1 0 1 1 1 0 1 𝑐 = 𝐴 + 𝐵′ Y así sucesivamente pare el resto de segmentos. Debe completar todos los segmentos y adjuntarlos a la hoja de calificación.