Document

Anuncio

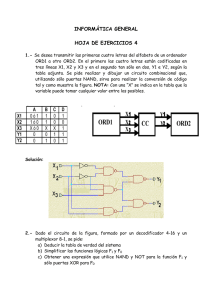

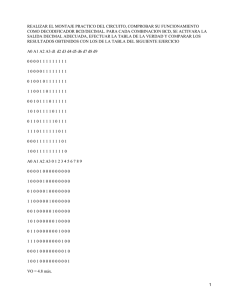

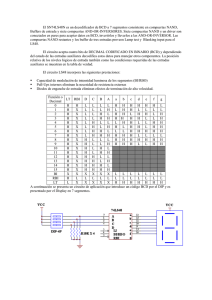

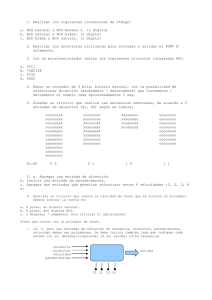

EIE 446 - SISTEMAS DIGITALES Tema 6: Funciones de la lógica combinacional Nombre del curso: “Sistemas Digitales” Nombre del docente: Héctor Vargas OBJETIVOS DE LA UNIDAD ● Distinguir entre semi-sumadores y sumadores completos. ● Utilizar sumadores completos para implementar sumadores en paralelo binarios de múltiples bits. ● Utilizar comparadores de magnitud para determinar la relación entre dos números binarios. Utilizar comparadores en cascada para realizar comparaciones de números más grandes. ● Estudiar la función de un decodificador binario. Específicamente, veremos decodificadores BCD a 7 segmentos. También estudiaremos la función inversa de codificación. ● Estudiar los multiplexores para la selección de datos. También se estudiará la función inversa de demultiplexación. ● Se estudiarán las funciones de generación y comprobación de paridad. EL SEMI-SUMADOR ● El semi-sumador realiza las reglas básicas de la adición binaria, que admite dos entradas binarias (A y B) y genera dos salidas binarias (Acarreo y Suma). ● Las entradas y salidas se pueden resumir en una tabla de verdad. ● El símbolo lógico y circuito equivalente son: A S S S A B Cout B Cout Inputs Outputs A 0 0 1 1 B 0 1 0 1 Cout 0 0 0 1 S 0 1 1 0 EL SUMADOR COMPLETO Inputs ● Un sumador completo tiene tres entradas binarias (A, B, y Acarreo de entrada) y dos salidas binarias (Acarreo de salida y Suma). La tabla de verdad resume la operación. A 0 0 0 0 1 1 1 1 ● Un sumador completo puede ser construido con dos semi-sumadores como se muestra a continuación: A A B B S S A Cout B S S Suma S Cout A B Cin Cin Cout S Cout Símbolo B 0 0 1 1 0 0 1 1 Outputs Cin 0 1 0 1 0 1 0 1 Cout 0 0 0 1 0 1 1 1 S 0 1 1 0 1 0 0 1 EL SUMADOR COMPLETO 1 A Para las entradas dadas, determinar 0 las salidas finales e intermedias de el sumador completo. B S S 1 A Cout 0 B S S 0 Cout 1 1 El primer semi-sumador tiene entradas 1 y 0; por lo tanto la Suma =1 y el Acarreo de salida es igual a 0. El segundo semi-sumador tiene entradas 1 y 1; por lo tanto la Suma = 0 y el Acarreo de salida es igual a 1. La puerta OR tiene entradas 1 y 0, por lo tanto, el acarreo final de salida es igual a 1. Suma Cout 1 EL SUMADOR COMPLETO ● Observe que el resultado del ejemplo previo se puede leer directamente desde la tabla de verdad para un sumador completo. Inputs A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 Outputs Cin 0 1 0 1 0 1 0 1 Cout 0 0 0 1 0 1 1 1 S 0 1 1 0 1 0 0 1 1 A 0 B 1 S S 1 A Cout 0 B S S 0 Cout 1 Suma Cout 1 SUMADORES EN PARALELO ● Los sumadores completos se pueden combinar en paralelo para sumar números binarios con múltiples bits. Un sumador de 4-bit se ilustra a continuación. A4 B4 A3 B 3 A 2 B2 A1 B1 C0 A B Cin Cout S C4 S4 A B Cin Cout C3 S S3 A B Cin Cout C2 S S2 A B Cin Cout C1 S S1 ● El acarreo de salida (C4) no está listo hasta que se propaga a través de todos los sumadores completos. Esto se denomina propagación de acarreo, retardando el proceso de suma. SUMADORES EN PARALELO ● El símbolo lógico para un sumador paralelo de 4-bit se ilustra en la figura. Este sumador de 4-bit incluye un acarreo de entrada (etiquetado como C0) y un acarreo de salida (etiquetado como C4). Número binario A 1 2 3 4 Número binario B 1 2 3 4 Acarreo entrada C0 S 1 2 3 4 C4 4-bit suma Acarreo salida ● El 74LS283 es un ejemplo C.I. Se caracteriza por incluir acarreo anticipado, que agrega lógica para minimizar el retardo de acarreo de salida. Para el 74LS283, el retardo máximo para el acarreo de salida es 17 ns. COMPARADORES ● La función de un comparador es “comparar” las magnitudes de dos números binarios para determinar la relación existente entre ellos. En su forma más simple, un comparador puede comprobar la igualdad usando puertas XNOR. ¿Como podrías comprobar la igualdad de dos números de 4-bit? Multiplicando (AND) las salidas de cuatro puertas XNOR. A1 B1 A2 B2 A3 B3 A4 B4 Salida COMPARADORES ● Los comparadores MSI ofrecen salidas para indicar cual de los números es más grande o si son iguales. Los bits se enumeran empezando en 0, en vez de 1 como en el caso de los sumadores. Igualmente se ofrecen entradas en cascada para expandir el comparador a números más grandes. A0 A1 A2 A3 Entradas cascada B0 B1 B2 B3 0 COMP A 3 A>B A>B A=B A=B A<B A<B 0 A 3 Salidas MSI de 4-bit 74LS85. COMPARADORES ● Los comparadores se pueden expandir usando las entradas en cascada como se muestra en la imagen inferior. El comparador de orden más bajo tiene un nivel lógico ALTO (+5v) en la entrada A = B. LSBs A0 A1 A2 A3 +5.0 V B0 B1 B2 B3 MSBs 0 COMP A 3 A>B A>B A=B A=B A<B A<B 0 A 3 A4 A5 A6 A7 B4 B5 B6 B7 0 COMP A 3 A>B A>B A=B A=B A<B A<B 0 A 3 Salidas DECODIFICADORES ● Un decodificador es un circuito lógico que detecta la presencia de una combinación específica de bits en su entrada. ● Dos decodificadores simples que detectan la presencia del código binario 0011 se muestra en la figura de abajo. El primero tiene una salida activa en nivel alto “HIGH”; el segundo tiene una salida activa en nivel bajo “LOW”. A0 A1 A0 X A1 X A2 A2 A3 A3 Decodificador activo con nivel alto para 0011 Decodificador activo con nivel bajo para 0011 DECODIFICADORES Asuma que la salida del decodificador es un 1 lógico. ¿Cuáles son las entradas al decodificador? A0 = 0 A1 = 1 1 A2 = 0 A3 = 1 DECODIFICADORES ● Los decodificadores MSI tienen múltiples salidas para decodificar cualquier combinación de entradas. Por ejemplo, el decodificador binario-a-decimal que se muestra aquí tiene 16 salidas – una para cada combinación de entradas binarias. Bin/Dec Para las entradas mostradas ¿Cuál es la salida? 1 4-bit binary input 1 0 1 A0 A1 A2 A3 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 Decimal outputs DECODIFICADORES ● Un decodificador MSI específico es el 74HC154 (decodificador 4 a 16). Incluye dos entradas de selección las cuales deben estar activas para habilitar las salidas (se activan con un nivel bajo en ambas entradas). Estas líneas pueden ser utilizadas para expandir el decodificador para entradas más grandes. X/Y A0 A1 A2 A3 CS1 CS2 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 1 2 4 8 & 15 EN 74HC154 DECODIFICADORES ● Los decodificadores BCD-a-Decimal aceptan una entrada decimal codificada en BCD y activan uno de diez posibles indicadores de dígito decimal. Asuma que las entradas al decodificador 74HC42 son la secuencia 0101, 0110, 0011, y 0010. Describa la salida. BCD/DEC (15) A0 A1 (14) A2 (13) (12) A3 0 1 2 3 4 5 6 7 8 9 1 2 4 8 74HC42 Todas las líneas están en nivel alto (HIGH) excepto la salida que está activa, que está en bajo (LOW). Las salidas activas son 5, 6, 3, y 2 en ese orden. (1) (2) (3) (4) (5) (6) (7) (9) (10) (11) DECODIFICADOR BCD A 7 SEGMENTOS ● Otro decodificador útil es el 74LS47. Este realiza la decodificación BCD a display de siete segmentos con salidas activas a nivel bajo (LOW). VCC ● Las salidas de a-g están diseñados para corrientes mucho más altas que otros dispositivos. (16) BCD/7-seg BI/RBO Entradas BCD LT RBI (7) (1) (2) (6) (3) (5) a b c d e f g 1 2 4 8 LT RBI 74LS47 (8) GND (4) (13) (12) (11) (10) (9) (15) (14) BI/RBO Salidas a dispositivo de siete segmentos DECODIFICADOR BCD A 7 SEGMENTOS ● Aquí el 74LS47 está conectado a un display de LEDs de siete segmentos. Observe las resistencias que limitan la corriente, requeridas para prevenir la saturación de los LEDs del display. +5.0 V 1.0 kW BCD input 74LS47 16 BCD/7-seg VCC 3 LT a 4 BI/RBO b 5 RBI c 6 A d 2 B e 1 C f g 7 D GND 8 +5.0 V MAN72 R's = 330 W 13 12 11 10 9 15 14 1 13 10 8 7 2 11 3, 9, 14 a b c d e f g DECODIFICADOR BCD A 7 SEGMENTOS ● El MSI 74LS47 permite la supresión de ceros, que no despliega los ceros innecesarios pero mantiene los ceros significativos. La salida BI/RBO está conectada a la entrada RBI del próximo decodificador. 0 0 0 0 0 RBI LT 8 4 2 1 74LS47 0 0 0 0 0 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO g f e d c b a BI/RBO Sin despliegue Sin despliegue 0 0 0 1 1 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO 1 0 0 0 0 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO Dependiendo del tipo de display, se podrían requerir resistores que limiten la corriente. DECODIFICADOR BCD A 7 SEGMENTOS ● Finalmente, la supresión de ceros también elimina los ceros innecesarios a la derecha del punto decimal como ilustra la figura. La entrada RBI está conectada a la salida BI/RBO del siguiente decodificador. 0 1 0 1 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO Punto Decimal 0 1 1 1 RBI LT 0 0 0 0 8 4 2 1 RBI LT 74LS47 0 0 0 0 8 4 2 1 RBI LT 74LS47 8 4 2 1 74LS47 g f e d c b a BI/RBO g f e d c b a BI/RBO g f e d c b a BI/RBO 1 0 0 Sin despliegue Sin despliegue DECODIFICADOR (Ejemplo de aplicación) ● Sistema simplificado de puertos E/S de una computadora. ● Las computadoras se tienen que comunicar con una variedad de dispositivos externos (periféricos). ● Como se aprecia en la figura, se puede utilizar un decodificador para seleccionar el puerto de entrada de E/S determinado del computador. ● En esta arquitectura, cada puerto de E/S está unívocamente determinado por una dirección de puerto. CODIFICADORES ● Un codificador acepta un nivel lógico activo en una de sus entradas y la convierte a una salida codificada, tal como BCD o binaria. ● El codificador decimal a BCD es un codificador con una entrada para cada uno de los diez dígitos decimales y cuatro salidas que representan el código BCD para el dígito activo. ● A la derecha se muestra el diagrama lógico básico. ● No hay una entrada cero porque las salidas estarán todas a nivel bajo cuando la entrada es cero. 1 A0 2 3 4 5 6 7 8 9 A1 A2 A3 CODIFICADORES Mostrar como el codificador decimal a BCD convierte el número decimal 3 en un código BCD 0011. Las dos puertas OR superiores tienen un uno como se indica con las líneas rojas. De esta manera la salida es 0011. 1 0 1 2 0 1 3 1 4 5 6 7 8 9 0 0 0 0 0 0 0 0 A0 A1 A2 A3 CODIFICADORES ● El 74HC147 es un ejemplo de C.I. de un codificador. Tiene diez entradas activas en BAJO y convierte la entrada activa a una salida BCD activa en BAJO. VCC ● Este dispositivo ofrece mayor flexibilidad ya que es un codificador con prioridad. Esto quiere decir que si hay más de una entrada activa, aquella con el dígito decimal de mayor orden estará activa. La próxima diapositiva muestra una aplicación … (16) Entrada decimal (11) (12) (13) (1) (2) (3) (4) (5) (10) HPRI/BCD 1 2 3 4 5 6 7 8 9 74HC147 1 2 4 8 (8) GND (9) (7) (6) (14) Salida BCD CODIFICADORES VCC R7 7 R8 8 R9 9 HPRI/BCD Codificador de teclado R4 4 R5 5 R1 1 0 6 R2 2 R0 R6 R3 1 2 3 4 5 6 7 8 9 1 2 4 8 BCD complement of key press 74HC147 3 La línea cero no es necesitada por el codificador, pero podría ser utilizada por otros circuitos para detectar una tecla presionada. CONVERTIDORES DE CÓDIGO ● Hay varios convertidores de código que cambian un código a otro. Dos ejemplos son los convertidores Binario-a-Gray y el convertidor Gray-aBinario de cuatro bits. Mostrar la conversión de binario 0111 a código Gray y vice versa. 0 1 0 1 0 1 1 0 0 Binario-a-Gray 1 LSB LSB MSB 0 1 1 1 0 0 Gray-a-Binario ● Estudiar conversión Binario-a-BCD y BCD-a-Binario. MSB MULTIPLEXORES ● Un multiplexor selecciona una línea de datos desde dos o más líneas de entrada y encamina los datos de la línea seleccionada a la salida. En particular, la línea de datos que se selecciona es determinada por las entradas de selección. Dos líneas de selección se muestran para escoger cualquiera de las cuatro entradas de datos. Que línea de datos se selecciona si S1S0 = 10? D2 Entradas de S0 selección S1 D0 Entradas D1 de datos D2 D3 0 1 MUX 0 1 0 1 2 3 Salida de datos DEMULTIPLEXORES ● Un demultiplexor (DEMUX) realiza la función opuesta de un MUX. Conmuta los datos desde una línea de entrada a dos o más líneas de salida dependiendo de las entradas seleccionadas. ● El C.I. 74LS138 puede funcionar tanto como un decodificador o como un demultiplexor. Cuando se conecta como un DEMUX, los datos se aplican a una de las entradas habilitadas, y luego son encaminados a la línea de salida seleccionada dependiendo del valor en las líneas de selección. Observe que las salidas están activas en BAJO como se ilustra en el siguiente ejemplo… DEMUX Líneas de selección Entradas habilitadas A0 A1 A2 G1 G2A G2B Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 74LS138 Salidas de datos DEMULTIPLEXORES Determinar las salidas, dadas las entradas mostradas. DEMUX Líneas de selección de datos Entradas habilitadas A0 A1 A2 G1 G2A G2B Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 74LS138 Salidas de datos A0 A1 A2 G1 G2A BAJO G2B BAJO Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 GENERADORES DE PARIDAD Y COMPROBADORES ● Paridad es un método de detección de errores que utiliza un bit extra asociado a un grupo de bits para forzarlos a ser par o impar. En paridad par, el número total de unos debe ser par; en paridad impar el número total de unos debe ser impar. La letra ASCII “S” es 1010011. Mostrar el bit de paridad para la letra “S” con paridad par e impar. S con paridad impar = S con paridad par 11010011 = 01010011 GENERADORES DE PARIDAD Y COMPROBADORES ● El C.I. 74LS280 se puede utilizar para generar un bit de paridad o para comprobar un flujo de datos de entrada para paridad par o impar. ● Comprobador: El C.I. 74LS280 puede examinar códigos de hasta 9 bits. La salida par será normalmente ALTA si la línea de datos tiene paridad par; por el contrario, será un nivel lógico BAJO. Igualmente, la salida impar será ALTA si la línea de datos tiene paridad impar; en otro caso, será un nivel lógico BAJO. ● Generador: Para generar paridad par, el bit de paridad se toma desde la salida de paridad impar. Para generar paridad impar, la salida se toma desde la salida de paridad par. Data inputs (8) (9) (10) (11) (12) (13) (1) (2) (4) A B C D E F G H I 74LS280 (5) (6) S Even S Odd ● Ejercicio 1: Describir con palabras el funcionamiento del circuito. Demux ● Ejercicio 2: Interpretar la utilidad del sistema que se muestra en la figura. ● Ejercicio 3: Diseñar un codificador de prioridad de cuatro entradas activas en el nivel bajo. Añada una salida que indique cuando no hay ninguna entrada activa. ● Ejercicio 3: Continuación de la solución... PALABRAS CLAVES DE LA UNIDAD Sumador Un circuito digital que suma dos bits y un bit de entrada completo de acarreo para producir una suma y un acarreo de salida. Cascada Conectar dos o más dispositivos similares de manera de expandir la capacidad de los dispositivos individuales. Propagación de Un método de suma binaria en que el acarreo de salida acarreo de cada sumador se convierte en el acarreo de entrada del sumador de orden superior. Acarreo Un método de suma binaria por el cual los acarreos del anticipado sumador previo son anticipados, de esta manera se eliminan los retardos de propagación de acarreo. PALABRAS CLAVES DE LA UNIDAD Decodificador Un circuito digital que convierte información codificada en una forma familiar no codificada. Codificador Un circuito digital que convierte información familiar en una forma codificada. Codificador Un codificador en el que solamente el dígito de entrada con prioridad de orden superior es codificado y cualquier otra entrada activa es ignorada. Un circuito que conmuta datos digitales de varias líneas Multiplexor de entrada en una única línea de salida en una secuencia (MUX) de tiempo especificada. Un circuito que conmuta datos digitales de una línea de Demultiplexor entrada a varias líneas de salida en una secuencia de (DEMUX) tiempo especificada. BIBLIOGRAFÍA Libro base: “Fundamentos de Sistemas Digitales”. Autor: Tomas L. Floyd. Libro complemento: “Principios de Diseño Digital”. Autor: Daniel D. Gaski.