5.3. Neurocomputadores

Anuncio

AAC

TEMA 5: OTRAS ARQUITECTURAS.

NEUROCOMPUTADORES

1

5.1. Introducción a los sistemas neuronales

Cuestión : ¿Por qué existen tareas que las

máquinas no han logrado resolver con eficacia, a

pesar del espectacular desarrollo tecnológico?

Arquitectura de Von Neumann: máquinas

simbólicas

Neurocomputación y sistemas borrosos: forman

parte de la IA; pretenden incorporar cierto tipo de

inteligencia en sistemas de procesamiento y control

AAC

2

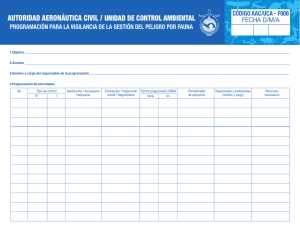

5.1. Introducción a los sistemas neuronales

Cerebro frente a computador convencional

Cerebro

Computador

10-2 s (100 Hz)

10-9 s (1 GHz)

Estilo de procesamiento

Paralelo

Secuencial

Número de procesadores

1011 – 1014

Pocos

104 por procesador

Pocas

Distribuido

Direcciones fijas

Amplia

Muy escasa

Autoorganizado

Centralizado

10-16 J

10-6 J

Velocidad de proceso

Conexiones

Almacenamiento del conocimiento

Tolerancia a fallos

Tipo de control del proceso

Eficiencia energética

La neurona: un procesador sencillo, lento y poco fiable

La potencia de cálculo reside en la cohabitación de

millones de ellas, sus interconexiones y su

procesamiento en paralelo.

AAC

3

5.1. Introducción a los sistemas neuronales

Sistemas neuronales artificiales (ANS): réplicas

aproximadas de la estructura hardware del cerebro.

No se pretende crear un cerebro artificial.

El objetivo es mejorar el rendimiento en tareas

propias de organismos biológicos: percepción,

reconocimiento de formas, control, etc.

Área multidisciplinar: Electrónica, Física,

Matemáticas, Biología, etc.

Excelentes resultados en ciertos ámbitos.

AAC

4

5.1. Introducción a los sistemas neuronales

Modelo biológico

Dendritas

Sinapsis

Axón

(100 µm–1 m)

Soma

(10-80 µm)

Núcleo

Presináptica

Postsináptica

Una neurona se activa si la influencia combinada de

sus entradas supera cierto umbral (hay sinapsis

potenciadoras y otras inhibidoras).

Las conexiones sinápticas poseen cierta plasticidad

(la influencia de las sinapsis varía y se crean otras);

esto es la base del aprendizaje y la memorización.

AAC

5

5.2. Sistemas neuronales artificiales

Estructura jerárquica de un ANS:

Σ

Capa

Red

Sistema neuronal

Σ

Σ

Salidas

Entradas

Neurona

Σ

Parte algorítmica

Σ

AAC

6

5.2. Sistemas neuronales artificiales

Modelo estándar de neurona artificial:

x2

x1

Entradas xj(t)

wi2

.

.

.

xj

Neurona i

wi1

wij

Σ

.

. win

.

xn

f()

θi

-1

yi(t) = fi(∑ wijx j − θ j )

j

yi

Pesos sinápticos wij

Regla de propagación hi(t) = σ(wij , xj(t))

Función de activación (filtro) yi(t) = fi [ hi(t) ]

Umbral = θi : nível mínimo de disparo de la neurona (todo-nada)

n

Si hacemos wi0 = θi , x0 = -1, entonces

yi(t) = fi(∑ wijx j )

j= 0

Peso sináptico negativo: conexión inhibidora; positivos: conexión excitadora

Capa de entrada (sensorial): capa de neuronas que no poseen sinapsis de entrada

Capa de salida: capa de neuronas que no poseen sinapsis de salida

Capa oculta: capa que posee neuronas que no son de entrada ni de salida (mayor riqueza)

Pueden existir conexiones intercapa e intracapa (o laterales)

AAC

7

5.2. Sistemas neuronales artificiales

Diferentes tipos de arquitecturas neuronales:

Redes monocapa y multicapa (layered).

Redes unidireccionales (feedforward) y recurrentes(feedback)

Redes autoasociativas (A + ruido ⇒ A) y heteroasociativas (A ⇒ B)

Funciones de activación habituales:

Identidad

Escalón

(Heaviside)

Lineal a tramos

Función

Rango

y=x

[-∞,+∞]

y=signo(x)

y=H(x)

{-1, +1}

{0, +1}

, si x < - L

⎧ -1

⎪

y = ⎨ x , si - L ≤ x ≤ L

⎪ + 1 + 1, si x > L

⎩

AAC

[-1,+1]

Gráfica

-L

L

8

5.2. Sistemas neuronales artificiales

Funciones de activación habituales:

Sigmoidea

Función

Rango

1

1 + e −x

[0,+1]

ex + e −x

y = x −x

e -e

[-1,+1]

y=

2

Gaussiana

y=A e-Bx

Sinusoidal

y=A sen(ωx+ϕ)

Gráfica

y = Ae −Bx

2

[0,+1]

AAC

[-1,+1]

9

5.2. Sistemas neuronales artificiales

Aprendizaje (entrenamiento): proceso, generalmente iterativo,

que consigue el ajuste de los parámetros libres de la red

neuronal, a partir de la estimulación por el entorno.

Se sigue una regla de aprendizaje basada en la optimización de

una función de error o coste

Niveles de aprendizaje:

1. Modelado de las sinapsis: ∆wij (t+1) = wij (t) +∆wij (t)

2. Creación/destrucción de neuronas.

Tipos de aprendizaje (I):

1. Supervisado. Se proporciona a la red una serie de patrones junto

con la salida deseada u objetivo; la red ajusta iterativamente los

pesos hasta que su salida tiende a la deseada (estimación de

relaciones entrada-salida).

2. No supervisado. Se proporciona a la red una serie de patrones sin

adjuntar la respuesta deseada; la red estima regularidades en el

conjunto de entradas, extrae rasgos comunes o agrupa patrones.

AAC

10

5.2. Sistemas neuronales artificiales

Aprendizaje

Tipos de aprendizaje (II):

3. Híbrido. Coexisten los tipos anteriores, normalmente en distintas

capas (Ejemplo: redes de contra-propagación).

4. Reforzado. La salida deseada simplemente es un índice global del

rendimiento de la red.

Recuerdo (ejecución): Una vez que el sistema ha sido

entrenado, sus pesos y su estructura han quedado definidos,

por lo que la red está preparada para procesar datos.

AAC

11

5.2. Sistemas neuronales artificiales

Redes supervisadas: El Perceptrón

Modelo unidireccional, con una capa sensorial de n neuronas y

otra de salida con m neuronas.

n

yi(t) = fi(∑ wijx j - θi ), ∀i, 1 ≤ i ≤ m

j=1

Las neuronas de entrada sólo envían información ({0, +1}) a las

de salida.

La función de activación es de tipo escalón

n

yi = H(∑ wijx j - θi ), ∀i, 1 ≤ i ≤ m

j=1

Una neurona tipo perceptrón permite discriminar entre dos clases

linealmente separables.

y = H(w1x1 + w2x2 - θ)

⎧1 , si w1x1 + w2x2 ≥ θ

y=⎨

⎩0 , si w1x1 + w2x2 < θ

AAC

12

5.2. Sistemas neuronales artificiales

Redes supervisadas: El Perceptrón

Una neurona tipo perceptrón permite discriminar entre dos clases

linealmente separables.

⎧1 , si w1x1 + w2x2 ≥ θ

y=⎨

⎩0 , si w1x1 + w2x2 < θ

w1x1 + w2x2 - θ = 0 ⇒ x2 =

− w1

θ

x1 +

w2

w2

Ejemplo: Si w1 = w2 = -2, θ = -3, la función implementada es la

NAND.

Problema: Un simple perceptrón no puede representar funciones

no separables linealmente (XOR).

x2

x2

<θ

≥ θ (0 NAND)

<θ

<θ

x1

(1,0)

(1,1)

(0,0)

(0,1)

x1

AAC

13

5.2. Sistemas neuronales artificiales

Redes supervisadas: El Perceptrón

Algoritmo de aprendizaje por corrección de errores: los pesos se

ajustan en proporción a la diferencia entre la salida actual de la

red y la salida deseada.

Se basa en la regla de Hebb: “Cuando un axón presináptico causa la

activación de cierta neurona postsináptica, la eficacia de la sinapsis

que las relaciona se refuerza”.

∆wij = ε yi xj

ε = ritmo de aprendizaje ∈ (0, 1)

Conjunto p de patrones xµ, µ = 1, ..., p y salidas deseadas tµ

Entradas y salidas discretas {-1, 1} (ó {0, 1}).

∆wij (t) = εwij (t µi - y µi) x µj = εwij δ x µj

AAC

14

5.2. Sistemas neuronales artificiales

Redes supervisadas: La Adalina

Adaline = Adaptive Linear Neuron

Similar el perceptrón pero de activación lineal; las entradas

pueden ser continuas.

n

yi(t) = ∑ wijx j - θi , ∀i, 1 ≤ i ≤ m

j=1

Utiliza la regla de Widrow-Hoff (o LMS –Least Mean Square).

Las actualizaciones de los pesos son continuas (discretas en el

perceptrón)

La regla LMS se acerca asintóticamente a la solución (número

finito de iteraciones en el perceptrón).

Se utiliza como filtro adaptativo para cancelar ruido en la

transmisión de señales (satélite).

Madalina (Madaline = Many adalines): versión multicapa de la

adalina.

AAC

15

5.2. Sistemas neuronales artificiales

El Perceptrón multicapa (MLP = Multi-Layer Perceptron)

Surge al añadir capas ocultas a un perceptrón simple.

Entradas a la red = xi ; salidas de la capa oculta = yi ; salidas de

la capa final = zk ; salidas objetivo = tk

zk = ∑ w'kj f (∑ w jix j - θ j ) - θ'k

j

i

La función de activación es de tipo

sigmoideo

θ’k

Se entrena mediante el algoritmo

denominado Back Propagation (BP)

w’kj

w

ji

θj

o retropropagación de errores

La idea del algoritmo es determinar cuál es la contribución de

cada neurona al error global, y propagar dicho error hacia atrás

actualizando los pesos entre las distintas capas de neuronas.

Un MLP con una única capa oculta es un aproximador universal de

funciones.

AAC

16

5.2. Sistemas neuronales artificiales

El Perceptrón multicapa (MLP = Multi-Layer Perceptron)

Aproximación al algoritmo de retropropagación:

Inicializar pesos de la red

Mientras no_parar hacer

Para cada patrón de entrenamiento p hacer

Para cada neurona de capa c en [2ª_capa .. última_capa]

net i (t) =

w jix j , ∀i, i ∈ B

∑

j ∈A

yi = f(neti)

Para cada neurona de última_capa hacer

δi = (ti - yi) f ’(neti)

Para cada neurona j de capa c en [última_capa - 1 .. 1ª_capa]

δj = f’(netj)

Σ δiwji

Para cada neurona i de capa c+1

wji = wji + ε δi yj

FinPara

FinMientras

AAC

17

5.2. Sistemas neuronales artificiales

Redes neuronales no supervisadas

Se proporciona a la red una serie de patrones sin adjuntar la

respuesta deseada; la red estima regularidades en el conjunto de

entradas, extrae rasgos comunes o agrupa patrones.

Por tanto, las neuronas han de ser capaces de autoorganizarse.

En general, son redes competitivas, en las que sólo una neurona

o un grupo de vecinas consiguen activarse. La neurona más

activa logrará inhibir a las demás (se les llama también redes

WTA – Winner Takes All).

La representación de la información

en la corteza cerebral aparece con

frecuencia organizada espacialmente

(área somato-sensorial, mapas

tonotópicos para los sonidos, etc.).

AAC

18

5.2. Sistemas neuronales artificiales

Redes no supervisadas: Mapas Autoorganizados (SOM)

Las neuronas se organizan de forma unidireccional de dos capas:

Capa sensorial: m neuronas, una por cada entrada; cada neurona

se etiqueta con un índice k (1 ≤ k ≤ m).

La segunda capa realiza el procesamiento; consiste en general en

una estructura rectangular (a veces, uni- o tridimensional) de

nxx ny neuronas que operan en paralelo. Cada neurona se

etiqueta con un par de índices i = (i, j) (1 ≤ i ≤ nx , 1 ≤ j ≤ ny) que

determina su localización espacial.

Cada neurona k está conectada a cada neurona (i, j) con el peso

sináptico wijk

Neurona (i,j)

Las entradas son muestras del

espacio sensorial, x(t) ∈ ℜm .

wijk

x(t)

AAC

Neurona k

19

5.2. Sistemas neuronales artificiales

Redes no supervisadas: Mapas Autoorganizados (SOM)

Cada neurona posee un vector de pesos o referencia wij(t) ∈ ℜm .

En el modo normal, se calcula la similitud entre el vector de

entradas x y el vector de referencia wij de cada neurona,

declarando ganadora aquella que proporcione la mayor similitud.

Dicha neurona indica el tipo de rasgo o patrón detectado.

En el modo de aprendizaje, la neurona vencedora modifica sus

pesos para que se asemejen más a x(t).

Además, existe una función de vecindad h(), de modo que las

neuronas en el entorno alrededor de la ganadora también

actualizan sus pesos.

Sombrero mejicano

Pipa

Gaussiana

AAC

Rectangular

20

5.2. Sistemas neuronales artificiales

Redes no supervisadas: Mapas Autoorganizados (SOM)

Aproximación al algoritmo de entrenamiento:

Inicializar pesos sinápticos

Mientras no_parar hacer

Para cada patrón de entrenamiento x(t) hacer

Para cada neuronan i=(i, j) calcular distancia en paralelo:

d2 (w ij , x) = ∑ (wijk - xk )2

k =1

FinPara

Determinar neurona ganadora g con menor distancia

Actualizar pesos de g y de sus vecinas

wijk(t+1) = wijk(t) + α(t)·h(|i-g|, t)·(xk(t) - wijk(t))

FinPara

FinMientras

El radio de vecindad y el ritmo de aprendizaje

α(t) son monótonos decrecientes con t.

AAC

21

5.2. Sistemas neuronales artificiales

Redes no supervisadas: Mapas Autoorganizados (SOM)

Variantes de los SOM:

Mapas de Fritzke y Growing Neural Gas: se empieza con un

mapa de tamaño pequeño y se van añadiendo neuronas a

medida que avanza el entrenamiento.

Red de contrapropagación: modelo híbrido con tras capas

(sensorial, oculta no supervisada y supervisada de salida).

LVQ (Learning Vector Quantization): modelo supervisado con

una capa de neuronas tipo SOM, sin vecindad; se premia las

neuronas que clasifican correctamente un determinado patrón

(aumentar peso) y castigar en sentido contrario (disminuir).

Aplicaciones de los SOM: Reconocimiento

del habla; control de robots; monitorización

de procesos industriales; ayuda al diseño de

circuitos integrados; reconocimiento de

patrones financieros, etc.

AAC

22

5.2. Sistemas neuronales artificiales

Redes no supervisadas: Mapas Autoorganizados (SOM)

Ejemplos gráficos:

Mapa fonético del finés

AAC

Mapa semántico

23

5.2. Sistemas neuronales artificiales

Otros tipos de redes

Red de Hopfield.

Se trata de una red realimentada, no supervisada, con una única

capa de neuronas y conectividad total entre ellas.

y1

…

x1

yn

yi

xi

…

xn

Funciona como memoria asociativa que puede almacenar patrones

internamente para reconstruirlos si se presentan incompletos o con

ruido. Las entradas y salidas son binarias ({0, 1} ó {-1, +1})

Supervisadas: Máquina de Boltzmann, BSB (Brain State in a Box),

etc.

No supervisadas: ART 1, 2, 3 (Adaptive Resonance Theory), BAM

(Bidirectional Associative Memory), Neocognitrón, etc.

AAC

24

5.3. Neurocomputadores

Soportes para la realización de redes neuronales:

Simulación software. Económica pero de bajo rendimiento.

Emulación hardware. Sistemas expresamente diseñados para

emular ANS (basados en RISC, DSP, etc.): neuroaceleradores o

neurocomputadores de propósito general.

Implementación hardware. Realización física de la red neuronal:

neurocomputadores de propósito específico. Basados en FPGA o

mediante integración microelectrónica (ASIC llamados chips

neuronales).

Neurocomputadores

Neurochips

Chips estándar

Secuencial

+ acelerador

Multiprocesador

Digitales

AAC

Híbridos

Analógicos

1

5.3. Neurocomputadores

Aspectos del soporte hardware:

El sistema debe soportar un gran número de conexiones y un

flujo elevado de transmisión de datos.

Principalmente se utiliza tecnología electrónica; se comienza a

experimentar con tecnologías optoelectrónicas y bioquímicas.

Se realizan ASIC o bien se utilizan FPGA (diferencia en cuanto al

ciclo de desarrollo y a la densidad de puertas) con lenguajes HDL.

Los pesos se almacenan en registros o memorias.

Inconveniente: se debe optimizar la representación de los datos y

el almacenamiento de los pesos, pues una precisión elevada

requeriría un área también muy elevada.

Se estima que el aprendizaje requiere pesos con precisión de 1418 bits mientras que el recuerdo requiere pesos de 6-10 bits.

Ejemplo: L-Neuro 1.0 de Philips usa pesos de 16 bits en el

aprendizaje y de 4 u 8 bits en el recuerdo.

AAC

2

5.3. Neurocomputadores

Aspectos del soporte hardware:

Actualmente, el diseño digital VLSI es el predominante:

Inconveniente: los EP deben disponerse en un área limitada 2D

y se conectan mediante un número limitado de capas.

Ventajas:

Simplicidad.

Alta relación señal-ruido (comparado con analógico).

Circuitos fácilmente escalables (idem).

Flexibilidad.

Coste reducido.

Aplicaciones CAD disponibles.

Fiabilidad.

Sumas fácilmente implementables.

Funciones no lineales implementables

mediante circuitos o tablas.

Elementos de almacenamiento.

Generadores de números aleatorios.

AAC

3

5.3. Neurocomputadores

Aspectos del soporte hardware:

Dificultad en la clasificación de las implementaciones hardware:

Clasificación de Flynn. Muchos neurocomputadores son de tipo

SIMD (arrays sistólicos, arrays de procesadores y procesadores

vectoriales segmentados).

Clasificación “cuántos y cuán complejos” EP:

Moderadamente paralelos (16-256 procesadores).

Altamente paralelos

(256-4096 procesadores).

Masivamente paralelos

(más de 4096 procesadores).

La complejidad del EP se mide en base a la longitud de la palabra.

División en neuroaceleradores y neurocomputadores.

Clasificación basada en 3 criterios:

Evidencia biológica (réplica de un sistema biológico; réplica de un

nivel superior; sin réplica).

Mapeado sobre hardware (orientado a red; orientado a neurona;

orientado a sinapsis).

Tecnología de implementación (digital; analógica; híbrida).

AAC

4

5.3. Neurocomputadores

Aspectos del soporte hardware:

Rendimiento del sistema:

La fase de recuerdo se evalúa en cuanto al número de

conexiones procesadas por segundo (CPS).

La fase de aprendizaje se evalúa en cuanto al número de

conexiones actualizadas por segundo (CUPS).

Son índices globales y muy poco representativos de distintos

tipos de redes.

Miden básicamente el tiempo de una MAC (básica en DSP) sin

otros factores como la transferencia de datos.

Otras unidades:

CPSPW: CPS Por Pesos; normalización de CPS por el número de

pesos de la red.

CPPS: Primitivas de Conexión Por Segundo; se multiplica CPS por

los bits de precisión y por los bits de las entradas.

AAC

5

5.3. Neurocomputadores

Aspectos del soporte hardware:

Tipo de aprendizaje para el caso de redes multicapa:

Off-chip. El aprendizaje se realiza por medio de un computador

con alta precisión, tras el cual los pesos se transfieren al chip.

Éste sólo lleva a cabo la etapa de propagación hacia adelante

(forward) del modo recuerdo.

Chip-in-the-loop. El hardware neuronal se utiliza en el

aprendizaje sólo en la propagación hacia adelante. El recálculo

de los pesos se realiza off-chip, tras el cual se transfieren al chip

tras cada iteración.

On-chip. El aprendizaje se realiza por completo en el propio

chip. El problema es la precisión empleada.

AAC

6

5.3. Neurocomputadores

Emulación hardware: neuroaceleradores.

Utilización de arquitecturas paralelas para trabajar con ANS.

Se trata de diseñar un acelerador o coprocesador dependiente de

un host, construido a partir de micros RISC, DSP, etc.

Se utiliza un software de simulación apropiado para evaluar un

ANS o desarrollar una aplicación práctica compleja.

Permite trabajar prácticamente con cualquier tipo de red.

Se trata de sistemas flexibles, pero que no explotan al máximo la

capacidad de la red neuronal.

La velocidad suele rondar los 10M CPS.

Ejemplos:

SIGMA-1 de SAIC (1989) alcanza 11 MCUPS y 3.1M de EPs

virtuales e interconexiones. El host es un PC.

ANZA Plus de HNC (1989); alcanza 1,8 MCUPS y 6 MCPS, 1M de

EPs virtuales, 1.5M de interconexiones. Un PC actúa como host.

Posee micro y coprocesador PF de Motorola.

AAC

7

5.3. Neurocomputadores

Emulación hardware: neuroaceleradores.

Ejemplos:

Balboa 860 de HNC (1991), basada en el micro Intel i860.

Disponible para PC y para estaciones SUN. Alcanza 25 MCPS y 9

MCUPS.

Serie NT6000 de NT (1993). Pueden conectarse a sistemas E/S

tanto analógicos como digitales. El NT6000st y el -hs usan el PC

como host y están equipados con un DSP TMS320 y un NISP

(Neural Instruction Set Processor); alcanzan 2 MCPS. Los

modelos neuronales implementables son el BP y los Mapas

Autoorganizativos.

NEP de IBM (1987). El Network Emulation Processor es un

entorno de emulación, cuyo hardware es un DSP TMS320,

memoria estática y dinámica e interfaz con el PC; es un sistema

modular de forma que se pueden conectar hasta 256 tarjetas.

Cada NEP simula hasta 2000 EPs virtuales y 16000 conexiones,

con 30-50 CUPS.

AAC

8

5.3. Neurocomputadores

Emulación hardware: neuroaceleradores.

Ejemplos:

NBS de Micro Devices (1990). El Neural Bit Slice MD1220

contiene 8 nodos, cada uno con 15 entradas sinápticas

cableadas, ampliables hasta 256 con hardware adicional. Los

pesos se almacenan externamente, con lo cual el aprendizaje es

off-chip. Se pueden interconectar directamente varias tarjetas,

y todas ellas a su vez al bus de la CPU del PC. Alcanza 10 MCPS.

Neuro Turbo I del Nagoya Institute of Technology (1989).

Contiene 4 DSP y se conecta a un ordenador personal NEC

PC98.

AAC

9

5.3. Neurocomputadores

Neurocomputadores construidos a partir de procesadores de

propósito general:

Nunca alcanzarán la máxima eficiencia, pero son relativamente

baratos y flexibles. Se suelen utilizar DSP o RISC.

Ejemplos:

AAC

Pesos

Registros

Pesos

Registros

Pesos

Registros

Mark III y IV de TRW-HNC (1989). La arquitectura es BBA ó de

bus de difusión (broadcast). El Mark III utiliza 8 micros 68010

de Motorola; implementa 8000 EPs y 480000 conexiones, y

alcanza 380000 CPS.

El Mark IV puede

implementar 262144

ALU

ALU

ALU

EPs, 5.5M conexiones

y alcanza 5 MCPS;

...

incluye DSP de 16 bits

TMS32020.

10

5.3. Neurocomputadores

Neurocomputadores construidos a partir de procesadores de

Memoria de pesos externa

propósito general:

Ejemplos:

Sandy/8 de Fujitsu (1990). Es un

prototipo para un arquitectura

sistólica en array (SSAA –Systolic

Square Array Architecture). Posee

256 DSPs TMS320C30; se estima

que alcanza 13 MCUPS en BP. El

prototipo se conecta a un SUN-3.

GigaConNection (GCN, 1990) de

Sony. Consta de 128 PE basadas

en el Intel i860, en una malla 2D.

Se estima que llega a 1 GCUPS.

BSP400 (1991) de Brain Style

Processor. Utiliza micros MC68701 de 8 bits; la baja velocidad

de éstos hace que sólo se alcance 6.4 MCUPS con 400

procesadores.

AAC

11

5.3. Neurocomputadores

Neurocomputadores construidos a partir de procesadores de

propósito general:

Ejemplos:

Ring Array Processor (RAP, 1990) de ICSI. Consta de 4-40 DSPs

TMS320C30 conectados en anillo a través de PGA de Xilinx.

Cada placa puede conectarse a un host, y puede alcanzar 57

MCPS en la propagación hacia adelante en un perceptrón

multicapa, mientras que en la fase BP llega a 13.2 MCPS.

Multiprocessor System with Intelligent Communication

(MUSIC, 1992), del Swiss

Memoria de pesos externa

Federal Institute of

Technology. Cada placa

consta de 3 DSP 96002 de

Motorola, pudiendo conectar

hasta 21 de ellas. Para un

perceptrón de dos capas se

consigue 817 MCPS y

330 MCUPS.

AAC

FIFO externa

12

5.3. Neurocomputadores

Neurocomputadores construidos a partir de neurochips:

Se diseñan circuitos específicos para implementar las funciones

neuronales.La velocidad aumenta en dos órdenes de magnitud.

Ejemplos:

SYNAPSE-I y SYNAPSE-X (SYnthesis of Neural Algorithms on a

Parallel Systolic Engine, 1990) de Siemens. Es una matriz

sistólica 2x4 de chips MA16; éstos implementan operaciones

típicas de diversos modelos neuronales (producto matriz-vector,

búsqueda de máximo, etc. La configuración estándar consta de

8 MA16, y alcanza

5100 MCPS y

133 MCUPS.

AAC

13

5.3. Neurocomputadores

Neurocomputadores construidos a partir de neurochips:

Ejemplos:

CNAPS (Connected Network of Adaptive Processors, 1991) de

Adaptive Solutions. Es un array 1D SIMD de nodos, conectados

a través de buses broadcast. El chip elemental es el X1, que

soporta aprendizaje on-chip, y 80 de ellos (64 útiles) se

agrupan en el N64000. El sistema estándar consta de 4 chips y

un secuenciador de microcódigo; alcanza 5700 MCPS y 1460

MCUPS. Los autores dicen que es el más veloz y que todos los

modelos neuronales testeados

pudieron ser mapeados.

AAC

14

5.3. Neurocomputadores

Neurocomputadores construidos a partir de neurochips:

Ejemplos:

SNAP (SIMD Neurocomputer Array Processor, 1991) de HNC.

Toma como chip básico el HNC 100 NAP, que consta de 4 células

aritméticas en anillo con aritmética PF IEEE de 32 bits. Cada

placa SNAP consta de 4 chips.

El SNAP-32 posee dos placas

(32 EPs), y puede alcanzar

500 MCPS y 128 MCUPS;

el SNAP-64 posee 4 placas

(64 EPs).

AAC

15

5.3. Neurocomputadores

Neurocomputadores construidos a partir de neurochips:

Ejemplos:

LNeuro 1.0 (Learning Neurochip, 1991) de Philips. El chip

implementa 32 neuronas de entrada y 16 de salida; posee

aprendizaje on-chip. Se pueden conectar modularmente varios

chips. Una configuración con 4 placas y 16 chips alcanza 19

MCPS y 4.2 MCUPS.

Su sucesor es el LNeuro 2.3, que consta de 12 DSP, un

procesador RISC y unidades para proceso escalar y vectorial. El

rendimiento máximo estimado es de 1380 MCUPS y 1925 MCPS.

Puede implementar distintos modelos neuronales: BP, mapas

autoorganizativos, etc.

Mantra I (1991) del Swiss Federal Institute of Technology. Está

construido con chips GENES (Generic Element for NeuroEmulator Systolic arrays) que realizan productos vector-matriz.

La configuración en array de 40x40 chips alcanza 500 MCPS y

160 MCUPS.

AAC

16

5.3. Neurocomputadores

Neurocomputadores construidos a partir de neurochips:

Ejemplos:

WSI (Wafer Scale Integration, 1991) de Hitachi. Un wafer posee

144 neuronas, y 8 de éstos se agrupan para lograr 1152 nodos

que permiten aprendizaje on-chip. Alcanza 2300 MCUPS en red

multicapa con BP.

ZISC (Zero Instruction Set Computer, 1992) de Intel. Posee 36

neuronas con 64 entradas de 8 bits, y permite aprendizaje onchip. Se pueden conectar modularmente varios chips. Están

diseñados especialmente para reconocimiento y clasificación en

tiempo real y a bajo coste.

HANNIBAL (Hardware Architecture for Neural Networks

Implementating Backpropagation Algorithm Learning, 1991) de

British Telecom. Cada chip contiene 8 EP y alcanza 160 MCPS.

AAC

17

5.3. Neurocomputadores

Neurocomputadores a partir de neurochips analógicos:

ETANN (Electrically Trainable Analog Neural Network, 1991) de

Intel. Cada chip contiene 64 neuronas y 10240 sinapsis. Alcanza

2 GCPS, y pueden conectarse

hasta 8 de éstos.

Otros: Mod2, Fully Analog Chip,

etc.

Neurocomputadores híbridos:

ANNA (Analog Neural Network

Arithmetic and logic unit,

1992) de AT&T. Alcanza entre

1000 y 2000 MCPS.

AAC

18

5.4. Aplicaciones de los SNA

Finanzas.

Predicción de índices

Detección de fraudes.

Riesgo crediticio

Predicción de la rentabilidad de acciones

Negocios

Marketing

Venta cruzada

Campañas de venta

Tratamiento de textos y procesamiento de formas

Reconocimiento de caracteres impresos mecánicamente.

Reconocimiento de gráficos.

Reconocimiento de caracteres escritos a mano.

Reconocimiento de escritura manual cursiva.

AAC

19

5.4. Aplicaciones de los SNA

Alimentación

Análisis de olor y aroma.

Perfilamiento de clientes en función de la compra.

Desarrollo de productos.

Control de Calidad.

Energía.

Predicción consumo eléctrico

Distribución recursos hidráulicos para la producción eléctrica

Predicción consumo de gas ciudad

Industria

Control de

Control de

Control de

manufacturera.

procesos.

calidad.

robots.

AAC

20

5.4. Aplicaciones de los SNA

Medicina y salud

Ayuda al diagnostico.

Análisis de Imágenes.

Desarrollo de medicamentos.

Distribución de recursos.

Ciencia e Ingeniería.

Ingeniería Química.

Ingeniería Eléctrica.

Climatología.

Transportes y Comunicaciones

Optimización de rutas.

Optimización en la distribución de recursos

……….

AAC

21