Prácticas de las asignaturas de Electrónica Digital, Estructuras de

Anuncio

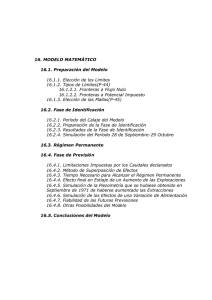

PRÁCTICAS DE LAS ASIGNATURAS DE ELECTRÓNICA DIGITAL, ESTRUCTURA DE COMPUTADORES Y DISEÑO DE SISTEMAS MICROCOMPUTADORES (SÍNTESIS MEDIANTE PLD’S) C. Diego Moreno, F. Javier Quiles, Manuel A. Ortiz, Joaquín Olivares, J. Ignacio Benavides Área de Arquitectura y Tecnología de Computadores. Escuela Politécnica Superior. Universidad de Córdoba el1momoc@uco.es 1. RESUMEN En este trabajo se presentan las prácticas que imparte el área de Arquitectura y Tecnología de Computadores de la Universidad de Córdoba en tres de las asignaturas, relacionadas con el diseño lógico de sistemas digitales, incluidas en la titulación de I.T.I. en la especialidad de Electrónica Industrial. A continuación presentamos de forma resumida en la siguiente tabla las prácticas impartidas en las tres asignaturas: ED.S.1: Puertas básicas ED.S.2: Simplificación de funciones lógicas Simulación ED.S.3: El multiplexor y el decodificador ED.S.4: Circuitos combinacionales aritméticos Electrónica Digital ED.S.5: Circuitos secuenciales ED.L.1: Universalidad de las puertas NAND, NOR Laboratorio ED.L.2: Implementación AOI, OAI, NAND y NOR ED.L.3: Circuitos secuenciales: latchs y biestables EC.L.1: Circuitos integrados digitales Laboratorio EC.L.2: Bloques funcionales MSI secuenciales EC.L.3: Transmisor serie Estructura de Computadores EC.L.4: Control microprogramado Simulación EC.S.1: Diseño de una RAM estática EC.S.2: Registro sensible a múltiples órdenes PLD’s Simulación PLD.S.1: Introducción a la herramienta ispLEVER PLD.S.2: Ecuaciones básicas en ABEL–HDL PLD.S.3: Ecuaciones When–Then–Else PLD.S.4: Tablas de verdad PLD.S.5: Diagramas de estado PLD.S.6: Diseños jerárquicos PLD.L.1: GAL22V10 (Práctica 2 y 3) Laboratorio PLD.L.2: GAL16V8 (Práctica 4 y 5) PLD.L.3: CPLD ispLSI1032 (Práctica 6) 2. PRÁCTICAS DE ELECTRÓNICA DIGITAL La primera de las asignaturas que imparte el área en esta titulación es Electrónica Digital, asignatura troncal que consta de 7’5 créditos (4’5 teóricos y 3 prácticos), que se imparte en el primer cuatrimestre del segundo curso. Estos tres créditos prácticos se dividen en 1’5 para prácticas de aula (problemas) y 1’5 para prácticas de laboratorio y simulación por ordenador. El objetivo de esta asignatura es dotar al alumnado de los conocimientos precisos, tanto sobre los fundamentos teóricos como sobre los componentes elementales que constituyen un sistema digital. Se imparten ocho prácticas realizadas en sesiones de dos horas cada una. De estas prácticas realizamos 5 de simulación, con la herramienta OrCAD; y tres de montaje real en el laboratorio. 2.1. Prácticas de simulación Para la realización de estas prácticas disponemos del centro de cálculo de la Escuela Politécnica Superior, con un servidor en donde está instalada la aplicación OrCAD, de la que utilizamos el Capture para la representación de los esquemas eléctricos, y del Simulate para la simulación y comprobación del circuito implementado. Seguidamente pasamos a describir las prácticas realizadas: 2.1.1. Práctica ED.S.1: Puertas básicas El objetivo de esta práctica es principalmente la iniciación al manejo de la herramienta de simulación OrCAD, aunque además se trata de hacer comprender al alumnado la propiedad asociativa de los operadores OR y AND, y razonar porqué los operadores NAND y NOR no son asociativos. La práctica consiste en realizar en la misma hoja de Capture en diseñar una puerta OR, AND, NOR Y NAND de tres entradas a partir de las puertas correspondientes de dos entradas. En esta práctica se utiliza el manual desarrollado por miembros del área utilizado para estas prácticas con OrCAD, como es “Guía rápida para la iniciación al diseño y simulación de sistemas digitales” [1]. 2.1.2. Práctica ED.S.2: Simplificación de funciones lógicas El objetivo de esta práctica es que el alumnado comprenda todos los pasos para implementar circuitos combinacionales y la simplificación de funciones lógicas, así como la implementación utilizando solamente puertas NAND. Se les pide diseñar un circuito combinacional que conociendo el voto de cuatro miembros de un tribunal determine automáticamente el fallo del mismo. El fallo del tribunal y los votos son del tipo SI/NO, no existe la abstención. Los votos son ponderados: el del presidente vale 3 puntos, el del secretario dos, y los de los dos vocales un punto. Los alumnos y alumnas deben realizar la implementación mediante el menor número posible de puertas lógicas básicas y mediante puertas NAND. 2.1.3. Práctica ED.S.3: El multiplexor y el decodificador como módulos lógicos combinacionales Con esta práctica se pretende que los alumnos y alumnas asimilen la utilización de estos bloques lógicos combinacionales universales (multiplexor y decodificador) para implementar lógica combinacional. Se trata de implementar un circuito combinacional que tenga como entrada un dígito BCD natural y detecte si el valor es mayor, menor o igual que un valor constante. Para implementar el circuito se ha de utilizar un multiplexor de 8 a 1 como es el circuito integrado 74LS151, y posteriormente realizar el mismo circuito pero utilizando dos decodificadores del integrado 74LS138 para transformarlo en uno de 4 a 16, y puertas NAND. En esta práctica además se introduce el concepto de bus empleado en OrCAD para lo que se utiliza el manual desarrollado por el área de conocimiento, “Utilidad y uso de buses” [2]. 2.1.4. Práctica ED.S.4: Circuitos combinacionales aritméticos En esta práctica se trata de diseñar un sumador/restador de 4 bits para lo cual es necesario utilizar los diseños jerárquicos. Se introduce, por tanto, el manejo de bloques jerárquicos en OrCAD, para lo que es útil el manual elaborado por miembros del área “Diseños jerárquicos en OrCAD” [3]. Se deben realizar tres esquemáticos correspondientes al mismo diseño: el nivel esquemático raíz será el sumador/restador de 4 bits que incluye puertas XOR para realizar el complemento a 2 del sustraendo y cuatro bloques que corresponden a cuatro sumadores completos, uno para cada bit. El segundo esquemático corresponde a este sumador completo y el nivel más bajo de la jerarquía es un semisumador que únicamente constará de dos puertas. De forma adicional se le propone al alumnado que añada la lógica combinacional necesaria para indicar cuando se ha producido desbordamiento. 2.1.5. Práctica ED.S.5: Circuitos secuenciales Finalmente se propone al alumnado la realización de un circuito que detecte una secuencia determinada, concretamente que detecte a la entrada la secuencia 2, 3, 1. Para ello debe de tener una entrada de datos DATA[1:0] y una sola salida que indique que ha detectado la secuencia indicada. El circuito debe incluir una entrada de RESET asíncrono y su entrada de reloj. 2.2. Prácticas de laboratorio: Para la realización de las prácticas de laboratorio instrumental disponemos del laboratorio del área de Arquitectura y Tecnología de Computadores, el cual cuenta con doce puestos de trabajo con el material siguiente: – Osciloscopio digital TDS 210. – Fuente de alimentación Protek 3015. – Generador de funciones HM8030–5. – Multímetro digital HM8011–3. – Placas de laboratorio, circuitos integrados, resistencias, diodos LED, etc. 2.2.1. Práctica ED.L.1: Universalidad de las puertas NAND y NOR: El objetivo de esta práctica es que el alumnado demuestre y compruebe experimentalmente que las puertas NAND y NOR forman un conjunto funcionalmente completo de operaciones en el álgebra de Boole. Para ello se le propone que implemente con puertas NAND (NOR) de dos entradas, utilizando solamente el circuito integrado 74LS00 (74LS02), las funciones lógicas NOT, AND y OR, demostrando de esta forma la universalidad de las puertas NAND (NOR). Posteriormente se le propone que implemente la función booleana siguiente f = Σ m (1, 3, 6, 7), utilizando solo el 74LS00 (74LS02). 2.2.2. Práctica ED.L.2: Implementación de funciones lógicas: suma de productos, producto de sumas, NAND y NOR: En esta práctica se propone la implementación de una función lógica de cuatro formas estándar distintas: mediante suma de productos y producto de sumas, para lo cual se emplearán los circuitos integrados 74LS08 y 74LS32; y mediante puertas NAND (74LS00) y solo con puertas NOR (74LS02). La función que se pide implementar es un sistema de alarma formado por cuatro detectores que debe activarse cuando se activen tres o los cuatro detectores, y no debe activarse cuando se active uno o ninguno; en el caso que se activen dos es indiferente la activación o no del sistema. 2.2.3. Práctica ED.L.3: Circuitos secuenciales: Latchs y biestables El objetivo de esta práctica es introducir a los alumnos y alumnas en los sistemas secuenciales. Esta práctica guiada se divide en tres partes. La primera de ellas consiste en montar un latch S–R con puertas NAND y en la comprobación experimental de su funcionamiento, así como el montaje y comprobación de un latch S–R con puertas NOR. La segunda parte de la práctica trata de comprobar el funcionamiento de dos biestables comerciales como son el biestable tipo D, 74LS74 y el biestable tipo J–K, 74LS112; comprobando sus entradas asíncronas y síncronas. Finalmente se les propone la realización de un divisor de frecuencia sencillo (por dos) con los dos tipos de biestables anteriores conectados convenientemente. Es decir que la frecuencia que se obtenga en la salida Q sea la mitad que la frecuencia de la señal de entrada CLK. 3. PRÁCTICAS DE ESTRUCTURA DE COMPUTADORES La segunda de las asignaturas a la que vamos a hacer referencia es Estructura de Computadores, asignatura obligatoria que consta de 4’5 créditos (tres teóricos y 1’5 prácticos), que se imparte en el segundo cuatrimestre del segundo curso. El objetivo de esta asignatura es dotar al alumnado de los conocimientos básicos sobre los componentes elementales de un computador, e introducirle en la arquitectura de un computador simple. Se imparten seis prácticas de dos horas cada una, excepto la primera de laboratorio que, por su amplitud, se realiza en dos sesiones de dos horas. Cuatro prácticas son de laboratorio y dos de simulación utilizando la misma herramienta de la asignatura anterior: OrCAD. 3.1. Prácticas de laboratorio: Al igual que la asignatura anterior estas prácticas se realizan en el laboratorio del área de Arquitectura y Tecnología de Computadores que consta de doce equipos con el material mencionado anteriormente. Además para la práctica del controlador microprogramado se utiliza un programador de la casa Hi–Lo Systems modelo Turbo All–11, conectado a un ordenador personal. 3.1.1. Práctica EC.L.1: Circuitos integrados digitales: El objetivo principal de esta práctica es que el alumnado asimile los parámetros básicos que definen el funcionamiento de los circuitos integrados digitales. En primer lugar se propone la obtención de la curva de transferencia (voltaje de salida en función del voltaje de entrada) del circuito integrado 7400 TTL estándar y también del circuito integrado 74HC00, que se corresponde con la misma función lógica anterior pero con tecnología CMOS de alta velocidad. A partir de las gráficas se pide obtener los valores de VILMáx y VIHMín de ambos circuitos integrados. A continuación obtienen los tiempos de propagación, midiendo con el osciloscopio los valores de tpHL y tpLH del circuito 7400 TTL estándar. Posteriormente se le propone la obtención de las curvas de salida (V–I) tanto a nivel alto como a nivel bajo de la salida. Con los datos obtenidos se pide calcular el factor de carga (fan–out) a nivel alto y a nivel bajo. Finalmente se hace un análisis de la salida triestado utilizando el circuito integrado 74LS125 que consta de cuatro buffer con una entrada de habilitación activa a nivel bajo. De este circuito se pide comprobar su funcionamiento, implementación de un bus y analizar sus características de conmutación. Señalar que para la realización de esta práctica se utilizan las hojas de características de los circuitos integrados nombrados y los apuntes referenciados “Tecnología de circuitos integrados digitales” [5]. 3.1.2. Práctica EC.L.2: Bloques funcionales MSI secuenciales: Registros y contadores: En esta práctica se pretende que el alumnado comprenda la estructura y el funcionamiento de los registros y contadores. Se le propone que compruebe el funcionamiento del registro universal de 4 bits incluido en el circuito integrado 74LS194, en sus modos de funcionamiento, así como en sus modos de entrada y salida de datos. Posteriormente se le pide que comprueben el funcionamiento de las distintas entradas de control y de la salida de acarreo de la serie de contadores 74160 y 74163. Asimismo se proponen varios ejercicios con estos contadores: implementar un contador BCD–XS3, y un contador BCD de dos dígitos con salida de acarreo. Finalmente se le propone que diseñen un divisor de frecuencia que a partir de una señal de reloj de 100 Hz obtengan una señal de salida de 2 Hz. 3.1.3. Práctica EC.L.3: Diseño con bloques funcionales MSI secuenciales: transmisor serie: Con esta práctica se pretende que comprendan la aplicación de los registros y contadores en la construcción de un transmisor serie. El ejercicio consiste en que diseñen un circuito, utilizando el registro y uno de los contadores de la práctica anterior, que realice una conversión paralelo–serie. Es decir, que entre un dato de cuatro bits en paralelo por las entradas del registro y salga en serie por una de sus salidas en cada flanco activo del reloj. El sistema debe tener una señal de inicio activa a nivel bajo, que indique cuando comienza la transmisión. 3.1.4. Práctica EC.L.4: Controlador microprogramado: diseño con EPROM: El objetivo de esta práctica es comprender la utilidad y el empleo de las memorias de sólo lectura (ROM) para implementar lógica combinacional, y su empleo como circuitos generadores de funciones o caracteres cualesquiera. Se trata de implementar un cartel de efectos luminosos mediante una EPROM 27C64 (8K x 8)y un contador que se utiliza para ir generando la secuencia de encendido de los leds. Los alumnos y alumnas deben realizar las conexiones necesarias entre el contador y la EPROM, además el contador deben diseñarlo del módulo necesario utilizando la EPROM para controlar la señal LOAD o CLEAR del contador. Cada salida de datos de la EPROM controlará cada led de visualización. Los alumnos y alumnas deben programar la EPROM con el programador disponible en el laboratorio de la casa Hi–Lo Systems modelo Turbo All–11. Señalar que para esta práctica y para la siguiente de simulación deben utilizar los apuntes desarrollados por los miembros del área: “Dispositivos de almacenamiento (I)” [6]. 3.2. Prácticas de simulación: Para las prácticas de simulación, al igual que en la asignatura de Electrónica Digital, se utiliza la herramienta OrCAD. Con esta herramienta se proponen las dos prácticas siguientes: 3.2.1. Práctica EC.S.1: Diseño de una RAM estática: En esta práctica a los alumnos y alumnas se les pide diseñar una memoria RAM estática de 4×2 (4 palabras de 2 bits cada una). Las líneas de datos serán las utilizadas tanto para escribir valores en las celdas de memoria como para obtener los datos almacenados en la misma. Así pues, las líneas de datos se representarán como un bus bidireccional, actuando como entrada durante la escritura y como salida durante la lectura. La escritura prevalecerá sobre la lectura en el caso de activación simultanea de ambas. Se recomienda utilizar diseño jerárquico y construir como bloque jerárquico al menos la celda básica de memoria. También deben manejar las señales de output enable, de las salidas de la RAM, para lo que les será útil el manual “Manejo de señales triestado”[4] 3.2.2. Práctica EC.S.2: Registro de 4 bits sensible a múltiples órdenes: El objetivo de esta práctica es estudiar el funcionamiento de un registro de trabajo y que el alumnado comprenda como actúan las operaciones más comunes sobre registros. Se les pide que diseñen un registro de trabajo de 4 bits capaz de realizar varias operaciones como son: puesta a cero de su contenido, complemento, incremento o decremento, lectura o escritura, y desplazamiento a derecha o izquierda. Debe tener unas señales IN[3..0] y OUT[3..0] para transferencias del bus al registro y viceversa. 4. PRÁCTICAS DE DISEÑO DE SISTEMAS MICROCOMPUTADORES: SÍNTESIS MEDIANTE PLD’S: Por último presentamos las prácticas de la asignatura Diseño de Sistemas Microcomputadores (PLD’s), asignatura optativa que se imparte en el primer cuatrimestre del tercer curso de la titulación en cuestión. Consta de 4’5 créditos, tres de los cuales son teóricos y 1’5 prácticos. El objetivo principal de esta asignatura es dotar a los alumnos de los conocimientos básicos sobre los distintos tipos de dispositivos lógicos programables, para lo cual utilizan los apuntes “Dispositivos lógicos programables”[7], así como estudiar un lenguaje de descripción de hardware de PLD, para lo cual se les suministra el material “Guía básica de diseño con el lenguaje ABEL–HDL”[8]. Esta asignatura es eminentemente práctica, por lo cual se realizan nueve sesiones de dos horas cada una: seis de ellas de simulación y tres de ellas de montaje real en el laboratorio de las realizadas en la simulación. 4.1. Prácticas de simulación: Para la realización de estas prácticas disponemos de la herramienta ispLEVER de Lattice Semiconductor instalada en un servidor del centro de cálculo de la Escuela Politécnica Superior. Además se les suministra a los alumnos el material incluido en “Guía básica de la herramienta ispLEVER v2.0. Diseño de Sistemas Digitales mediante Dispositivos Lógicos Programables” [9]. 4.1.1. Práctica PLD.S.1: Introducción a la herramienta ispLEVER: El objetivo principal de esta práctica es que los alumnos y alumnas se familiaricen con los pasos necesarios a realizar para la simulación de circuitos con esta herramienta. Se les pide un ejercicio sencillo, que implementen varias puertas lógicas de dos entradas (AND, OR, NAND, XOR) y un biestable tipo T con entrada de clear activa a nivel bajo. 4.1.2. Práctica PLD.S.2: Ecuaciones básicas en el lenguaje ABEL–HDL: En esta práctica se pretende que el alumnado aprenda a utilizar las ecuaciones básicas que se emplean en el lenguaje de descripción Hardware ABEL. Para ello se les propone diseñar un registro universal de 4 bits, implementado en una GAL22V10, que mediante tres señales de control realice ocho operaciones distintas (mantenimiento, desplazamiento a derecha e izquierda, complemento, incremento, carga paralela, AND y OR de la entrada y su contenido). Además debe incluir una entrada de clear asíncrono, y otra de preset síncrono. 4.1.3. Práctica PLD.S.3: Ecuaciones When–Then–Else: Los alumnos y alumnas deben de practicar con las ecuaciones When– Then–Else del lenguaje ABEL–HDL, para implementar en una GAL22V10 una unidad aritmético–lógica de 4 bits, que tiene dos operandos de entrada de 4 bits, y una salida de 4 bits que indique el resultado. Tiene dos entradas de control que indican la operación a realizar: suma, resta, AND lógica y complemento de una de las entradas. Además debe incluir una salida de acarreo para las operaciones de suma y resta. Adicionalmente se les propone el diseño de un contador BCD síncrono que dispone de unas entradas de carga, borrado y habilitación síncronas, activas a nivel bajo. Además de las salidas de la cuenta, debe tener una salida de acarreo, activa a nivel bajo. 4.1.4. Práctica PLD.S.4: Tablas de verdad: En esta práctica se les propone implementar en una GAL16V8 un contador con salida para un display de 7 segmentos, utilizando la utilidad de tablas de verdad del lenguaje ABEL–HDL. Debe tener, además de la entrada de reloj, tres entradas síncronas que son de test, reset y enable; y ocho salidas una para cada led del display y otra de acarreo. Señalar que para que la implementación pueda efectuarse en una sola GAL16V8, se debe implementar contando directamente en el formato del display. Otra opción más costosa sería implementar un contador BCD en una GAL16V8 y un decodificador BCD–7 segmentos en otra. 4.1.5. Práctica PLD.S.5: Diagramas de estado: El objetivo de esta práctica es que el alumnado estudie la programación en el lenguaje ABEL–HDL para realizar sistemas secuenciales síncronos. Se les propone el diseño de un sistema secuencial que controle el funcionamiento de un ascensor de sólo tres plantas e implementarlo en una GAL16V8. El sistema tiene como entradas el botón pulsado desde el interior del ascensor, una señal de restauración (RESET), y una entrada PULSO que indica que el ascensor ha pasado por algún piso. Sólo debe generar dos señales de salida SUBIR y BAJAR, según el sentido del movimiento a realizar. 4.1.6. Práctica PLD.S.6: Diseños jerárquicos: En esta última práctica se pretende que los alumnos y alumnas aprendan a utilizar los diseños jerárquicos de la herramienta ispLEVER, y las instrucciones del lenguaje ABEL–HDL que lo realizan: definición de los interfaces y la instanciación de los componentes. Se les propone la realización de un sistema que mida la anchura de un pulso. El sistema constará de un bloque de control, de dos contadores, dos registros y dos decodificadores BCD–7segmentos. Por tanto tienen que definir cuatro módulos: control, contador, registro y decodificador. Todo ello lo deben de implementar en un CPLD de la serie MACH4 de Lattice, el de menor coste posible. El sistema es el siguiente: RESET PULSO Contador BCD RESET ENA PULSO BLOQUE CLEAR DE CONTROL CLK CLK LOAD ENA Q0 CLEAR Qn CLK Decodificador Visualizador Registro D0 Q0 DN QN BCD 7 segmentos LOAD CLEAR CLK Figura 1: Diagrama de bloques del medidor de la anchura de un pulso 4.2. Prácticas de laboratorio: Las prácticas de laboratorio de esta asignatura consisten en realizar el montaje real de las prácticas realizadas en simulación en los componentes indicados para cada una de ellas. 4.2.1. Práctica PLD.L.1: GAL22V10: En esta práctica los alumnos y alumnas deben de programar físicamente en una GAL22V10 el fichero jedec obtenido de la simulación de la herramienta ispLEVER, con la ayuda del programador disponible en el laboratorio de la casa Hi–Lo Systems modelo Turbo All–11, de las prácticas 2 y 3 de simulación. Posteriormente deben comprobar su funcionamiento real en una placa de laboratorio. Las prácticas propuestas son un registro de 4 bits, una ALU y un contador BCD. 4.2.2. Práctica PLD.L.2: GAL16V8: En esta práctica deben programar una GAL16V8 con los ficheros jedec obtenidos de la herramienta en las prácticas 4 y 5 de simulación: contador en display–7segmentos, y el circuito de control de un ascensor; y comprobar su funcionamiento en el laboratorio. 4.2.3. Práctica PLD.L.3: CPLD ispLSI1032: Finalmente deben programar la última práctica de simulación: medidor del ancho de un pulso; en el CPLD ispLSI1032, que está incluido en una tarjeta desarrollada por el grupo de arquitecturas avanzadas de la Universidad de Córdoba. En esta tarjeta se incluye el CPLD nombrado, una GAL22V10 y display y led para visualizar las salidas necesarias. Además esta tarjeta dispone de conectores PCI, RS232 y JTAG para programarla desde un ordenador personal y de una alimentación externa, para que no sea necesario introducirla en el PC. 5. CONCLUSIONES: Como conclusión obtenemos que en todas las asignaturas relacionadas con el diseño lógico, es conveniente realizar prácticas tanto de simulación como de montaje real en un laboratorio. En la práctica docente se observa que cuando se realizan estos dos tipos de prácticas, el alumnado obtiene mejores resultados en la evaluación total de la asignatura. 6. REFERENCIAS [1] E. Sáez, F.J. Quiles. 1999. “Guía rápida para la iniciación al diseño y simulación de sistemas digitales”. A.C. Arquitectura y Tecnología de Computadores, Dpto. Electrotecnia y Electrónica, Universidad de Córdoba. [2] E. Sáez, F.J. Quiles. 1999. “Utilidad y uso de buses”. A.C. Arquitectura y Tecnología de Computadores, Dpto. Electrotecnia y Electrónica, Universidad de Córdoba. [3] E. Sáez, F.J. Quiles. 1999. “Diseños jerárquicos”. A.C. Arquitectura y Tecnología de Computadores, Dpto. Electrotecnia y Electrónica, Universidad de Córdoba. [4] E. Sáez, F.J. Quiles. 1999. “Manejo de señales triestado”. A.C. Arquitectura y Tecnología de Computadores, Dpto. Electrotecnia y Electrónica, Universidad de Córdoba. [5] F.J. Quiles. 2000. “Tecnologías de circuitos integrados digitales”. A.C. Arquitectura y Tecnología de Computadores, Dpto. Electrotecnia y Electrónica, Universidad de Córdoba. [6] F.J. Quiles, M.A. Ortiz López, M.A. Montijano Vizcaíno. 2000. “Dispositivos de almacenamiento (I)”. A.C. Arquitectura y Tecnología de Computadores, Dpto. Electrotecnia y Electrónica, Universidad de Córdoba. [7] F.J. Quiles. 2000. “Dispositivos lógicos programables”. A.C. Arquitectura y Tecnología de Computadores, Dpto. Electrotecnia y Electrónica, Universidad de Córdoba. [8] F.J. Quiles. 2003. “Guía básica de diseño con el lenguaje ABEL–HDL”. A.C. Arquitectura y Tecnología de Computadores, Dpto. Electrotecnia y Electrónica, Universidad de Córdoba. [9] F.J. Quiles, C.D. Moreno. 2002. “Guía básica de la herramienta ispLEVER v2.0. Diseño de Sistemas Digitales mediante Dispositivos Lógicos Programables”. A.C. Arquitectura y Tecnología de Computadores, Dpto. Electrotecnia y Electrónica, Universidad de Córdoba.