descargar

Anuncio

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

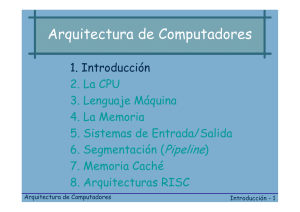

Tema 1: Introducción a la estructura de computadores

1. Objetivos de la asignatura.

2. Niveles de descripción de un computador.

3. Estructura básica de un computador convencional.

4. Evolución histórica: tecnología y arquitectura.

5. Lenguajes de descripción hardware.

1. Objetivos de la asignatura

La arquitectura de un computador está constituida por el conjunto de funcionalidades

disponibles para un programador que utiliza el lenguaje máquina, básicamente, el repertorio de

instrucciones y los elementos de memoria referenciados desde él, es decir, los registros

generales y la memoria principal. Las funcionalidades de una arquitectura se pueden conseguir

con diferentes organizaciones internas o estructuras, diferenciándose unas de otras

fundamentalmente en los parámetros de rendimiento y el coste. Finalmente, la estructura de un

computador se puede implementar con diferentes tecnologías, siendo nuevamente el coste y el

rendimiento los elementos diferenciales. Arquitectura, estructura y tecnología constituyen, pues,

tres niveles de estudio del hardware de un computador.

En esta asignatura abordaremos el estudio de la organización o estructura interna de un

computador. Para ello la materia la dividiremos en cuatro módulos. En el primero realizaremos

una introducción general a la estructura de computadores. En el segundo estudiaremos la

arquitectura del repertorio de instrucciones (ISA), arquitectura que define la interfaz hardwaresoftware de la máquina. En el tercero veremos toda la jerarquía de memoria de una máquina y

su gestión. Finalmente, en el cuarto estudiaremos las unidades de entrada/salida, los periféricos

y los buses de comunicación. El estudio de la unidad aritmético-lógica y la unidad de control se

aborda en la asignatura Ampliación de Estructura de Computadores.

Para situar con mayor precisión el objeto de estudio de esta asignatura analizaremos en el

apartado siguiente los diferentes niveles de descripción que se suelen contemplar en el estudio de un

computador digital.

2. Niveles de descripción de un computador

La estrategia que habitualmente se utiliza para abordar el estudio de los sistemas

complejos consiste en especificarlos a diferentes niveles de abstracción. Cada nivel se

caracteriza por:

A) Unos elementos de entrada, es decir, disponibles para el diseño en este nivel, y que

proceden del nivel inmediato inferior.

B) Unos elementos de salida, es decir, objetivos del diseño en este nivel, y destinados al

nivel inmediato superior.

C)

Una metodología de análisis y síntesis de los elementos de salida en términos de los de

entrada.

Con esta estrategia, la complejidad del sistema queda dividida, acotada y organizada en las

complejidades parciales de cada nivel, dentro de cuyos límites se puede aplicar una metodología

propia de estudio.

Al computador digital como sistema artificial complejo se le ha aplicado esta estrategia.

En nuestro caso consideraremos los siguientes niveles de abstracción dentro del estudio de un

1

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

computador digital:

APLICACIONES

ALGORITMOS

LENGUAJES DE ALTO NIVEL

SOFTWARE BASICO (S.O.)

ARQUITECTURA

Estructura de

Computadores

TRANFERENCI DE REGISTROS

LOGICO

ELECTRONICO

FISICO

Cada nivel se corresponde con la visión que tiene del sistema un tipo determinado de

usuario, y en cada uno podemos considerar dos procesos de estudio diferentes, el análisis y la

síntesis. El análisis parte de la implementación del sistema a un cierto nivel en términos de

elementos básicos del nivel inferior, y llega a determinar la función del mismo, es decir, su

especificación. El sentido de la síntesis es el opuesto, parte de la especificación de un sistema y

obtiene su implementación en función de los elementos básicos del nivel inferior. En la siguiente

figura hemos representado gráficamente esta relación:

Análisis

ESPECIFICACION

IMPLEMENTACION

Síntesis

Ejemplo:

a

a +b

Su m a dor

b

Sín t esis

a r r a st r e

a

a b a +b a r r a st r e

0

0

1

1

0

1

0

1

0

1

1

0

0

0

0

1

E specifica ción

An á lisis

b

a +b

a r r a st r e

Im plem en t a ción

2

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Comentaremos en los subapartados siguientes cada uno de estos niveles.

Nivel Físico

En el nivel físico se manipulan como elementos de entrada las formas geométricas que

se corresponden con las máscaras de difusión utilizadas en el proceso de fabricación de los

circuitos integrados del computador. Determinadas disposiciones de estas formas representan

dispositivos electrónicos concretos, tales como transistores, resistencias, etc., que son los

elementos de salida del nivel físico. En este nivel se suele utilizar como herramienta de estudio

software de manipulación gráfica con restricciones.

DD

OUT

IN

VSS

F ís ic o (s ilic io )

Nivel Electrónico

En este nivel los elementos de salida, es decir, los biestables y las puertas lógicas, se

obtiene a partir de dispositivos electrónicos (resistencias, transistores, etc.) conectados según

una determinada topología. Como metodología de estudio (análisis y síntesis) en este nivel se

utilizan técnicas cuantitativas de análisis en el plano eléctrico-temporal, fundamentalmente

ecuaciones algebraicas y diferenciales.

VD

D

IN

OUT

VS S

Circ u ito e lé c tric o

Nivel Lógico

Los elementos de entrada a este nivel son los biestables y las puertas lógicas, y los de

salida son módulos combinacionales y secuenciales tales como multiplexores, codificadores,

sumadores, registros, contadores, etc. Este nivel de estudio dispone de sus propias técnicas de

análisis y síntesis. El comportamiento de un circuito combinacional se representa con una

función lógica que admite una expresión algebraica manipulable simbólicamente dentro de un

formalismo matemático: el álgebra de conmutación (un álgebra de Boole). Para los circuitos

secuenciales se utiliza la teoría de las máquinas de estados finitos.

3

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

S

Q

NQ

R

Q

S

NQ

R

Circ u ito ló g ic o

Transferencia de Registros (RT)

Los elementos de entrada al nivel RT son registros, módulos combinacionales y

elementos de interconexión (buses y/o multiplexores). Los primeros mantienen el estado del

sistema, los segundos definen las transformaciones elementales del estado, y los terceros

permiten el intercambio de información entre los dos primeros. Los elementos de salida son el

conjunto de transferencias elementales posibles en la ruta de datos construida con los tres tipos

de elementos de entrada. Al contrario de lo que ocurría en los dos niveles anteriores, el nivel RT

no dispone de una herramienta propia de análisis y síntesis, aunque sí es posible utilizar los

modernos lenguajes de descripción hardware (por ejemplo VHDL) como instrumentos de

expresión precisa y estándar a este nivel.

bus

RMIC

RMICAUX

SECUENCIADOR

RI

MAR

ROM

DE

CONTROL

bus

Transferencia de registros

Arquitectura (lenguaje máquina)

Este es el nivel que separa el hardware del software. Los elementos básicos de entrada

son las transferencias y transformaciones posibles de información en la ruta de datos de un

computador. Con ellos se construyen las instrucciones máquina y su método de

secuenciamiento, es decir, lo que se denomina un lenguaje máquina. Lo más significativo de

este nivel es que con él comienzan los niveles propiamente simbólicos, es decir, niveles cuyos

componentes básicos no son objetos físicos, sino símbolos relacionados por un lenguaje, el

instrumento por excelencia del conocimiento simbólico.

El nivel de lenguaje máquina suele ser el primer nivel al que tiene acceso el usuario de

un computador, salvo si la máquina es microprogramable, en cuyo caso dispone de un nivel

intermedio que permite modificar el repertorio de instrucciones. Normalmente, el usuario no

utiliza directamente el lenguaje máquina, sino una representación simbólica del mismo conocida

como lenguaje ensamblador, que ofrece algunas prestaciones más que el puro lenguaje

máquina, como el uso de macros y la definición simbólica de constantes y posiciones de

memoria.

Este nivel queda definido por 1) el repertorio de instrucciones, con sus formatos, tipos de

direccionamiento, modos de secuenciamiento y representación de datos, y 2) la memoria y el

conjunto de registros visibles por el programador. En la actualidad cabe distinguir dos

planteamientos diferentes a la hora de definir el nivel máquina de un computador.

4

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

M em oria

R egistros

R epertorio d e in stru ccion es

LDR Ri, Dj

STR Ri, Dj

ADD Ri, Rj

En primer lugar está el planteamiento CISC (Complex Instruction Set Computers) que

define un repertorio de instrucciones bastante complejo y numeroso, con muchos tipos de

direccionamiento y muchos modos de control, pretendiendo reducir la distancia semántica que lo

separa de los lenguajes de alto nivel, y facilitar así el diseño del compilador. La

microprogramación es la técnica de diseño de la unidad de control con la flexibilidad suficiente

para facilitar la implementación de las máquinas CISC. Un caso extremo de proximidad al

lenguaje de alto nivel lo tenemos en arquitecturas avanzadas que tienen este tipo de lenguaje

como su lenguaje máquina.

En segundo lugar tenemos el planteamiento RISC (Reduced Instruction Set Computer),

que simplifica la complejidad y el número de instrucciones máquina, dejándolo reducido a un

conjunto pequeño y rápido que cubre un porcentaje muy elevado del peso computacional de los

programas. Los compiladores para este tipo de arquitecturas asumen la responsabilidad de

utilizar eficientemente unas instrucciones con poco contenido semántico pero elevada velocidad

de ejecución.

Dos aspectos importantes del nivel máquina son también la gestión de memoria y la

entrada/salida. Sin embargo, en los computadores actuales estos recursos los utiliza el

programa del usuario a través del sistema operativo.

Software básico (sistema operativo)

El Sistema Operativo (SO) no constituye un nivel del mismo tipo que los demás, por

ejemplo, el lenguaje máquina o el lenguaje de alto nivel. En realidad se trata de un gestor de

determinados recursos del nivel máquina que por la frecuencia y complejidad de uso resulta más

eficiente utilizarlos agrupados en una especie de máquina virtual que es el SO.

En los primeros computadores las funciones del SO eran escasas, limitadas

básicamente a la carga del programa y a la entrada salida. Sin embargo, las competencias de

este sistema han ido aumentando con la complejidad y sofisticación de las máquinas modernas,

que funcionan en entornos multiusuario y multitarea y que requieren una gestión de todos los

recursos de la máquina: la CPU, la jerarquía de memoria, el tratamiento de las excepciones, los

mecanismos de protección, etc.

El protagonismo que el SO tiene en un computador actual hace que cuando se diseña la

arquitectura de un procesador se tengan muy en cuenta las funciones de este sistema.

Lenguajes de alto nivel

En este nivel se utilizan lenguajes de programación con una sintaxis y una semántica

más complejas que las del lenguaje ensamblador. Estos lenguajes pretenden facilitar el trabajo

del programador aportando recursos expresivos más próximos a los problemas que se van a

resolver. En este sentido cabe diferenciar dos grandes grupos. Un primer grupo, denominado de

estilo imperativo como Pascal, Fortran, etc., que presentan una semántica operacional que

refleja directamente el funcionamiento de la máquina Von Neumann, es decir, que obligan al

programador a expresar la secuencia de órdenes cuya ejecución resuelve el problema en

cuestión. El segundo grupo lo formarían los lenguajes de estilo declarativo, como Prolog,

Miranda o Lisp (puro), que disponen de un modelo computacional diferente (aunque equivalente)

al de la máquina Von Neumann. En este caso el programador tan solo tiene que declarar las

relaciones lógicas o funcionales de los elementos que intervienen en la especificación del

problema a resolver.

5

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Este nivel requiere un proceso de traducción al nivel máquina que es realizado por un

programa denominado compilador. Se trata de un programa que toma como dato de entrada un

programa fuente escrito en un lenguaje de alto nivel, y produce como salida un programa objeto

escrito en lenguaje máquina con una semántica equivalente (igual significado).

Nivel L.A.N.

IF A ope B THEN

<sentencias1>

ELSE

<sentencias2>

L1

L2

Nivel L.M.

CMP A, B

Bope L1

<sentencias2>

BRA L2

<sentencias1>

......

Algoritmos

En el nivel algorítmico se expresa la resolución de un problema mediante un conjunto de

reglas aplicadas de forma sistemática y ordenada, es decir, mediante un algoritmo. Los

procedimientos que define un algoritmo son

independientes de cualquier lenguaje de

programación y de cualquier máquina particular.

Aplicaciones

Las aplicaciones se corresponden con dominios de actividad que pueden automatizarse

con el uso de un computador digital. Del análisis del dominio se extraen unas especificaciones

funcionales que son expresadas mediante algoritmos. Codificados estos algoritmos en un

lenguaje de programación y previa compilación, se ejecutan en la máquina.

• Inconvenientes de la división entre niveles

El establecimiento de niveles de abstracción en el estudio de un computador hace posible

acotar su complejidad al utilizar metodologías de análisis y síntesis propias en cada nivel, permitiendo

que dentro de un nivel el usuario pueda abstraerse de lo que ocurre en los demás niveles. Este

planteamiento que facilita sin duda el estudio del computador presenta sin embargo algunas

dificultades cuando se contempla el problema de la optimización. En efecto, a la hora de implementar

una especificación no sólo deben cumplirse todos los requerimientos funcionales de la misma,

además se deben optimizar ciertas funciones de calidad que generalmente tienen que ver con la

velocidad (maximización) y el costo (minimización). En efecto, existen ocasiones en las que

contemplar tan solo los niveles frontera de un nivel en el que se plantea un problema de diseño

puede dar lugar a la imposibilidad de optimizar la implementación. A título de ejemplo citaremos dos

casos en los que se presenta esta situación. El primero entre los niveles eléctrico y lógico, y el

segundo entre los niveles lenguajes de alto nivel y arquitectura (repertorio de instrucciones)

1) Niveles eléctrico <--> lógico Si nos planteamos el diseño de un multiplexor con

conmutadores bidireccionales (tecnología NMOS estática) respetando los niveles de diseño,

obtendríamos en primer lugar el esquema lógico (con puertas) del multiplexor, y después

expresaríamos cada puerta lógica en términos de los conmutadores bidireccionales.

6

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

X3

X2

X3

X2

MUX

Z

X1

X1

X0

X0

1

1

El diseño resultante es más costoso (mayor número de conmutadores) que el que podemos

obtener si planteamos el diseño directamente con conmutadores:

X3

S1

S0

S1

S0

S1

S0

S1

S0

1

X2

X1

X0

2) Niveles lenguaje de alto nivel <--> arquitectura

En este caso un compilador, para optimizar el código máquina que genera (mayor velocidad),

7

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

tiene en cuenta no sólo la arquitectura (repertorio de instrucciones) sino la forma en que se ejecutan

estas instrucciones (estructura) en la ruta de datos de la máquina. Este hecho puede dar lugar a que

el orden de las instrucciones máquina generadas no sea el orden lógico que utilizaría un

programador de lenguaje máquina que ignorase los detalles estructurales de la arquitectura. Esta

situación viene producida fundamentalmente por la segmentación y paralelización de las

instrucciones dentro de la máquina y se estudiará con detalle en las asignaturas de Ampliación de

Estructura de Computadores y Arquitectura e Ingeniería de Computadores.

3. Estructura básica de un computador convencional

La estructura básica de un computador actual sigue siendo la original de von Neumann,

una máquina secuencial que ejecuta datos escalares y que hemos representado en la siguiente

figura:

MEMORIA

P ROCES AD OR

CON TROL

EN TRAD A

S ALID A

U AL

REG.

La memoria almacena las instrucciones del programa, los datos iniciales, los resultados

parciales y los finales. Se accede de forma directa (RAM) a cualquier posición para realizar

operaciones de lectura o escritura.

El procesador es la unidad encargada de leer y ejecutar las instrucciones. Para ello

dispone de una ruta de datos constituida por un conjunto de registros (REG.), una unidad

aritmético-lógica (UAL), y unos buses de comunicación; y una unidad de control, que es la

encargada de generar las señales que gobiernan todos los dispositivos.

La entrada y salida constituyen la unidad para la transferencia de información con el

mundo exterior. Funcionalmente la máquina tiene las siguientes características:

1) Organización lineal de la memoria

2) Palabra de longitud fija.

3) Espacio único de direcciones.

4) Memoria única para datos e instrucciones sin diferenciar entre ambos.

5) Ejecución secuencial de las instrucciones salvo las de ruptura de secuencia

A esta organización básica de von Neumann se han ido incorporando algunas aportaciones

significativas entre las que destacaremos las siguientes:

a) Sistema de interrupciones, que permite la interrupción de un programa en ejecución

producida por una señal externa a la máquina. El sistema de interrupciones permite una mejor

sincronización de la Entrad/Salida con el exterior y la posibilidad de compartir la CPU por más de

un programa

8

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Programa principal

I1

I2

.

.

.Ii

Ii+1

.

señal de interrupción

línea de interrupción

.

.In

Rutina de tratamiento

i1

i2

.

.

im

b) Sistema de memoria cache, que permite disminuir el tiempo de acceso a la memoria

principal(Mp) ubicando una memoria de menor tamaño y mayor velocidad (memoria cache, Mc)

entre la CPU y Mp. El sistema explota la localidad de referencia de los programas haciendo que

Mc contenga en cada momento los bloques de Mp más referenciados, y evitando así que la CPU

tenga que acceder a Mp:

CPU

palbras

Memoria cache

(Mc)

bloques

Memmoria principal

(Mp)

c) Sistema de memoria virtual, que permite la ejecución de programas cuyo tamaño

supere el de la Mp. Para ello el sistema mantiene en Mp, de forma transparente para el

programador, tan sólo el conjunto de páginas activas (con mayor probabilidad de ser

referenciadas) del programa en ejecución. Las restantes páginas que completan el programa

residen en la memoria secundaria, hasta que son referenciadas, en cuyo caso el sistema las

activa llevándolas a Mp:

9

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Memoria principal

(Mp)

páginas

Memoria secundaria

(Ms)

4. Evolución histórica: tecnología, estructura y arquitectura

La velocidad de procesamiento de información de un computador está determinada

básicamente por tres elementos: arquitectura, organización (o estructura) y tecnología. Podemos

analizar la influencia de estos elementos en la velocidad de procesamiento de información de un

computador teniendo en cuenta que el tiempo T de ejecución de un programa se puede expresar

como el producto de tres factores: el número de instrucciones del programa (N), el número

medio de ciclos por instrucción (CPI), y el tiempo de ciclo (Tc), como hemos representado en la

siguiente figura:

Tc

P r ogr a m a

1 ciclo

I1

3 ciclos

I2

2 ciclos

I3

N

CP I (n º de ciclos m edio/in st r u cción )

in st r u ccion es

.

t iem po

T

10

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

T = N * CPI * Tc

Arquitectura del computador

Compilador

Organización del computador

Tecnología

Arquitectura del computador

Organización del computador

T

N

CPI

Tc

=

=

=

=

tiempo de ejecución del programa

número de instrucciones del programa

número medio de ciclos por instrucción

tiempo de ciclo

Es decir, mientras la arquitectura influye a través del número medio de ciclos por instrucción y del

número total de instrucciones, la organización lo hace a través de éste último y el tiempo de ciclo,

mientras que la tecnología lo hace casi exclusivamente a través del tiempo de ciclo (o su inversa, la

frecuencia de reloj del procesador). El tiempo de ciclo viene determinado por los tres niveles tecnológicos:

físico, electrónico, lógico y trasferencia de registros.

La tecnología ha experimentado una transformación continua durante las últimas décadas. Desde

la aparición del primer computador comercial, la industria informática ha pasado por cuatro generaciones

de computadores, diferenciadas básicamente por la tecnología de los componentes básicos. Los relés y las

válvulas de vacío de 1940 a 1950, los diodos y transistores discretos de 1950 a 1960, los circuitos

integrados de pequeña y media escala de integración (SSI/MSI) de 1960 a 1970, y los circuitos integrados

de alta y muy alta escala de integración (LSI y VLSI) desde 1970 en adelante. La disminución del tiempo

de conmutación de los componentes electrónicos ha repercutido directamente en el aumento de velocidad

de los computadores. También el aumento de la capacidad de integración y de encapsulado han repercutido

en la misma dirección. Los cambios tecnológicos alteran constantemente las relaciones de

compromiso tecnología/organización/arquitectura, obligando a la reconsideración de viejas

ideas ante un nuevo avance tecnológico.

Aumento de rendimiento a través de la organización y arquitectura

A lo largo de las últimas cuatro décadas la organización y arquitectura de computadores

ha experimentado un desarrollo gradual, no traumático, que ha ido decantando aquellas

características responsables de las mejoras de rendimiento.

Paralelismo y Segmentación

Las organizaciones y arquitecturas paralelas consiguen que en ciertos instantes de

tiempo el computador procese simultáneamente más de una operación básica. La simultaneidad

temporal se consigue fundamentalmente con dos técnicas: el paralelismo y la segmentación. La

primera ejecuta simultáneamente varias operaciones independientes replicando el número de

operadores hardware. La segunda descompone el operador y la operación correspondiente en

etapas secuenciales y autónomas, de manera que simultáneamente se puedan ejecutar etapas

diferentes de varias operaciones. Ambas técnicas se consideran como dos formas del

paralelismo: el paralelismo espacial o replicación la primera, y el paralelismo temporal la

segunda.

La idea básica de la segmentación estaba ya latente en la propuesta de von Neumann

para construir el primer computador de programa almacenado. Al hablar sobre las técnicas de

entrada/salida, sugería la conveniencia de disponer un buffer que permitiese el solapamiento

11

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

de la ejecución del programa con las operaciones de E/S, es decir, una forma primaria de

procesamiento segmentado.

Procesadores Segmentados

Se trata de arquitecturas monoprocesador que operan con una organización interna en

la que se segmenta la ejecución de las instrucciones a fin de iniciar una (y finalizar otra) cada

ciclo de operación. Sin embargo este objetivo límite difícilmente llega a conseguirse debido a los

riesgos estructurales, las dependencias de datos, las bifurcaciones y las excepciones. Para

reducir al máximo el efecto de tales ineficiencias se utilizan técnicas software como la

reordenación estática de instrucciones, el renombramiento de registros, y los saltos retardados; y

técnicas hardware como el adelantamiento (forwarding), la reordenación dinámica de

instrucciones y la predicción dinámica de saltos.

Bú squ eda

Decodifica ción

Un ida d

Bu

Un ida d

De

E jecu ción

E scr it u r a

Un ida d

Ej

Un ida d

Es

Regist r os

In st r u cción 1

Bu 1

In st r u cción 2

De1

E j1

E s1

Bu 2

De2

E j2

E s2

Bu 3

De3

E j3

E s3

Bu 4

De4

E j4

In st r u cción 3

In st r u cción 4

E s4

ciclos

1

2

3

4

5

6

7

8

Procesadores Superescalares

Un procesador superescalar de grado m emite m instrucciones por ciclo, debiendo ser

también m el paralelismo a nivel de instrucción para explotarlo completamente. En estos

procesadores los recursos para la decodificación y ejecución de instrucciones se incrementan

hasta el punto de disponer de m cauces segmentados operando concurrentemente, si bien en

algunas etapas los cauces pueden compartir algunas unidades funcionales. En general, los

conflictos por dependencias de datos, de control y estructurales de los procesadores escalares

segmentados siguen existiendo en los superescalares con mayor complejidad.

Las máquinas superescalares proporcionan compatibilidad a nivel del código objeto con

las máquinas escalares, detectando el paralelismo de las instrucciones en tiempo de ejecución.

Normalmente, se dividen las instrucciones máquina en categorías, y como mucho una

instrucción de cada categoría pueden emitirse simultáneamente.

12

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Un ida d

de

Bú squ eda

Un ida d

de

E m isión

de

In st r u ccion es

Un ida d de ejecu ción 1

vía 1

Un ida d de ejecu ción 2

vía 2

Un ida d de ejecu ción 3

vía 3

Procesadores VLIW

En un procesador VLIW (Very Long Instruction Word) una única instrucción especifica

más de una operación concurrente, reduciéndose el número de instrucciones por programa en

comparación con el caso escalar. Las organizaciones VLIW extendieron y formalizaron el

concepto de microcodificación horizontal que se venia utilizando años atrás para el diseño de

procesadores de propósito especial dedicados a tareas intensivas en cálculo, tales como el

procesamiento de señales digitales. Utilizando técnicas avanzadas de compilación se puede

extraer el paralelismo de grano fino de un amplio rango de aplicaciones científicas y de propósito

general. En estos procesadores los conflictos por dependencias de datos y estructurales se

resuelven antes de la ejecución, y son explícitamente controlados por las instrucciones. El

hardware adicional se dedica a caminos de datos paralelos y más unidades funcionales, en

lugar de a lógica de control y sincronización.

In st r u cción la r ga

DE C

Un ida d de ejecu ción 1

DE C

Un ida d de ejecu ción

DE C

Un ida d de ejecu ción 3

Regist r os

Procesadores Vectoriales

Los procesadores vectoriales disponen de operaciones que trabajan sobre vectores de

números. Por ejemplo, una operación vectorial puede sumar dos vectores de 64 elementos en

punto flotante dando como resultado otro vector de 64 elementos. La instrucción vectorial es

equivalente a un bucle completo en el que se calcula un elemento del resultado en cada

iteración, se actualiza el índice y se bifurca al comienzo.

Una simple instrucción vectorial especifica, pues, una gran cantidad de trabajo, por lo

que se reduce la anchura de banda necesaria para su lectura en comparación con la de las

instrucciones escalares equivalentes. Además, el acceso a los datos tiene un patrón conocido.

Desde el punto de vista arquitectónico son procesadores segmentados con instrucciones

máquina vectoriales. Al no existir dependencias entre operaciones de una instrucción vectorial,

se explota eficientemente la segmentación en las unidades aritméticas. Pero para conseguir el

13

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

rendimiento máximo de estas arquitecturas hay que alimentar a las unidades funcionales

segmentadas con nuevos datos en cada ciclo de reloj, lo que requiere un gran ancho de banda

con la memoria principal.

Mem or ia

Regist r os

Un ida d a r it m ét ica segm en t a da

Regist r os

Un ida d a r it m ét ica segm en t a da

Regist r os

Un ida d a r it m ét ica segm en t a da

Multiprocesadores de Memoria Compartida

Se trata de arquitecturas compuestas por un conjunto de procesadores que acceden a

una única memoria común a través de una red de interconexión. Utilizan memorias cache

locales para las que hay que resolver el problema de su coherencia con respecto a la memoria

principal y entre sí. Las soluciones que se adoptan tienen un mayor o menor soporte hardware y

dependen mucho de la red de interconexión. Otro problema que plantean estas arquitecturas es

el de la sincronización de los diferentes procesadores cuando participan de una tarea común.

Para ello es necesario disponer del soporte hardware en forma de instrucciones máquina del tipo

TEST&SET, TEST&AND, etc. que permiten implementar secciones críticas y otros mecanismos

de sincronización a nivel del sistema operativo.

P r ocesa dor

P1

P r ocesa dor

P2

P r ocesa dor

Pn

Red de in t er con exión

(bu s, r ed m u lt iet a pa , cr ossba r )

Mem or ia com ú n com pa r t ida

Multicomputadores

Son multiprocesadores de memoria distribuida donde cada procesador tiene un espacio

privado de direcciones. Se comunican y sincronizan mediante paso de mensajes a través de una

red de interconexión. Las topologías de red más utilizadas son la malla y el hipercubo.

14

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Mem or ia

M1

Mem or ia

Mn

P r ocesa dor

P1

P r ocesa dor

Pn

Red de in t er con exión est á t ica

5. Lenguajes de descripción hardware.

Los lenguajes de descripción hardware son lenguajes de alto nivel con una sintaxis

similar a los de programación (C, ADA, Pascal, Modula, etc.) y una semántica que permite el

modelado y simulación de los dispositivos hardware a diferentes niveles de abstracción. Los

primeros lenguajes de este tipo sólo pretendían servir de vehículo de comunicación del diseño.

Se trataba de formalismos de especificación de los dispositivos hardware desarrollados por

instituciones universitarias o por industrias electrónicas que alcanzaron escasa difusión. Pero los

actuales lenguajes han adquirido un alto grado de estandarización y han adoptado los nuevos

conceptos de la ingeniería software, permitiendo la verificación de la especificación del diseño

mediante simulación. Se utilizan como vehículo de entrada a muchas herramientas de diseño

automático. Revisaremos brevemente algunos de estos lenguajes

5.1. Lenguajes precursores

CDL (Computer Design Language) fue desarrollado por Yaohan Chu a comienzo de los años

60 bajo el principio de separación de la componente lógica y electrónica de un computador

digital. CDL refleja directamente el hardware y sus operaciones, es decir, existe una

correspondencia uno-a-uno entre los objetos y operaciones hardware (registros, RAMs, relojes,

suma, cuenta, etc.) y las construcciones del lenguaje. La primera versión del simulador CDL para

IBM 7090 estuvo disponible en 1968, y la versión tercera para Univac pocos años más tarde. Se

utilizó en universidades y en la industria del radar y aeronáutica.

DDL

(Digital systems Design Language) se desarrolló a mediados de los 60 en la

Universidad de Wisconsin con varios objetivos: precisión y concisión para facilitar la

especificación de los diseños, potencia suficiente para modelar sistemas complejos,

independencia respecto a cualquier tecnología o procedimiento de diseño, capacidad de

especificación a diferentes niveles de abstracción y, finalmente, una sintaxis y una semántica

que permitieran la documentación jerárquica del diseño.

AHPL (A Hardware Programming Language) fue propuesto por F.J. Hill y G.R. Peterson unos meses

más tarde que el CDL y DDL, y apareció publicado por primera vez en 1973 en la edición original de

Digital Systems: Hardware Organization and Design. Los autores concibieron AHPL como un lenguaje

de síntesis: todo dispositivo síncrono que pudiese ser implementado en hardware debía ser

expresable en AHPL de manera tal que se pudiese traducir a una realización física siguiendo un

conjunto simple de reglas. En opinión de uno de sus autores, F.J. Hill, que participó como

miembro del grupo de trabajo que formuló las especificaciones originales para VHDL, la

existencia de AHPL favoreció la incorporación de mecanismos para permitir el proceso de

síntesis en VHDL.

15

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

ISPS

(Instruction Set Processor Specifications) con este lenguaje se dió un paso importante

hacia la formalización del proceso de diseño a niveles de comportamiento. Además de la

simulación y la síntesis, ISPS se utilizó en la generación de software, la verificación de

programas y la evaluación de arquitecturas. ISPS favoreció los aspectos de comportamiento

sobre los estructurales pero sin eliminarlos completamente.

TI-HDL (Texas Instruments-HDL) es un lenguaje de descripción jerárquica del diseño,

estructurado en bloques y basado en texto, que se ha utilizado principalmente en el diseño de

circuitos integrados. Procede de antiguos lenguajes usados allá por 1968, concretamente el

TIBSD (TI Boolean System Description), desarrollado como lenguaje de entrada de datos para

un sistema CAD de circuitos impresos, y Fusim (Functional Simulator), utilizado para describir

modelos de alto nivel de microprocesadores y para generar prototipos de patrones de tests.

5.2. Lenguajes actuales

Verilog es un lenguaje de descripción hardware diseñado por la compañía Cadence Design

Systems Inc., que se ha venido utilizando como lenguaje del simulador digital Cadence. El uso

de Verilog está promovido por la Open Verilog International (OVI), que publicó en octubre del 91

la primera versión del Hardware Description Language Reference Manual. En Verilog la unidad

de diseño fundamental es el módulo, que describe un componente hardware con su interfaz y

contenido. Desde un punto de vista funcional, un módulo Verilog contiene la información de una

entidad y su correspondiente arquitectura VHDL. Verilog no proporciona compilación

independiente de módulos: todos los módulos relacionados con el mismo diseño y simulación

deben estar en el mismo archivo.

UDL/I (Unified Design Language for Integrated circuits) es un lenguaje de descripción

hardware que se viene desarrollando desde 1989 por la Japan Electronic Industry Development

Association, dependiente de importantes compañías japonesas tales como NTT. Una de las

características de UDL/I es que pretende ser específico para modelar circuitos integrados. La

única unidad de diseño existente en UDL/I es la descripción de diseño, que comprende varias

subentidades denominadas descripciones de módulos. Una descripción de diseño contiene el

modelo de un circuito integrado que consta de varias subunidades o módulos, cada uno de los

cuales está especificado por una descripción de módulo.

VHDL (VHSIC Hardware Description Language) es un lenguaje impulsado por el Departamento de

Defensa de los Estados Unidos dentro del programa VHSIC (Very High Speed Integrated Circuits) y

estandarizado por IEEE Computer Society. Con VHDL se puede estudiar un sistema digital a diferentes

niveles de abstracción dentro de un único lenguaje de programación, acelerando considerablemente las

diferentes fases diseño y proporcionando un mejor conocimiento del mismo cuando se aborda la fase de

implementación física. VHDL es un lenguaje con una semántica orientada a la simulación. Por ello, su

principal dominio de aplicación es el modelado de dispositivos hardware para comprobar su corrección

funcional. Sin embargo, como ilustra la siguiente figura sus áreas de aplicación son cada vez más

numerosas, y hoy día se utiliza en la síntesis automática, la diagnosis de fallos, la verificación formal, el

modelado de rendimiento y la documentación

16

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

S ín te s i

i1

su m a

ca r r y

i2

Mo d e la d o

Re n d im ie n t

D o c u m e n ta c i

Cir cu it o

semisu ma do

Compon en t es:

pu er ta AND

pu er ta OR

pu er ta XOR

............................

............................

VHD L

EN TITY cir cu ito IS

P ORT(i1,i2 : IN bit ; su m , ca r r y : OU T);

E N D cir cu it o;

ARCH ITE CTU RE est r u ct u r a OF cir cu it o

BE GIN

P ROCE SS

..................

E ND

END

Ve rific a c ió

F o rm a

D ia g n o s is d e

i1

su m a

i2

¿cor r ect o

S im u la c ió

ca r r y

si

CLK

X

Z

La síntesis automática tiene como objetivo la generación de dispositivos digitales a partir de una

especificación inicial expresada en un lenguaje de descripción hardware. VHDL, al ser un lenguaje con

una semántica poco formal, en el que se pueden mezclar diferentes estilos de descripción, no es el más

apropiado para utilizar como entrada en las herramientas de síntesis. Sin embargo, dado su status de

estándar IEEE y su amplia aceptación en la industria electrónica, resulta muy conveniente no romper el

ciclo de diseño saliendo de VHDL en la fase de síntesis. Por ello, lo que se realiza habitualmente en este

terreno es definir subconjuntos sintetizables de VHDL. En este sentido cabe distinguir dos grandes

subconjuntos. Uno que engloba las construcciones secuenciales de VHDL, utilizado para la síntesis de alto

nivel, y otro que parte de unas construcciones concurrentes de VHDL que permiten descripciones de

dispositivos a nivel de transferencia de registros (RTL), utilizado para la síntesis de bajo nivel.

17

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

La diagnosis de fallos en circuitos digitales se puede plantear a partir de las descripciones VHDL

de los mismos. En efecto, en lugar de identificar la parte de circuito que falla, podemos localizar la parte de

descripción VHDL cuya implementación hardware tiene un fallo físico y está causando el fallo de

comportamiento observado. En principio esta diagnosis es similar a la que se realiza a nivel de puertas,

pero en este caso el nivel de descripción hardware puede ser más alto y consecuentemente el modelo de

fallos será diferente.

La verificación formal de un diseño consiste en probar que para todos los estados iniciales

aceptables y para todas las entradas posibles, la implementación del diseño cumple su especificación. Las

otras dos alternativas para verificar un diseño, la síntesis automática y la simulación funcional, pueden

resultar incompletas. En efecto, los diseños producidos por síntesis automática son correctos por

construcción si los componentes primitivos están completamente verificados y si las transformaciones

realizadas en el proceso de síntesis son así mismo correctas. Sin embargo, probar la corrección formal de

un método de síntesis implica probar la corrección formal del método en sí y del software que lo

implementa, tarea que puede resultar impracticable. Por otra parte, la verificación funcional por simulación

exhaustiva también es impracticable a partir de una complejidad media en el diseño. La verificación formal

requiere un modelo matemático para representar las propiedades bajo estudio y un cálculo para realizar

computación simbólica sobre el modelo. La lógica es la rama de las matemáticas más ampliamente

utilizada en la verificación formal, incluyendo la lógica de predicados de primer orden, la lógica de orden

superior y la lógica temporal. Al no existir una semántica formal para VHDL los sistemas de verificación

formal, al igual que los sistemas de síntesis, se limitan a subconjuntos del lenguaje.

Los modelos de rendimiento constituyen el nivel más alto de abstracción de los sistemas

electrónicos. Estos modelos se utilizan principalmente para estudiar la capacidad global de procesamiento

de información de un sistema en las primeras etapas del proceso de diseño. El objetivo es identificar las

principales unidades funcionales y definir su forma de actuación en la transformación de los datos de

entrada en datos de salida. A este nivel de conceptualización el diseñador ve una unidad funcional como

algo que realiza una cierta tarea en un cierto tiempo, sin detalles específicos sobre la forma de realizar la

tarea. En realidad, puede que estos detalles no se conozcan aún en esta fase del diseño. Debido a esta

ocultación de detalles sobre los valores de los datos y sus transformaciones específicas se dice que los

datos son no interpretados, y para resaltar este hecho a los modelos de rendimiento se les denomina a veces

modelos no interpretados. VHDL, al disponer de recursos expresivos con alto nivel de abstracción, facilita

la confección de modelos de rendimiento basados en redes de Petri extendidas y colas estocásticas.

Finalmente, la documentación es una de las tareas más importantes en todo proceso de diseño, y

muy particularmente cuando el sistema tiene el grado de complejidad de los circuitos actuales. En estos

casos se hace indispensable disponer de lenguajes con una elevada capacidad de abstracción y ampliamente

aceptados por los diseñadores, como ocurre en la actualidad con VHDL.

Como muestra la siguiente figura, VHDL dispone de recursos expresivos para cubrir totalmente

la descripción y el modelado de dispositivos digitales en los niveles circuito lógico, transferencia de

registros y chip. Los niveles de sistema y circuito eléctrico sólo se cubren parcialmente. Pero lo más

interesante del lenguaje en este aspecto es que permite mezclar en una misma descripción diferentes

niveles. Esto, unido al modelo de concurrencia que permite la construcción de modelos estructurales en los

que los componentes básicos pueden a su vez ser descritos con modelos estructurales, hace posible el

establecimiento de una descomposición estructural de la jerarquía de diseño.

18

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

S OF TWAR E

AR QU ITECTU RA

VHD L

TRAN S F EREN CIA D E REGIS TROS

LÓGICO

ELECTRICO

F ÍS ICO

Á

19

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Tema 2: Formato de las instrucciones y modos de direccionamiento

1. Formato de las instrucciones

2. Propiedades generales del direccionamiento

3. Modos de direccionamiento.

4. Soporte de los modos de direccionamiento a los lenguajes de alto nivel

Las instrucciones máquina son las acciones elementales que puede ejecutar un computador.

Una acción compleja deberá codificarse como una secuencia de instrucciones máquina en lo que se

denomina un programa. La arquitectura de un procesador entendida como el conjunto de recursos

operativos disponibles por un programador a nivel de lenguaje máquina queda definida por el repertorio

de instrucciones (ISA: Instruction Set Architecture). En general, una instrucción codifica una operación

básica que el computador realiza sobre unos datos ubicados en la memoria o en los registros de la

máquina y a los que accede utilizando un modo de direccionamiento. Por consiguiente, la arquitectura

ISA de un procesador viene determinada por los siguientes factores:

a) Tipos de datos y formatos que pueden manejar las instrucciones: naturales, enteros, reales,

caracteres, etc.

b) Modos de direccionamiento de los datos ubicados en la memoria: inmediato, directo,

indirecto, etc. Estos dos factores son determinantes para la implementación eficiente de las

estructuras complejas de datos de un lenguaje de alto nivel.

c) Conjunto básico de operaciones que se pueden realizar sobre los datos: suma, resta, etc.

Propiedad de ortogonalidad

Diremos que un repertorio es ortogonal cuando las instrucciones puedan combinar los elemento

de los tres factores anteriores sin ninguna restricción. La ortogonalidad completa no se da en ningún

repertorio de máquina real.

tipo de direccionamiento

.

indirecto -directo

--

inmediato --

(MUL, real, indirecto)

ADD

|

|

XOR

SUB

|

|

MUL

|

operaciones

entero -natural -real --

tipo de datos

1. Formato de las instrucciones

Las informaciones relativas a los cuatro factores anteriores se codifican en cada una de las

instrucciones siguiendo un formato preestablecido. El formato determinará la longitud en bits de las

1

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

instrucciones y los campos que codifican el valor de los factores citados. En general una

instrucción se compone de los siguientes campos:

• Código de operación (CO)

• Operandos fuente (OP1, OP2,...)

• Operando destino o Resultado (OPd)

• Instrucción siguiente (IS)

CO

OP1

OP2

..........

OPd

IS

El CO determina la operación que se realiza sobre OP1,OP2,... El resultado se deja en OPd. Lo normal es

que el número de operandos fuente de un repertorio no pase de 2. La dirección de la instrucción siguiente IS

queda implícita en todas las instrucciones (se trata de la instrucción siguiente del programa) salvo en las

instrucciones de ruptura condicional o incondicional de secuencia.

1.1 Diseño del repertorio de instrucciones.

Los repertorios de instrucciones podemos clasificarlos atendiendo a los siguientes criterios:

A) Número de operandos explícitos por instrucción

a) 3 operandos explícitos

CO

ejemplo:

OP1 (fuente 1)

OP2 (fuente 2)

OP3 (destino)

AÅB+C

ADD B,C,A

• Máxima flexibilidad

• Ocupa mucha memoria si los operandos no están en registros

b) 2 operndos explícitos

CO

OP1 (fuente 1)

ejemplo:

ADD B, C

OP2 (fuente

BÅB+C

• Reduce el tamaño de la instrucción

• Se pierde uno de los operandos

c) 1 operando explícito

CO

OP1 (fuente

ejemplo:

ADD B

Acumulador Å <Acumulador> + B

• Supone que fuente 1 y destino es un registro predeterminado (acumulador)

• Se pierde un operando fuente

d) 0 operandos explícitos

CO

ejemplo:

ADD

cima de pila Å <cima de pila> + <cima de pila - 1>

2

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

• Se trata de computadores que trabajan sobre una pila

Ejemplo:

3 operandos

ADD C, D, C

SUB A, B, A

MUL A, C, E

ADD

SUB

MUL

MOV

E = (A – B)*(C + D)

2 operandos

1 operando

LOAD A

C, D

SUB B

A, B

STORE A

A, C

LOAD C

C, E

ADD D

MUL A

STORE E

0 operandos

(PUSH) LOAD A

(PUSH) LOAD B

SUB

(PUSH) LOAD D

(PUSH) LOAD C

ADD

MUL

(PULL) STORE E

B) Forma de almacenar operandos en la CPU

a) Arquitectura de pila (HP 3000/70)

b) Arquitectura de acumulador (Motorola 6809)

c) Arquitectura de registros de propósito general (IBM 360)

Ejemplo: código máquina en cada una de las tres alternativas correspondiente a la sentencia de

asignación C := A + B

C=A+B

Pila

Acumulador

Conjunto de registros

PUSH A

LOAD

A

LOAD R1, A

PUSH B

ADD

B

ADD

ADD

STORE C

POP

R1, B

STORE C, R1

C

Las arquitecturas de registros de propósito general se clasifican a su vez atendiendo al número

máximo de operandos (2 ó 3) que pueden tener las instrucciones de la ALU y cuantos de ellos se

pueden ubicar en memoria:

(operandos - en memoria)

(

3

-

0

) Arquitectura registro-registro (también llamada de carga-almacenamiento).

Utilizan tres operandos totales y cero en memoria. Formato de longitud

fija y codificación simple de las instrucciones que pueden ejecutarse en un

número similar de ciclos. Facilitan un modelo simple de generación de

código apara el compilador. SPARC, MIPS, PowerPC

(

2

-

1

) Arquitectura registro-memoria. Utilizan dos operandos totales con uno

ubicado en la memoria. Intel 80X86, Motorola 68000

(

3

-

3

) Arquitectura memoria-memoria. Utilizan tres operandos totales con la

posibilidad de ser ubicados los tres en memoria. VAX

Códigos de operación de longitud fija y variable

n

Una máquina con un formato de instrucción que dedica n bits al CO permitirá 2 instrucciones diferentes,

cada una de las cuales puede tener diferente número de operandos (0, 1, 2, 3, etc.). Los bits del campo

3

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

OPERANDOS se pueden utilizar para extender el CO de aquellas instrucciones con menor número de operandos.

Ejemplo: Partimos de una máquina con instrucciones de longitud fija de 24 bits y consideraremos los

siguientes supuestos:

1) La máquina dispone de 16 registros generales

4

4

16

CO

R

OP

Ö En este caso se pueden codificar 16 instrucciones de 2 operandos: uno en registro y el otro en

memoria

2) Si queremos extender el CO se puede utilizar una de las 16 combinaciones del CO (quedarían

15 con 2 operandos), por ejemplo CO = 1111, dando la posibilidad de codificar 16 instrucciones de

1 operando en memoria. Si queremos seguir extendiendo el CO podemos utilizar CO = 1111 1111

(quedarían 15 con 1 operando) para definir instrucciones sin operandos (216 = 65.536)

En la siguiente tabla se resume el proceso descrito.

R

0000

R

0001

.

.

.

.

.

.

R

1110

1111 0000

1111 0001

.

.

.

1111 1110

1111 1111

1111 1111

1111 1111

OP

OP

.

.

.

.

.

15 instrucciones de

2 operandos

(CO de 4 bits)

15 instrucciones de

1 operando

OP

0000 0000 0000 0000

0000 0000 0000 0001

.

.

.

1111 1111 1111 1111

(CO de 8 bits)

216 = 65.536

instrucciones de

0 operandos

(CO de 24 bits)

Otra alternativa: dedicar 2 bits para indicar si la instrucción tiene 0, 1 o 2 operandos:

2

L

2

CO

4

16

R

OP

En este caso podemos codificar los siguientes grupos de instrucciones:

L = 00 Î CO de 2 bits Î 4 instrucciones de 2 operandos

L = 01 Î CO de 6 bits Î 64 instrucciones de 1 operando

L = 10 Î CO de 22 bits Î 4.194.304 instrucciones de 0 operandos

Optimización del CO variable en función de la frecuencia de las instrucciones.

Una posibilidad a la hora de codificar las operaciones de un repertorio de instrucciones es utilizar

algún criterio de óptimo. En este sentido tenemos dos alternativas:

a) Frecuencia de aparición en el programa Î optimización de memoria

b) Frecuencia de ejecución en el programa Î optimización del tráfico CPU-Memoria

La alternativa b) es la más interesante en la actualidad, pues prima la velocidad de ejecución sobre

4

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

la memoria .necesaria para almacenar el programa.

Para optimizar el CO se puede utilizar la codificación de Huffman que veremos con el siguiente

Ejemplo: Supongamos las siguientes frecuencias de ejecución de 7 tipos diferentes de

instrucciones:

Tipo de instrucciones

Frecuencia de ejecución

0.53

ADD

0.25

SUB

0.12

MUL

0.03

DIV

0.03

STA

0.02

LDA

0.02

JMP

Con CO de longitud fija se necesitarían 3 bits. Para obtener el código de Huffman procedemos de

la siguiente manera:

1) Se escriben en una columna las instrucciones y a su derecha su frecuencia de ejecución. Cada

elemento de la columna será un nodos terminal del árbol de decodificación.

2) Se unen las dos frecuencias menores de la columna anterior con sendos arcos, obteniéndose

un nuevo nodo cuyo valor será la suma de los nodos de procedencia.

3) Se repite el paso 2) hasta llegar a la raíz del árbol que tendrá valor 1

4) Comenzando en la raíz, asignamos 0 (1) al arco superior y 1 (0) al inferior hasta llegar a los

nodos terminales

5) Se obtiene el código de cada instrucción recorriendo el árbol de la raíz a la instrucción y

concatenando los valores de los arcos del camino

Para nuestro ejemplo tendremos lo siguiente:

ADD

0.53

SU B

0.25

MU L

0.12

DIV

0.03

0

0

1

0.47

0

0

0.22

0.06

STA

0.03

1

LDA

0.02

0

J MP

0.02

1

0

0.10

1

1

0.04

1

Tipo de instrucciones

Frecuencia de ejecución

Código de Huffman

ADD

SUB

MUL

DIV

STA

LDA

JMP

0.53

0.25

0.12

0.03

0.03

0.02

0.02

0

10

110

11100

11101

11110

11111

Longitud media del código resultante:

5

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

l m = ∑ f i × l i = 0.53 × 1 + 0.25 × 2 + 0.12 × 3 + 0.003 × 5 + 0.003 × 5 + 0.02 × 5 + 0.02 × 5 =

i

1.89 _ bits < 3 _ bits

2. Propiedades generales del direccionamiento.

Resolución

Es la menor cantidad de información direccionada por la arquitectura. El mínimo absoluto es un bit,

aunque esta alternativa la utilizan pocos procesadores, por ejemplo, el iAPX432 de Intel (1981)

Requiere un gran número de bits para expresar las direcciones de una cierta cantidad de

información y mucho tiempo para alinearlos correctamente. Lo más frecuente en los procesadores

actuales es utilizar resoluciones de 1 o 2 bytes. La resolución puede ser diferente para

instrucciones y datos aunque lo normal es que coincida.

Resolución

Instrucciones

Datos

MC68020

16

8

VAX-11

8

8

IBM/370

16

8

B1700

1

1

B6700

48

48

iAPX432

1

8

Orden de los bytes en memoria

El concepto de endian lo introdujo Cohen para expresar la forma como se ordenan los bytes de un

escalar de varios bytes.

• Modo big-endian: almacena el byte más significativo del escalar en la dirección más baja de

memoria

• Modo little-endian: almacena el byte más significativo del escalar en la dirección más alta de

memoria.

Ejemplo: el hexadecimal 12 34 56 78 almacenado en la dirección de memoria 184 tendrá la

siguiente organización en cada uno de los modos:

big-endian

184

12

185

34

186

56

187

78

little-endian

184

78

185

56

186

34

187

12

Alineación

Un objeto de datos de n bytes ubicado en la dirección de memoria D se dice que está alineado si

D mod n = 0

Objeto de datos direccionado (tamaño)

byte

media palabra (2 bytes)

palabra (4 bytes)

doble palabra (8 bytes)

Alineaciones correctas

0, 1, 2, 3, 4, 5, 6, 7, 8, 9

0, 2, 4, 6, 8, 10

0, 4, 8, 12

0, 8, 16

• Determinadas máquinas sólo permiten accesos alineados

• La falta de alineación implica complicaciones hardware

• Los programas con accesos alineados se ejecutan más rápidamente

• Para alinear datos se utiliza una red de alineación. En el caso de la figura para acceder a una

palabra no alineada serán necesarios 2 accesos para obtener la parte alta y baja

6

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

32 bits

32 bits

32 bits

32 bits

a la CPU

Espacios de direcciones

En un mismo procesador pueden diferenciarse hasta 3 espacios de direcciones diferentes:

• Espacio de direcciones de registros

• Espacio de direcciones de memoria

• Espacio de direcciones de entrada/salida

Los espacios de direcciones de memoria y entrada/salida de algunos procesadores están unificados

(un solo espacio), ocupando los puertos de E/S direcciones de ese espacio único. En estos procesadores

(ejemplo, 68000) no existen instrucciones específicas de E/S, para esta función se utilizan las de referencia a

memoria (carga y almacenamiento) con las direcciones asignadas a los puertos.

3. Modos de direccionamiento.

Los modos de direccionamiento determinan la forma como el operando (OPER) presente en las

instrucciones especifican la dirección efectiva (DE) del dato operando (DO) sobre el que se realiza la

operación indicada por CO.

Inmediato.

CO

OPER

DO = OPER

• El dato operando se ubica en la propia instrucción ==> no requiere accesos a memoria.

• Se suele utilizar para datos constantes del programa

• El tamaño está limitado por el número de bits de OPER

Implícito

CO

• El dato operando se supone ubicado en algún lugar específico de la máquina, por ejemplo, una pila

Directo (memoria o registros)

OPER = Dirección de memoria o de un registro

DE = OPER

DO = <OPER>

Memoria

o

Registros

CO

OPER

DO

7

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

• La especificación de un registro requiere menor número de bits que la de una posición de memoria

• El acceso a los registros es más rápido que a Memoria

• El direccionamiento directo a memoria se conoce como absoluto

• A veces se limita el número de bits de OPER limitando el acceso a sólo una parte de la memoria que

suele ser la correspondiente a las direcciones más bajas (página cero)

Indirecto (memoria)

OPER = Dirección de memoria

DE = <OPER>

DO = <<OPER>>

Memoria

CO

OPER

DE

DO

• Permite el tratamiento de una dirección de memoria como un dato

• Permite el paso por referencia de parámetros a subrutinas

• Permite referenciar un espacio mayor de direcciones

CO

2n-p direcciones

dirección

p bits

n-p bits

CO

dirección

p bits

2n-p direcciones

n-p bits

2n direcciones

dirección

n-bits

Indirecto (registro)

OPER = Dirección de un registro

DE = <OPER>

DO = <<OPER>>

Registros

CO

Memoria

OPER

DE

DO

Modos con desplazamiento.

Calculan la dirección efectiva (DE) sumando al contenido de un registro el operando declarado

8

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

en la instrucción (OPER) que se interpreta como un desplazamiento respecto al contenido del registro.

La distinta naturaleza del registro hace que se diferencien tres modos con desplazamiento. Todos

explotan la proximidad de los datos o instrucciones referenciadas para utilizar menor número de bits en

el campo OPER.

Direccionamiento base más desplazamiento

DE = <Registro base> + OPER; OPER = desplazamiento

• Se utiliza para la reubicación de datos y programas en memoria

Memoria

CO

OPER

+

DO

Registro Base

Ejemplo: A = B + C

Programa

LOAD RB,1; RD1

LOAD RB, 2; RD2

ADD RD1; RD2

STORE RD1; RB,0

(RD1 <-- <RB>+1)

(RD2 <-- <RB>+2)

(RD1 <-- <RD1> + <RD2>)

(A<RB>+0 <-- <RD1>)

<RB> + 1 = B

<RB> + 2 = C

<RB> + 0 = A

Memoria

RB

A

Registros de datos

B

RD1

C

RD2

Este programa podremos reubicarlo en memoria y siempre llevará a la dirección apuntada por el

registro base RB la suma de los contenidos de las dos direcciones siguientes.

Direccionamiento relativo

DE = <Contador de programa> + OPER; OPER = desplazamiento

• Se utiliza en las instrucciones de salto para conseguir la reubicación de estas instrucciones

• El desplazamiento en estas instrucciones tiene signo (c2) lo que significa que el salto relativo se

puede dar hacia posiciones anteriores o siguientes a la ocupada por la instrucción.

Memoria

CO

OPER

+

DO

Contador de Programa

9

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Direccionamiento indexado

DE = <Registro índice> + OPER; OPER = desplazamiento

• Se utiliza para recorrer estructuras lineales como los arrays

• Par facilitar su uso se suele complementar con el pre o post incremento o decremento del registro

índice

Memoria

CO

OPER

+

DO

Registro Indice

Resumen de los tipos de direccionamiento

Direccionamiento

instrucción

Indirecto (registro)

registro

Indirecto (memoria)

dirección

Indexado

registro

registro

memoria

dirección

operando

dirección

desplazamiento

+

operando

dirección

base

registro

dirección

+

operando

desplazamiento

Relativo

registro

dirección

+

operando

dirección

Modos compuestos

Veremos los modos compuestos analizando el repertorio de algunos procesadores.

Modos de direccionamiento del MC 68.X

CO

OPER

• Inmediato

DO = OPER

- enteros: 8, 16 y 32 bits

- reales: 32 bits (simple precisión), 64 bits (doble precisión) y 96 bits (precisión extendida)

• Directo

- Memoria o absoluto

DE = OPER, DO = <DE>, con OPER de 16 y 32 bits

10

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

- Registro

Ri = OPER, DO = <Ri>, con Ri cualquier registro

• Indirecto registro

- puro

DE = <Ri>, con Ri cualquier registro

Memoria

CO

OPER

Ri

DO

DE

- Indirecto registro con postincremento

DE = <Ri>;

Ri Å <Ri> + Inc,

CO

con Inc = 1, 2 ó 4 bytes

Memoria

OPER

Ri

+ Inc

DO

DE

- Indirecto registro con predecremento

Ri Å <Ri> - Dec,

DE = <Ri>,

CO

con Dec = 1, 2 ó 4 bytes

Memoria

OPER

Ri

- Dec

DO

DE

- Indirecto con desplazamiento (= base + desplazamiento)

DE = <Ri> + Despla

Memoria

CO

Despla

+

DO

DE

Ri

11

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

- Indirecto registro indexado (= base + desplazamiento indexado)

DE = <Ri> + <Rj>xEscala + Despla,

con Escala = 1, 2, 4, 8 bytes

Memoria

Escala

CO

Despla

x

+

DO

DE

Rj

Ri

• Indirecto memoria

- Postindexado (= base + desplazamiento indirecto indexado + desplazamiento)

DE = <<Ri> + despla1> + <Rj>xEscala + Despla2

CO

Despla1

Despla2

Memoria

+

DIR

DE

Ri

DO

Rj

x

+

Escala

- Preindexado (base + desplazamiento indexado indirecto + desplazamiento)

DE = <<Ri> + Despla1 + <Rj>xEscala> + Despla2

12

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

CO

Despla1

Despla2

+

Memoria

Ri

DIR

+

+

DE

Rj

DO

x

Escala

• Relativo

- Básico

DE = <CP> + Despla

Memoria

CO

Despla

+

DO

DE

CP

- Indexado con desplazamiento

DE = <CP> + <Rj>xEscala + Despla

Escala

x

Memoria

CO

Despla

+

DO

DE

Rj

CP

13

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

- Indirecto memoria postindexado

DE = <<CP> + Despla1> + <Rj>xEscala + Despla2

CO

Despla1

Despla2

Memoria

+

DIR

DE

CP

DO

Rj

x

+

Escala

- Indirecto memoria preindexado

DE = <<CP> + Despla1 + <Rj>xEscala> + despla2

CO

Despla1

Despla2

+

Memoria

CP

+

Rj

DIR

+

DE

DO

x

Escala

Modos de direccionamiento del MIPS R-2000

• Inmediato

• Registro

LA = R

• Relativo

DE = <PC> + Despla

14

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

• Indirecto registro con desplazamiento (= base + desplazamiento)

DE = <Ri> + Despla

Modos de direccionamiento del Pentium II

CO

A

Registros de uso general

Registro base

Registro índice

B

0, 8 ó 32 bits

I

A

Escala

(1,2,4,8)

X

Memoria

+

Registro de segmento

SR

DE

LA

+

segmento

(6 registros SR)

Paginación

• Inmediato

DO = A (1,2,4 bytes)

• Registro

LA = R, DO = <R> (LA = dirección lineal)

• Desplazamiento

LA = <SR> + A

• Base

LA = <SR> + <B>

• Base + desplazamiento

LA = <SR> + <B> + A

• Indexado

LA = <SR> + <I>xEscala + A

• Base + desplazamiento indexado

LA = <SR> + <B> + <I> + A

• Base + desplazamiento indexado escalado

LA = <SR> + <B> + <I>xEscala + A

• Relativo

LA = <PC> + A

15

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

4. Soporte de los modos de direccionamiento a los lenguajes de alto nivel

Visibilidad en C

Un programa escrito en C no es más que una colección de subprogramas (funciones) en

idéntico nivel, dentro del programa principal (Main). Estas funciones pueden llamarse entre sí, incluso

de forma recursiva. Las variables locales definidas en una función son visibles sólo dentro de la función.

En cambio las variables globales se definen fuera de la funciones (en la función Main) y pueden ser

referenciadas desde cualquiera de ellas.

Las variables locales de una función se asignan dinámicamente Estudiaremos ahora los

modos de direccionamiento más adecuados para satisfacer los requerimientos de los lenguajes de alto nivel.

Estos modos reducirán al mínimo el número de instrucciones requeridas para acceder a los elementos de las

diferentes estructuras de datos (array, record, etc.) que soportan estos lenguajes, es decir, para calcular sus

direcciones efectivas. Estos lenguajes presentan una estructura de bloques e incorporan el concepto de

visibilidad de las variables del programa, es decir, las reglas de acceso a las variables de cada uno de los

bloques.

, es decir, cada vez que se activa la función. La asignación tiene lugar dentro de un registro de

activación (RA) que se ubica en la pila asociada al programa. Dada la naturaleza recursiva de las

llamadas, pueden existir en la pila más de un RA para la misma función (tantos como llamadas).

Supongamos el siguiente perfil de progrma C:

Main( )

{

.

.

.

... = ... fe(...) ...

.

.

.

}

fa (...)

{

.

.

.

fb (...)

{

.

.

.

... = ... fb(...) ...

.

.

.

... = ... fc(...) ...

.

.

.

}

fc (...)

{

.

.

.

... = ... fc(...) ...

.

.

.

... = ... fb(...) ..

.

.

.

}

}

La estructura de este programa sería la siguiente:

fd (...)

{

.

.

.

}

fe (...)

{

.

.

.

... = ... fc(...) ...

.

.

.

}

main

fa

fb

fc

fd

fe

Supongamos que tiene lugar la siguiente secuencia de llamadas:

main Æ fe Æ fc Æ fc Æ fb Æ fb Æ fc

En la pila del programa se ubican los registros de activación correspondientes a cada una de estas

llamadas, tal como se muestra en la siguiente figura, donde se ha sombreado las variables que pueden

ser accedidas desde la tercera activación de la función fc: las globales y las locales a esta tercera

llamada. Para realizar el acceso se dispone de sendos registros que apuntan a cada uno de estos RA,

el Puntero al Registro de Activación Global (PRAG) y el Puntero al Registro de Activación Local (PRAL)

16

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

RA main

RA fe

PRAG

Puntero al Registro de Activación Global

RA fc

(1ª llamada)

RA fc

(2ª llamada)

Registros de Activación

visibles desde la última

llamada a fc

RA fb

(1ª llamada)

RA fb

(2ª llamada)

RA fc

(3ª llamada)

PRAL

Crecimiento de la PILA

Puntero al Registro de Activación Local

Visibilidad en Pascal

En los lenguajes de tipo Pascal un bloque puede ser un procedure o una function, y el concepto

de visibilidad adquiere una estructura anidada. Los bloques de un programa de este tipo presentan una

estructura jerárquica y la visibilidad de variables desde la llamada a un bloque se extiende a todos los

bloques (últimas llamadas) en el camino hasta la raíz (main)

main

Ba

Bc

Bb

Bd

Be

Bf

Bh

Bi

Bg

program main(..)

procedure a

begin

procedure c

begin

...

end

procedure d

begin

...

end

end

procedure b

begin

procedure e

begin

... function h (..)

end

procedure f

begin

... function i (..)

end

procedure g

begin

...

end

end

end

Secuencia de llamada: main Æ Ba Æ Bb Æ Bb Æ Bf Æ Be Æ Bh Æ Bh

17

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

RA main

RA Ba

PRAG

RA Bb

(1ª llamada)

RA Bb

(2ª llamada)

Registros de Activación

visibles desde la última

llamada al bloque Bh

RA Bf

RA Be

Display del RA Bh

RA Bh

(1ª llamada)

RA Bh

(2ª llamada)

PRAL

El display de un RA contiene un puntero a cada RAi visible desde RA

Acceso a variables escalares locales o globales (contenido)

RA main

Despla

PRA G

Variable g lobal

RA

(procedimiento

en ejecución)

Despla

PRA L

Variable local

Variables locales:

DE = <PRAL> + despla Î direccionamiento base + desplazamiento

Variables globales:

DE = <PRAG> + despla Î direccionamiento base + desplazamiento

18

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Acceso a variables escalares no locales (contenido)

main

Ba

Bb

Bl

Bc

Bd

Secuencia de llamada: main Æ Ba Æ Ba Æ Bb Æ Bc Æ Bd

RA main

RA Ba

PRAG

(1ª llamada)

RA Ba

Despla 2

(2ª llamada)

RA Bb

RA Bc

Ubicación del dato accedido

Despla 1

RA Bd

display

PRAL

DE = <<PRAL> + Despla1> + Despla 2 Î

direccionamiento base + desplazamiento indirecto + desplazamiento

19

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Acceso a variables escalares locales (dirección)

Var. referenciada

RA proc. Ejec.

Despla

Puntero local

PRAL

DE = <<PRAL> + Despla> Î

direccionamiento base + desplazamiento indirecto

Acceso a variables escalares no locales (dirección)

Var. referenciada

RA proc. refer.

Despla 2

Referencia a var.

Inicio RA referenc.

Despla 1

display

RA proc. Ejec.

PRAL

DE = <<<PRAL> + Despla1> + Despla 2> Î

direccionamiento base + desplazamiento indirecto + desplazamiento indirecto

20

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Acceso a variables de tipo array locales (contenido)

RA proc. Ejec.

1º elemento

Factor_escala (=1,2,4,8)

Despla

Indexación

array

X

RX

n-simo elemento

PRAL

DE = <PRAL> + Despla + <RX>factor_escala Î

direccionamiento base + desplazamiento indexado

Acceso a variables de tipo array no locales (contenido)

RA proc. referen.

1º elemento

Factor_escala (=1,2,4,8)

Despla 2

Indexación

array

X

RX

n-simo elemento

Despla 1

Inicio RA referenc.

display

RA proc. Ejec.

PRAL

DE = <<PRAL> + Despla 1> + Despla 2 + <RX>factor_escala Î

direccionamiento base + desplazamiento indirecto + desplazamiento indexado

21

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Acceso a variables de tipo array locales (dirección)

Factor_escala (=1,2,4,8)

1º elemento

Indexación

array

X

RX

n-simo elemento

RA proc. Ejec.

Despla

Puntero local

PRAL

DE = <<PRAL> + Despla > + <RX>factor_escala Î

direccionamiento base + desplazamiento indirecto indexado

Acceso a variables de tipo record locales (contenido)

RA proc. ejec.

1º campo

Despla 1

Despla 2

record

n-simo campo

PRAL

DE = <PRAL> + Despla 1 + Despla 2 Î

direccionamiento base + desplazamiento

Despla 1 = dirección e inicio del record

(conocido en tiempo de compilación)

Despla 2 = posición en record del campo accedido

(conocido en tiempo de compilación)

22

Estructura de Computadores, Facultad de Informática, UCM, Curso 04-05

Acceso a variables de tipo record anidados locales (contenido)

RA proc. ejec.

1º campo de RR(x)

1º campo de R (y)

record RR

Despla 1