GUIA DE CATEDRA MATERIA Electrónica Digital 1

Anuncio

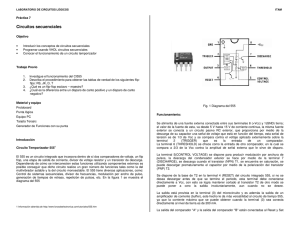

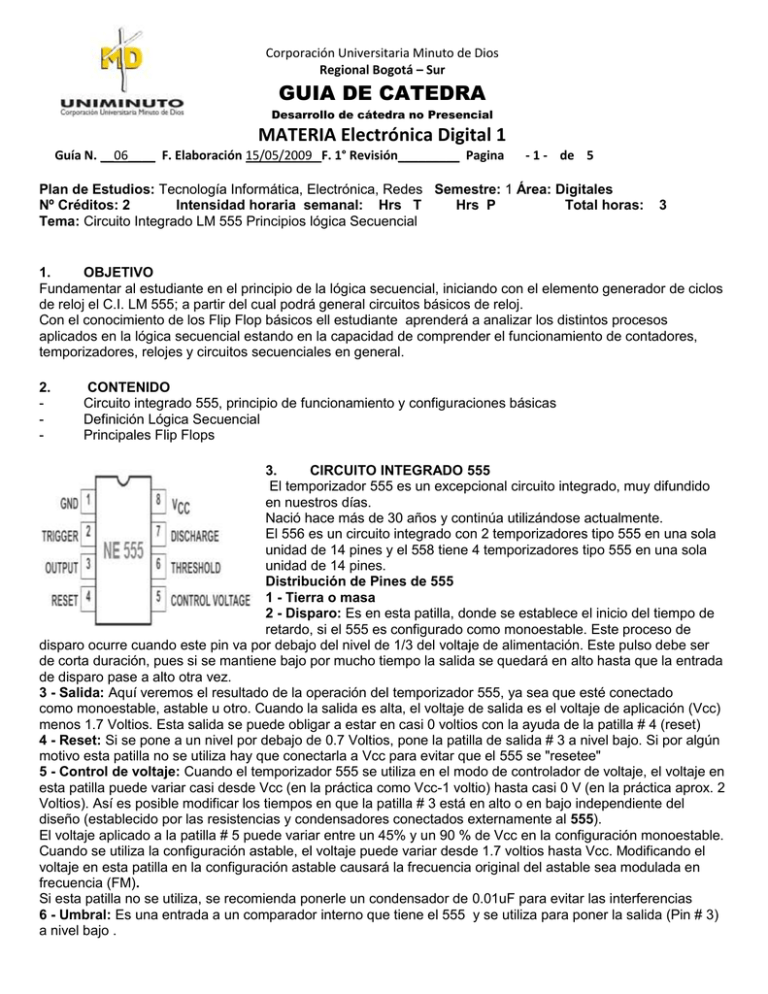

Corporación Universitaria Minuto de Dios Regional Bogotá – Sur GUIA DE CATEDRA Desarrollo de cátedra no Presencial MATERIA Electrónica Digital 1 Guía N. __06____ F. Elaboración 15/05/2009 F. 1° Revisión_________ Pagina - 1 - de 5 Plan de Estudios: Tecnología Informática, Electrónica, Redes Semestre: 1 Área: Digitales Nº Créditos: 2 Intensidad horaria semanal: Hrs T Hrs P Total horas: Tema: Circuito Integrado LM 555 Principios lógica Secuencial 3 1. OBJETIVO Fundamentar al estudiante en el principio de la lógica secuencial, iniciando con el elemento generador de ciclos de reloj el C.I. LM 555; a partir del cual podrá general circuitos básicos de reloj. Con el conocimiento de los Flip Flop básicos ell estudiante aprenderá a analizar los distintos procesos aplicados en la lógica secuencial estando en la capacidad de comprender el funcionamiento de contadores, temporizadores, relojes y circuitos secuenciales en general. 2. - CONTENIDO Circuito integrado 555, principio de funcionamiento y configuraciones básicas Definición Lógica Secuencial Principales Flip Flops 3. CIRCUITO INTEGRADO 555 El temporizador 555 es un excepcional circuito integrado, muy difundido en nuestros días. Nació hace más de 30 años y continúa utilizándose actualmente. El 556 es un circuito integrado con 2 temporizadores tipo 555 en una sola unidad de 14 pines y el 558 tiene 4 temporizadores tipo 555 en una sola unidad de 14 pines. Distribución de Pines de 555 1 - Tierra o masa 2 - Disparo: Es en esta patilla, donde se establece el inicio del tiempo de retardo, si el 555 es configurado como monoestable. Este proceso de disparo ocurre cuando este pin va por debajo del nivel de 1/3 del voltaje de alimentación. Este pulso debe ser de corta duración, pues si se mantiene bajo por mucho tiempo la salida se quedará en alto hasta que la entrada de disparo pase a alto otra vez. 3 - Salida: Aquí veremos el resultado de la operación del temporizador 555, ya sea que esté conectado como monoestable, astable u otro. Cuando la salida es alta, el voltaje de salida es el voltaje de aplicación (Vcc) menos 1.7 Voltios. Esta salida se puede obligar a estar en casi 0 voltios con la ayuda de la patilla # 4 (reset) 4 - Reset: Si se pone a un nivel por debajo de 0.7 Voltios, pone la patilla de salida # 3 a nivel bajo. Si por algún motivo esta patilla no se utiliza hay que conectarla a Vcc para evitar que el 555 se "resetee" 5 - Control de voltaje: Cuando el temporizador 555 se utiliza en el modo de controlador de voltaje, el voltaje en esta patilla puede variar casi desde Vcc (en la práctica como Vcc-1 voltio) hasta casi 0 V (en la práctica aprox. 2 Voltios). Así es posible modificar los tiempos en que la patilla # 3 está en alto o en bajo independiente del diseño (establecido por las resistencias y condensadores conectados externamente al 555). El voltaje aplicado a la patilla # 5 puede variar entre un 45% y un 90 % de Vcc en la configuración monoestable. Cuando se utiliza la configuración astable, el voltaje puede variar desde 1.7 voltios hasta Vcc. Modificando el voltaje en esta patilla en la configuración astable causará la frecuencia original del astable sea modulada en frecuencia (FM). Si esta patilla no se utiliza, se recomienda ponerle un condensador de 0.01uF para evitar las interferencias 6 - Umbral: Es una entrada a un comparador interno que tiene el 555 y se utiliza para poner la salida (Pin # 3) a nivel bajo . Corporación Universitaria Minuto de Dios Regional Bogotá – Sur GUIA DE CATEDRA Desarrollo de cátedra no Presencial MATERIA Electrónica Digital 1 Guía N. __06____ F. Elaboración 15/05/2009 F. 1° Revisión_________ Pagina - 2 - de 5 7 - Descarga: Utilizado para descargar con efectividad el condensador externo utilizado por el temporizador para su funcionamiento. 8 - V+: También llamado Vcc, es el pin donde se conecta el voltaje de alimentación que va de 4.5 voltios hasta 16 voltios (máximo). Hay versiones militares de este integrado que llegan hasta 18 Voltios El temporizador 555 se puede conectar para que funcione de diferentes maneras, entre las más importantes están: multivibrador astable y como multivibrador monoestable. Oscilador Astable El periodo T = t1 + t2 y la frecuencia: f = 1 / T Recordar que el período es el tiempo que dura la señal desde que se inicia en un momento dado hasta que éste se vuelve a repetir. En este modo se genera una señal cuadrada oscilante de frecuencia: F = 1/T = 1.44 / [C*(Ra+2*Rb)] La señal cuadrada tendrá como valor alto Vcc (aproximadamente) y como valor bajo 0V. Si se desea ajustar el tiempo que está a nivel alto y bajo se deben aplicar las fórmulas: Salida a nivel alto: T1 = 0.693*(Ra+Rb)*C Salida a nivel bajo: T2 = 0.693*Rb*C Para que el circuito oscile es necesario que se se cumplan ciertos rangos para los valores de las resistencias y el condensador, los cuales se relacionan a continuación. R1 ≥ 1 kΩ R1 + R2 ≤ 6.6 MΩ C ≥ 500 pF Oscilador Monoestable Cuando la señal de disparo está a nivel alto (ej. 5V con Vcc 5V) la salida se mantiene a nivel bajo (0V), que es el estado de reposo. Una vez se produce el flanco descendente de la señal de disparo y se pasa por el valor de disparo, la salida se mantiene a nivel alto (Vcc) hasta transcurrido el tiempo determinado por la ecuación: T = 1.1*R1*C1 Es recomendable, para no tener problemas de sincronización que el flanco de bajada de la señal de disparo sea de una pendiente elevada, pasando lo más rápidamente posible a un nivel bajo (idealmente 0V). NOTA: en el modo monoestable, el disparo debería ser puesto nuevamente a nivel alto antes que termine la temporización Corporación Universitaria Minuto de Dios Regional Bogotá – Sur GUIA DE CATEDRA Desarrollo de cátedra no Presencial MATERIA Electrónica Digital 1 Guía N. __06____ F. Elaboración 15/05/2009 F. 1° Revisión_________ Pagina - 3 - de 5 Flip Flop Los Flip-Flop o Biestable, como también se le conoce, son circuitos secuénciales constituidos por puertas lógicas capaces de almacenar un bit, que es la información binaria más elemental. Existe una gran variedad de biestables, los cuales se clasifican en: Asíncronos: R-S ; J-K ; T Síncronos: Activados por Nivel: R-S ; J-K ; D Activados por Flanco: Edgetriggered y Master-Slave (maestro-esclavo) R-S; D ; J-K ; T Biestable Asíncronos R-S Posee dos entradas denominadas Reset (R) y Set (S) y dos salidas, Q1 y Q2. Este dispositivo se puede construir mediante dos puertas NOR o dos puertas NAND, a continuación vemos su símbolo grafico y su tabla de verdad. Biestable Sincrono D Activado Por Nivel El flip-flop D (datos) es una ligera modificación del flip-flop SR. Un flip-flop SR se convierte a un flip-flop D insertando un inversor entre S y R y asignando el símbolo D a la entrada única. La entrada D se muestra durante la ocurrencia de una transición de reloj de 0 a 1. Si D = 1, la salida del flip-flop va al estado 1, pero si D = 0, la salida del flip-flop va a el estado 0. Biestable Asíncrono J-K El biestable asíncrono J-K es como el R-S, al cual se le ha eliminado el defecto de funcionamiento cuando las dos entradas valen 1. En este caso Q1 y Q2 siempre son complementarias Corporación Universitaria Minuto de Dios Regional Bogotá – Sur GUIA DE CATEDRA Desarrollo de cátedra no Presencial MATERIA Electrónica Digital 1 Guía N. __06____ F. Elaboración 15/05/2009 F. 1° Revisión_________ Pagina - 4 - de 5 Flip Flop T El flip-flop T se obtiene del tipo JK cuando las entradas J y K se conectan para proporcionar una entrada única designada por T. El flip-flop T, por lo tanto, tiene sólo dos condiciones. Cuando T = 0 ( J = K = 0) una transición de reloj no cambia el estado del flip-flop. Cuando T = 1 (J = K = 1) una transición de reloj complementa el estado del flip-flop. Su unidad básica se dibuja a continuación que, como actúa por "niveles" de amplitud (0-1) recibe el nombre de Flip-Flop T activado por nivel (FF-T-AN). Cuando no se especifica este detalle es del tipo Flip-Flop T maestroesclavo (FF-T-ME). Su ecuación y tabla de funcionamiento son qQ = T Biestable Sincronos Activados por Flanco Como hemos comprobado en los biestables activados por nivel los cambios producidos en las entradas, mientras permanece la señal de reloj en nivel activo, se reflejan en la salida. Esta forma de funcionamiento puede ocasionar problemas cuando la conmutación en las señales de entradas se realiza con una frecuencia elevada. Reducir el tiempo de duración del nivel activo no es una solución suficiente, ya que este, por otra parte, debe ser lo suficientemente largo como para permitir la conmutación de los dispositivos más lentos que forman parte del sistema. Los FLIP-FLOPS integrados adoptan algunas de las dos soluciones que se describen a continuación: a) Configuración EDGE-TRIGGERED. b) Configuración MASTER-SLAVE Master-Slave: Esta constituido por dos etapas. Cuando la señal de reloj pasa de nivel cero (0) a nivel uno (1), la información presente en las entradas R-S del circuito entra al primer biestable, denominado Master, a través de las puertas Y1 e Y2. En este estado de la señal de reloj las entradas del segundo biestable, llamado Slave, permanecen cerradas, ya que el valor de salidas de las puertas Y3 e Y4 es cero (0). Al pasar la señal de reloj a nivel cero (0), la información almacenada en el Master pasa al Slave porque ahora esta señal abre las puertas Y3 e Y4. En estas circunstancias las puertas Y1 e Y2 permanecerán cerradas y, en consecuencia, los cambios producidos en las entradas principales del circuito no seran captados por el Master. Corporación Universitaria Minuto de Dios Regional Bogotá – Sur GUIA DE CATEDRA Desarrollo de cátedra no Presencial MATERIA Electrónica Digital 1 Guía N. __06____ F. Elaboración 15/05/2009 F. 1° Revisión_________ Pagina - 5 - de 5 4. ACTIVIDADES DE INVESTIGACIÓN En laboratorio se deberán realizar montajes prácticos del funcionamiento del CI 555 en sus modos de Astable y Monoestable verificando con osciloscopio la frecuencia previamente diseñada. 5. CRITERIO E INSTRUMENTO DE EVALUACION La práctica de laboratorio verificara el aprendizaje de la guía, conjuntamente con el manejo del CI 555 y los Flip Flop respectivamente vistos 6. - BIBLIOGRAFIA Mabel Gonzales Urmachea Circuitos Digitales: Flip Flops http://www.monografias.com/trabajos14/flipflop/flipflop.shtml , consulta hecha el 15 de mayo de 2009 Sistemas Digitales, Editorial Prentice Hall, Ronald J. Tocci 2007, consulta hecha el 15 de mayo de 2009 Electrónica, teoría de Circuitos y Dispositivos Electrónicos, Editorial Prentice Hall, BoylestadNashelsky Octava Edición consulta hecha el 15 de Septiembre de 2008 http://galeon.hispavista.com/edigi/flipflop.htm; Consulta hecha el 15 de mayo de 2009 http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/laboratorios/070101.htm, Consulta hecha el 15 de mayo de 2009 Elaborado por: Juan Carlos Botello Juanbotello01@yahoo.com