ELEVADOR DE TENSIÓN PARA CIRCUITOS CMOS N-WELL

Anuncio

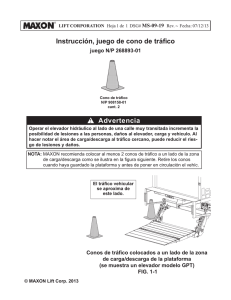

Título : "ELEVADOR DE TENSIÓN PARA CIRCUITOS CMOS N-WELL " Autores: Ing. Alejandro de La Plaza, Profesor Universidad de Buenos Aires Ing. Héctor Fabián Kirschenbaum, Estudiante de doctorado Contacto: Ing. Alejandro de La Plaza Dirección : Laboratorio de Microelectrónica Facultad de Ingeniería de la Universidad de Buenos Aires Paseo Colon 850, CP 1063, Buenos Aires, ARGENTINA. Teléfono: 54-1-4343-0891, int 263 y 167. Mail: a.plaza@ieee.org < Alejandro de La Plaza> hkirsc@fi.uba.ar <Héctor Fabián Kirschenbaum> Resumen El uso de elevadores de tensión integrados se debe a los dispositivos EPROM de compuerta-flotante, y a los circuitos de muy baja tensión de alimentación. En el primer caso esta necesidad esta justificada por el hecho de que una segunda fuente de alimentación para el ciclo de escritura es inaceptable. En el segundo caso muchas funciones no son bien resueltas con un potencial bajo y por lo tanto se requiere de uno superior. Para obtener una tensión a partir de otra inferior se utilizan principalmente dos métodos, a través de circuitos de elevación de carga y a través de reguladores de conmutación. La principal diferencia entre ambos circuitos es el elemento usado para almacenar energía. En el primer caso este elemento es un capacitor y en el segundo caso es un inductor o transformador. Cuando la potencia requerida es pequeña los capacitores requeridos por los circuitos de elevación de carga pueden ser lo suficientemente pequeños como para que todo el circuito elevador sea implementado en un único integrado. Por lo tanto los circuitos elevadores de tensión por elevación de carga son los ampliamente utilizados en los circuitos de memoria no-volátil y también en la mayoría de los dispositivos EEPROM con alimentación exclusiva de 5v disponibles en la actualidad. Se ha desarrollado un nuevo elevador de tensión integrado para su utilización tanto en memorias EEPROM como en circuitos de muy baja tensión utilizando el concepto de elevación de carga pero de una nueva forma que permite la integración de los capacitores con tecnología CMOS N-Well estándar. También permite el control de la tensión sobre todos los dispositivos del elevador. Se obtuvieron valores de eficiencia similares a los del elevador de Dickson. El elevador ha sido fabricado a través de MOSIS con la tecnología nombrada anteriormente. Summary The on-chip high-voltage generators are used in non-volatile memory circuits and in very low voltage circuits. In the first case they need it because a second voltage source for the write cycle is unacceptable. In the second case many functions are not well solved by low voltage source, so a high voltage source is required. In order to obtain a high voltage from a low voltage two methods are preferred. The charge pump one, and the conmutation regulators. The main difference between them is the storage element. These are a capacitor and an inductor or transformer respectively. When the power is low, the capacitors that are used in the pump charge circuits are small enough that allow all the circuit can be integrated. For this reason the charge pump circuits are widely use in the non-volatile memory circuits and also in the most of the EEPROM devices with 5v voltage available now. A new high voltage generator has been developed it can be used for non-volatile memory circuits and for very low voltage circuits. It uses the concept of charge pump but in a new way. This allowed the circuits' integration with standard Cmos N-Well technology. The Circuit has been fabricated through Mosis with the technology named above. Elevador De Tensión Integrado Para Circuitos CMOS N-WELL Alejandro de La Plaza, Héctor Fabián Kirschenbaum Abstracto - Se desarrolló un multiplicador de tensión integrado en el cual solo se requiere una sola fase. Con esta técnica la tensión desarrollada sobre los capacitores no supera a la alimentación. También se describe un circuito equivalente del elevador. Este circuito puede ser utilizado como fuente para circuitos de muy bajo nivel de operación. Introducción La utilización de generadores de alta tensión integrados para la escritura de memorias EEPROM es algo muy utilizado y en constante desarrollo debido a la reducción continua de la alimentación de los integrados. Esta reducción también obliga a la utilización de elevadores integrados como fuente de alimentación de los circuitos. La alta tensión generada, al someter a los dispositivos integrados a tensiones superiores a su tolerancia, dificulta su integración con tecnología estándar o en forma económica. La nueva configuración que se presenta aquí permite la implementación sin que ningún dispositivo sea sometido a tensiones superiores a la alimentación. También utiliza solo un clock. Todo esto se logra recurriendo a un nuevo método de transferencia de carga. Principio de Funcionamiento estos deben soportar el total de tensión desarrollada a lo largo del elevador y que se deben utilizar dos señales de clock en contrafase y no superpuestas, esto último para reducir la tensión de ondulación; aunque la mayoría de las aplicaciones práctica basadas en este circuito exigen 4 fases [2]. Debido a la alta tensión a la que son sometidos los capacitores no se los puede integrar usando la capacitancia entre gate y sustrato de un transistor MOS de baja tensión y por lo tanto ocupan un área muy grande. Para solucionar estas limitaciones se presenta el multiplicador de tensión de la figura 2. La idea general de este multiplicador es cargar simultáneamente una batería de capacitores, C1, C2. . . Ci. . . CN, para después ponerlos en serie, formando una cadena. Este concepto es tratado por Masaaki en [3]. Si se elimina el camino de descarga de los capacitores, la tensión en los extremos de la cadena es igual a la suma de la tensión entre bornes de cada capacitor. Parte de esta carga se transfiere por redistribución en cada ciclo a un capacitor de salida. El circuito posee dos estados, el de carga y el de redistribución. En el ciclo de carga los capacitores adquieren la tensión de alimentación. En el ciclo de redistribución los capacitores son puestos en serie. Estos ciclos están definidos por un solo clock. Si cada capacitor se carga a la tensión de alimentación, Vcc, cuando se ponen todos ellos en paralelo, la tensión de la cadena es: En principio se puede generar voltajes superiores a la tensión de alimentación en forma integrada utilizando el circuito desarrollado por Dickson [1], que se muestra en la figura 1. Su operación es bien conocida y solo se remarca que por estar los capacitores dispuestos en paralelo Vcad = (N + 1) ⋅ Vcc − Vd Figura_2: Esquema del elevador de tensión Figura_1:Circuito de Dickson (1) Figura_2: Esquema del elevador de tensión En donde N es la cantidad de capacitores en la cadena, y él termino extra corresponde a la alimentación, ya que el primer capacitor de la cadena se conecta a Vcc; Vd es la caída en el diodo. Como la carga entregada por la cadena en cada ciclo de clock es: Q(c arg a ) = COUT // Ce V V N ⋅ ( cad − out ) estas se deduce un modelo del elevador mostrado en la figura 3. (2) La corriente entregada por el multiplicador a una frecuencia de clock esta dada por Figura_3 : Modelo del elevador de tensión I OUT = f ⋅ COUT // Ce ⋅ (Vcad − Vout ) N (3) Donde vout es la tensión de salida del elevador. Por lo tanto la expresión de la salida con una carga dada por IOUT es la siguiente Vout = (N + 1) ⋅ Vcc − VD − IOUT La tensión de ondulación de salida esta determinada, como muestra el modelo de la figura 4, por la descarga del capacitor de salida cuando debe mantener una corriente de salida IOUT. (4) f ⋅ COUT // Ce N Con N: Cantidad de etapas VD : Tensión de barrera del diodo de salida F : Frecuencia del clock Figura_4 : Modelo para la tensión de ondulación Podemos volver a escribir la ultima como Vout = VO − I OUT ⋅ RS (5) Con VO = (N + 1) ⋅ Vcc − VD (6) RS = 1 Ce // C f N OUT ⋅ (7) La corriente se cierra exclusivamente por el capacitor de salida cuando el elevador esta en su ciclo de carga y por el capacitor de salida y el elevador cuando este último esta en su ciclo de puesta en serie, un gráfico de la corriente se muestra en la figura 5. Por lo tanto la tensión de ondulación esta dada por VR ≅ I OUT T I OUT ⋅ + C OUT 2 C e N + C OUT T ⋅ (8) 2 Con T: Periodo del clock de alimentación. Siendo Vo y Rs el voltaje de salida a circuito abierto y la resistencia serie respectivamente. De Figura_7 : Diagrama temporal del clock Figura_5 : Diagrama de la corriente Esto se logra mediante el circuito de la figura 8. De esta expresión se deduce que la tensión de ondulación y la tensión de salida dependen linealmente de I OUT, alcanzando VOUT su valor máximo y la tensión de ondulación siendo nula con I OUT = 0 independientemente del valor de las otras variables. Implementación con tecnología CMOS En la configuración que se presenta en la figura 6 se muestra la implementación desarrollada, con las llaves realizadas con transistores NMOS y PMOS. Los capacitores se implementan con transistores utilizando la capacitancia entre gate y sustrato. El circuito utiliza transistores NMOS como llaves de control de carga de los capacitores. Para activar las llaves NMOS que conectan al capacitor con la masa y la alimentación simultáneamente se debe contar con un único clock pero con dos ramas desplazadas por una tensión continua, como se muestra en la figura 7. Figura_8 : Circuito del clock Entonces al entrar en corte los transistores NMOS dejan al capacitor aislado y sin camino de descarga. Para conectar estos capacitores en serie se usan transistores PMOS. Para controlar las compuertas PMOS el clock solo activa directamente a Mcp4, que por ser PMOS se activa cuando el NMOS se desactiva. La secuencia de cambio de estado de carga a redistribución prosigue después de la activación de Mc4 con la elevación del potencial del drain de Mn8, provocada por la activación de Mc4, y por lo tanto del source del Mn7. Debido a que Mcc4 no tiene por donde descargarse, este potencial pasa a Figura_6: Circuito del elevador estar en el orden de 2vcc. Al elevarse el potencial en el source de Mn7 se habilita a Mc3 que eleva la tensión en el drain de Mn6 y entonces en el source de Mn5 hay 3 Vcc. Esto activa la compuerta siguiente y así se va repitiendo el proceso hasta llegar a la última etapa que tiene como tensión de salida (N+1)Vcc donde N es la cantidad de etapas. Verificación del circuito La simulación se realiza por medio de SPICE. Primero se simula el elevador sin carga dando como resultado la salida mostrada en la figura 9, donde alcanza el valor predicho por (4). corriente de carga, tal como predicen las ecuaciones (4) y (8). Conclusión Se presenta un circuito elevador de tensión que permite el uso de capacitores de baja tensión que puede implementarse con tecnología Cmos N-Well estandar. El uso de un clock único permite optimizar la operación y simplifica el diseño. Referencias [1] Dickson, John F.; "On chip High-Voltage Generation in NMOS Integrated Circuits Using an Improved Voltage Multiplier technique"; IEEE Journal of solid-state circuits; vol SC-11; No 3; June 1976 [2] Christl Lauterbach, Werner Weber, Dirk Romer, "Charge Sharing and New Clocking Scheme for Power Efficiency and Electromagnetic Emission Improvement of Boosted Charge Pumps", IEEE Journal of solid-state circuits, vol 35, No 5, May 2000. [3] Maasaki Mihara, Yasushi Terada, Michihiro Yamada, "Negative Heap Pump for Low Voltage Operation Flash Memory", IEEE 1996 Symposium on VLSI Circuits Digest of Technical Papers, p. 7677. Figura_9 : Salida simulada del elevador sin carga A continuación se realizan mediciones variando la corriente de salida pero manteniendo fija la frecuencia y capacidad de salida. En estas mediciones se centra la atención en VOUT y la tensión de ondulación. El resultado de las mediciones se detalla en la tabla 1. COUT = 10p; Frecuencia = 10Mhz IOUT VOUT VOUT Vr Vr Amper Simulado Calculado Simulado Calculado 1u 14.28 14.35 6m 5m 5u 14 14.15 26m 25m 20u 13.4 13.4 .135 0.1 100u 9,75 9.4 0.73 .5 Tabla 1 : Mediciones realizadas Se observa como la tensión de ondulación aumenta a medida que aumenta la carga del elevador, también se observa como la salida del elevador disminuye a medida que aumenta la