Examen IC 2009-2010-Q2-nivell-B_solucio

Anuncio

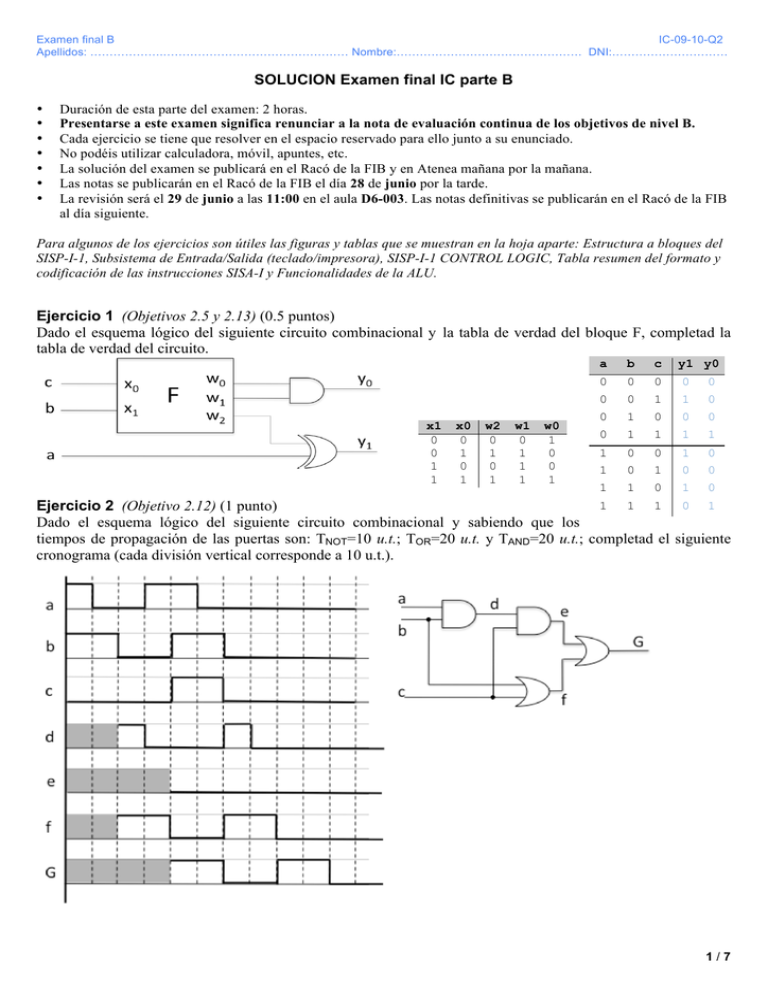

Examen final B IC-09-10-Q2 Apellidos: ……………….………………………………………… Nombre:………………………………………… DNI:………………………… SOLUCION Examen final IC parte B • • • • • • • Duración de esta parte del examen: 2 horas. Presentarse a este examen significa renunciar a la nota de evaluación continua de los objetivos de nivel B. Cada ejercicio se tiene que resolver en el espacio reservado para ello junto a su enunciado. No podéis utilizar calculadora, móvil, apuntes, etc. La solución del examen se publicará en el Racó de la FIB y en Atenea mañana por la mañana. Las notas se publicarán en el Racó de la FIB el día 28 de junio por la tarde. La revisión será el 29 de junio a las 11:00 en el aula D6-003. Las notas definitivas se publicarán en el Racó de la FIB al día siguiente. Para algunos de los ejercicios son útiles las figuras y tablas que se muestran en la hoja aparte: Estructura a bloques del SISP-I-1, Subsistema de Entrada/Salida (teclado/impresora), SISP-I-1 CONTROL LOGIC, Tabla resumen del formato y codificación de las instrucciones SISA-I y Funcionalidades de la ALU. Ejercicio 1 (Objetivos 2.5 y 2.13) (0.5 puntos) Dado el esquema lógico del siguiente circuito combinacional y la tabla de verdad del bloque F, completad la tabla de verdad del circuito. x1 0 0 1 1 x0 0 1 0 1 w2 0 1 0 1 w1 0 1 1 1 w0 1 0 0 1 a b c y1 y0 0 0 0 0 0 1 0 1 0 0 0 1 0 0 0 0 1 1 1 1 1 1 0 0 0 1 1 0 0 0 1 1 0 1 0 1 Ejercicio 2 (Objetivo 2.12) (1 punto) Dado el esquema lógico del siguiente circuito combinacional y sabiendo que los tiempos de propagación de las puertas son: TNOT=10 u.t.; TOR=20 u.t. y TAND=20 u.t.; completad el siguiente cronograma (cada división vertical corresponde a 10 u.t.). 1 1 1 0 1/7 Ejercicio 3 (Objetivos 3.1, 4.5, 3.4.2, 4.8.1, 4.10 y 4.7) (0,5 punto) Escribid el valor lógico de los bits de salida del siguiente circuito (con buses y bloques de 8 bits) para los siguientes valores de las entradas: X = 00110111, Y = 11000001 y Cin=0. a 0 b 0 W7 0 W6 0 W5 0 W4 0 W3 1 W2 0 W1 0 W0 0 Ejercicio 4 (Objetivo 5.15) (1 punto) Indicad cuál es el camino crítico (o uno de ellos si hay varios) y el tiempo de ciclo mínimo del circuito secuencial formado por la unidad de control y la unidad de proceso que se muestran a continuación. Considerad que: • • • • El tiempo de propagación de cada uno de los dispositivos es: TNot = 10, TAnd = 20, TOr = 20, TF1 =30, TF2 = 30, TF3 = 40, TMUX =50, TBiestable = 100, TREG1 = 110 y TREG2 = 120 u.t. La señal de entrada X está estable pasadas 130 u.t. desde que se produce el flanco ascendente de cada ciclo de reloj. La señal de entrada In está estable pasadas 120 u.t. desde que se produce el flanco ascendente de cada ciclo de reloj. La salida W debe estar estable 20 u.t. antes del flanco ascendente de cada ciclo de reloj. 2/7 Examen final B IC-09-10-Q2 Apellidos: ……………….………………………………………… Nombre:………………………………………… DNI:………………………… Ejercicio 5 (Objetivo 5.13) (1,5 puntos) Dado el grafo de estados de un circuito secuencial de Moore, se pide lo siguiente. a) Completad el cronograma simplificado que muestra el comportamiento del circuito (valor lógico del estado y de las salidas) para la secuencia de valores indicada. (0,5 Puntos). Num. Ciclo 0 1 2 3 4 5 6 7 8 9 Estado: q1q0 00 00 00 01 01 10 11 01 10 11 0 1 1 0 0 1 0 1 0 1 010 010 011 011 100 101 011 100 101 010 Entrada: y Salida z2z1z0 b) Escribid la tabla del estado siguiente (tabla de transiciones) y la tabla de salidas del circuito. (0,5 puntos) Tabla de salidas: Tabla de transiciones: y 0 0 0 0 1 1 1 1 q1 0 0 1 1 0 0 1 1 q0 0 1 0 1 0 1 0 1 q 1+ 0 1 1 0 0 0 1 0 q 0+ 0 0 1 0 1 1 1 1 q1 q0 z2 0 0 1 1 z1 1 1 0 0 z0 0 1 0 1 c) Dibujad el esquema lógico que implementa el circuito con el mínimo número de biestables D y dos memorias ROM. Indicad claramente: (0,5 puntos) • • • El nombre de todas las señales de entrada y salida del circuito. Los bits de dirección de las dos ROMs, para saber el peso de los mismos, la dirección (en decimal) de la primera y última palabra de la ROM y el contenido de cada palabra dentro del símbolo de cada ROM (codificad las X de las tablas como 0 en las ROMs). La entrada D y la salida Q de cada biestable. 3/7 *)).$ • ! • %#$ o o % o o -).'( • '# )( • • *#+, • & Ejercicio 6 (Objetivos 7.8 y 7.10) (1.5 puntos) Completad el fragmento del grafo de estados de Moore correspondiente a la unidad de control para que junto la UPG realice la funcionalidad descrita mediante un fragmento de código en C. Considerad que los datos son enteros en complemento a dos. Indicad las etiquetas de los arcos y los mnemotécnicos de las palabras de control asociados a cada estado que faltan. 4/7 Examen final B IC-09-10-Q2 Apellidos: ……………….………………………………………… Nombre:………………………………………… DNI:………………………… Ejercicio 7 (Objetivos 10.1) (1 punto) Rellenad la siguiente tabla indicando los mnemotécnicos o las instrucciones del lenguaje máquina SISA-I que faltan. Indicad el resultado ensamblado en hexadecimal. Indicad si hay alguna instrucción incorrecta (por algún motivo no se puede ensamblar). Mnemotécnico SISA-I LD R7,18(R7) MOVHI R4,lo(0xF36A) BZ R4, -2 OUT 0x43, R7 Lenguaje Maquina SISA-I 0x3FD2 0x596A 0x68FE 0x7F43 5/7 Ejercicio 8 (Objetivos 11.5) (1 punto) Escribid sobre la siguiente tabla el valor de los bits que tiene la palabra de control del SISP-I-1 durante el ciclo en que se ejecuta cada una de las instrucciones SISA-I que se indican. Poned x siempre que no se pueda saber el valor de un bit (al no saber cómo se han implementado las x en la ROM de la lógica de control) o cuando no importe el valor de ese bit para la ejecución correcta de la instrucción (aunque se pueda saber el valor codificando la instrucción). Suponed que antes de ejecutar cada instrucción el contenido de los registros, de los puertos de entrada y salida y de la memoria de datos es cero. Palabra de Control del SISP-I-1 @D b2 @A b1 b0 b2 b1 OP b0 F b1 b0 b2 b1 b0 Rb/N WrD InLd/Alu In/Ld Wr-Out Rd-In TknBr Instrucción SISA-I Wr-Mem ADDRIO N (hexa) @B b2 b1 b0 D3 D2 D1 (hexa) D0 D1 D0 ST 9(R5), R0 0 1 0 0 x x 0 x x x 1 0 1 0 0 1 0 0 0 0 0 0 0 0 0 9 X X BZ R4, -2 1 0 0 0 x x 0 x x x x x x 1 0 x x x 1 1 0 0 F F F E X X AND R3,R3,R1 0 0 0 0 x 0 1 0 1 1 0 1 1 0 0 0 0 0 1 0 0 1 X X X X X X IN R5, 18 0 0 1 0 1 1 1 1 0 1 x x x x x x x x x x x X X X X 1 2 x Ejercicio 9 (Objetivos 11.4) (1,5 puntos) Completad las filas y columnas sombreadas en la siguiente tabla que representa en forma compacta el contenido de la ROM de la lógica de control del SISP-I-1 (ROM-SISP-I-1-CTRL). Poned x siempre que un bit pueda valer tanto 0 como 1. Tened en cuenta que cuando se ejecuta una instrucción con un código de operación que no coincide con ninguno del SISA-I no se debe modificar el estado del computador, excepto el PC que se debe incrementar para pasar a ejecutar la siguiente instrucción (podemos decir que estos códigos de operación no usados hacen referencia a instrucciones NOP). MxN Mx@B MxF Mx@A OP0 OP1 Rb/N In/Ld InLD/Alu WrD Wr-Out Rd-In Wr-Mem Bz Bnz Not Used I15 I14 I13 I12 I8 0 0 0 0 X 0 1 0 A/L 0 0 0 1 X 0 1 0 CMP 0 0 1 0 X 0 0 0 ADDI 0 0 1 1 X 0 0 0 0 0 1 1 0 0 0 0 0 1 x 0 LD 0 1 0 0 X 0 0 1 0 0 0 x x 0 0 0 0 1 1 0 ST 0 1 0 1 0 0 0 x MOVI 0 1 0 1 1 0 0 1 MOVHI 0 1 1 0 0 0 1 0 0 0 0 x x 1 1 0 x x 1 1 BZ 0 1 1 0 1 1 0 0 0 0 0 x x 1 1 0 x x 1 1 BNZ 0 1 1 1 0 1 x x IN 0 1 1 1 1 0 x x OUT 1 X X X X Not Used 6/7 Examen final B IC-09-10-Q2 Apellidos: ……………….………………………………………… Nombre:………………………………………… DNI:………………………… Ejercicio 10 (Objetivos 10.2) (0.5 puntos) Indicad cuál es el estado del computador (el contenido de los registros del banco de registros y de las posiciones de memoria modificadas, de los puertos de salida modificados, el registro PC, etc) después de la ejecución de cada una de las siguientes instrucciones. Suponed que el contenido inicial de los registros y de las posiciones de memoria es igual para todas las instrucciones y es el siguiente: BANCO DE REGISTROS Registro Contenido 0x0000 R0 0x2454 R1 0x5656 R2 0xFFFF R3 0x0000 R4 0x0001 R5 0x0006 R6 MEMORIA Direccion Contenido 0x03AF 0x0000 0x63F7 0x0001 0xEB20 0x0002 0x3804 0x0003 0x7534 0x0004 0xA46A 0x0005 PC 0x0FA7 0x0003 R7 Instrucción MOVI R4, 0x75 ST 3(R5), R5 CMPLT R1, R3, R7 LD R6, 1(R4) Cambios en el estado del computador R4=0x0075, PC=0x0FA8 M[0x0004]=0x0001, PC=0x0FA8 R4=0x0000, PC=0x0FA8 R6=0x63F7, PC=0x0FA8 7/7