Sistemas Digitales. Tema 4. Circuitos Lógicos Secuenciales

Anuncio

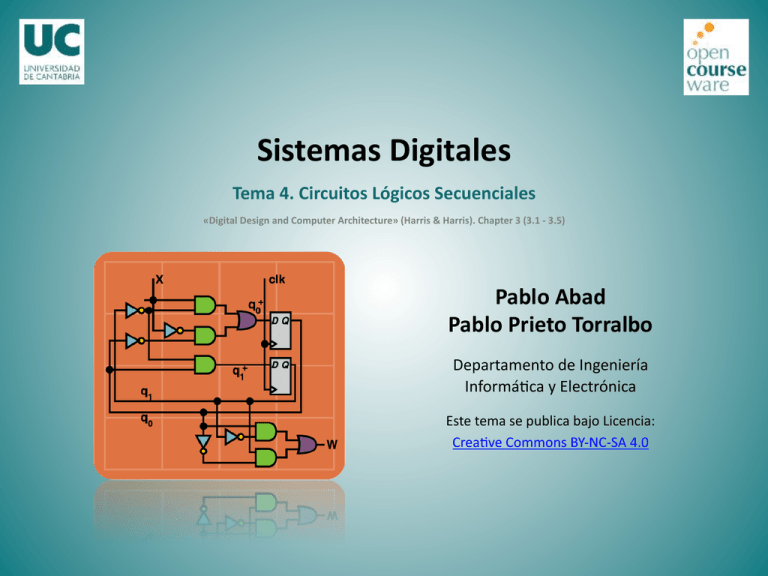

Sistemas Digitales Tema 4. Circuitos Lógicos Secuenciales «Digital Design and Computer Architecture» (Harris & Harris). Chapter 3 (3.1 -­‐ 3.5) Pablo Abad Pablo Prieto Torralbo Departamento de Ingeniería Informá2ca y Electrónica Este tema se publica bajo Licencia: Crea2ve Commons BY-­‐NC-­‐SA 4.0 Índice • Introducción: – Definición de CLS. – Necesidad de Memoria y Sincronización. • Latches y Flip Flops. • Máquinas de Estados: – Mealy. – Moore. • Análisis. • Síntesis: – Mínimo número de biestables. – 1 biestable por estado. • Timing. Tema 4 : Circuitos Lógicos Secuenciales 2 Introducción • Circuito Lógico Secuencial (CLS): – Definición: circuito combinacional cuya salida depende de los valores actuales y pasados de las señales de entrada. – Se trata de circuitos en los que aparecen lazos de «feedback» (salidas del circuito pueden actuar como valores de entrada). – Los Componentes de un CLS son: • Señales de entrada y Salida (señales binarias). • Señal de Reloj (señal binaria con forma periódica). • Lógica Combinacional (determina la salida y el próximo estado). inputs • Almacenamiento (man2ene información sobre el estado actual). clock Tema 4 : Circuitos Lógicos Secuenciales outputs n Lógica Combinacional n m m Storage 3 Introducción • Ejemplo: Circuito contador de «unos»: – La salida depende del valor que tengo en input (valor actual) y de los «unos» que llevo contados hasta el momento (valor pasado). A cargo de calcular el número de unos en función de la señal de entrada y de los que hemos contado hasta el momento. Input: señal binaria con valor «1» ó «0». Lógica Combinacional Storage Tema 4 : Circuitos Lógicos Secuenciales Output: número de «unos» en la entrada (satura en 7). Necesitamos almacenar el número de «unos» contados hasta el momento (Estado).(Necesidad de Memoria). 4 Introducción • Necesidad de Sincronización (Reloj): input(t) – Pregunta: Con la siguiente señal de entrada, ¿Cuántos unos contaría mi CLS? 0 0 0 1 0 1 1 0 1 0 1 0 1 0 0 0 – Respuesta: Nos falta información para poder considerar una respuesta como válida (3?, 6?…). 0 0 0 0 0 0 1 0 1 0 1 0 Wme 0 outputs input 3 CLC 3 3 clock Tema 4 : Circuitos Lógicos Secuenciales 0 Storage 5 Introducción input 3 CLC 3 3 clock Storage • Necesidad de Sincronización (Reloj): input(t) – La información adicional la proporciona la señal de reloj, que marca en qué precisos instantes se lee la señal de entrada. – El reloj convierte la señal de entrada en una señal síncrona. clock Wme 1 1 0 1 Señal Síncrona (Dato + Clk) = secuencia de bits. Tema 4 : Circuitos Lógicos Secuenciales 6 Índice • Introducción: – Definición de CLS. – Necesidad de Memoria y Sincronización. • Latches y Flip Flops. • Máquinas de Estados: – Mealy. – Moore. • Análisis. • Síntesis: – Mínimo número de biestables. – 1 biestable por estado. • Timing. Tema 4 : Circuitos Lógicos Secuenciales 7 Latches y Flip Flops • Un CLS debe almacenar información que se uWlizará en el futuro (estado), nuevo elemento: Memoria. • ¿Cómo almacenamos un valor con lógica combinacional?: – Feedback (realimentación): la salida se conecta a la entrada y conseguimos que la señal se mantenga en el 2empo. ¿Con un inversor? out NO, la señal de salida no Wene un valor estable. Tema 4 : Circuitos Lógicos Secuenciales ¿Y si uWlizo dos? (BIESTABLE) 0 1 1 0 Almaceno un 1 out Almaceno un 0 Pero… ¿cómo cambio el valor almacenado? 8 Latches y Flip Flops • Cambio del valor almacenado. RESET Q 0 ATENCIÓN RESET 1 Q SET 1 Q 0 RESET Q Q Q Tema 4 : Circuitos Lógicos Secuenciales 1 ¿Q = Q ? No es un biestable. El valor final no es predecible. R = S = 1: prohibido. Q ¿Cómo consigo volver de 0 a 1? 0 Q Q RESET Q SET 9 Latches y Flip Flops • Latch SR: – Elemento de memoria más simple en el diseño de sistemas digitales. R S S 0 0 0 1 1 R 0 0 1 0 1 Q Q Q Q(next) Q(next) 0 0 1 1 1 0 X 0 1 X 1 0 X 0 0 Tema 4 : Circuitos Lógicos Secuenciales Biestable: el circuito almacena el valor previa-­‐ mente introducido (memoria). Q(next) = Q. Set/Reset: se graba un nuevo valor de Q. Q(next) puede ser dis2nto a Q. Don´t Care: el valor de entrada no influye en la salida (me da igual que sea un 1 o un 0. Prohibido: valor final no biestable. 10 Latches y Flip Flops • Gated D-­‐Latch: – Eliminamos la posibilidad de alcanzar el estado prohibido. – Sigue funcionando como elemento de memoria. D R Q C S C 0 0 1 D 0 1 0 R 0 0 1 S 0 0 0 1 1 0 1 nunca 1,1 Tema 4 : Circuitos Lógicos Secuenciales Q C 0 0 1 1 D X X 0 1 Q Q(next) Q(next) 0 0 1 1 1 0 X 0 1 X 1 0 Hold Set/Reset Funcionamiento: C = 0: mantengo el valor previamente almacenado. C = 1: Copio el valor de D al interior del lazo. 11 Latches y Flip Flops • Ejemplo de Funcionamiento: D Q S Q C D (data) C (clock) 1 ciclo R Q Hold S/R Ciclo Bits (D) Bits (Q) n n+1 n+2 n+3 n+4 n+5 1 0 0 1 0 0 0 1 0 0 1 0 Tema 4 : Circuitos Lógicos Secuenciales El valor a la entrada en el ciclo n (presente) aparece en la salida en el ciclo n+1 (futuro). 12 Latches y Flip Flops • Problema: – El comportamiento deseado (Diaposi2va anterior) solamente se cumple si la señal de entrada no cambia durante la fase de Set/Reset (clk = 1). ciclo n+1 C (clock) ciclo n ciclo n+2 D R Q S Q D (data) C Ciclo Bits (D) Bits (Q) Hold S/R Tema 4 : Circuitos Lógicos Secuenciales n n+1 n+2 1 0 0 0 0 1 ¿SOLUCIÓN? 13 Latches y Flip Flops • Biestable D acWvado por flanco (Flip Flop): Master Latch R Q R Q S Q S Q Segunda fase del ciclo (clk = 0): el siguiente estado, en la entrada del circuito, es almacenado en el Master Latch. Tema 4 : Circuitos Lógicos Secuenciales Slave Latch Primera Fase del ciclo (clk = 1): el estado previamente calculado se convierte en el estado actual, y es enviado a la salida. 14 Latches y Flip Flops • Biestable D acWvado por flanco (Flip Flop): ciclo n ciclo n+1 ciclo n+2 D (data) C (clock) D D Qm D Qs C C Q Clk Hold Q Qm Hold Tema 4 : Circuitos Lógicos Secuenciales Hold Ciclo Bits (D) Bits (Q) n n+1 n+2 1 0 0 0 1 0 ¡¡CORRECTO!! 15 Latches y Flip Flops • Biestable D acWvado por flanco (Flip Flop): – Elemento básico de memorización (1 bit). – Ecuación caracterís2ca: q+ = d • q+: estado siguiente (ciclo actual+1). • d: valor de entrada actual. d D q Q Tema 4 : Circuitos Lógicos Secuenciales q(salida) El valor presente en d cuando el reloj hace un flanco ascendente se copia en el Flip Flop, y se manWene hasta el si-­‐ guiente flanco ascendente (indepen-­‐ dientemente de lo que haga la señal de entrada). d(data) C (clock) Clk 16 Latches y Flip Flops • Registro: D n REG – Elemento de memorización de n bits. – Formado por n Flip Flops conectados en paralelo. n Clk D = dn-1, dn-2, … d1, d0 Q = qn-1, qn-2, … q1, q0 Tema 4 : Circuitos Lógicos Secuenciales d0 D Q q0 d1 D Q q1 Q dn-­‐2 Q+ = D dn-­‐1 D Q qn-­‐2 qn-­‐1 D Q 17 Latches y Flip Flops • Ejercicio 1: D (data) C (clock) – Dadas las señales de reloj y de entrada del cronograma inferior, completa la forma de la señal de salida si el elemento de memoria u2lizado es un latch-­‐D. El 2empo de propagación de dicho elemento es 10 u.t. – Repite el proceso anterior para un Flip Flop con el mismo 2empo de propagación. – ¿Cómo cambia la señal de salida si tp = 0? 50 Tema 4 : Circuitos Lógicos Secuenciales 100 150 200 18 Latches y Flip Flops • Ejercicio 2: – Dadas los CLS de las figuras inferiores y el cronograma de la señal de entrada, completa la forma de la señal de salida en ambos casos (delay NOT: 10 u.t., delay Flip Flop: 20 u.t.). input d D input Q input Clk 50 Tema 4 : Circuitos Lógicos Secuenciales d D Q Clk 100 150 200 19 Índice • Introducción: – Definición de CLS. – Necesidad de Memoria y Sincronización. • Latches y Flip Flops. • Máquinas de Estados: – Mealy. – Moore. • Análisis. • Síntesis: – Mínimo número de biestables. – 1 biestable por estado. • Timing. Tema 4 : Circuitos Lógicos Secuenciales 20 Máquinas de Estados • Circuito Secuencial Síncrono: – Red de combinacionales y biestables conectados entre sí. – Puede haber caminos cíclicos, pero 2enen que atravesar al menos un biestable. – Todos los biestables u2lizan la misma señal de reloj. – Las señales de entrada se sincronizan con el mismo reloj. D Q CLC2 x CLC1 D Q CLC3 w0 D Q w1 Clk Tema 4 : Circuitos Lógicos Secuenciales 21 Máquinas de Estados • Circuito Secuencial Síncrono: Tiempo de ciclo. X clk D Q Tc > 140 Clk x t y 40 CLC z D Q y W 100 z 40 Tp(FF) = 40 u.t. w Tp(CLC) = 100 u.t. Tc ≥ Tp(FF) + Tp(CLC) Tema 4 : Circuitos Lógicos Secuenciales 22 Máquinas de Estados • Máquinas de Estados (FSM): – Cualquier CLS se puede representar con un esquema como el de la figura inferior (Modelo de Mealy): • Agrupando todos los circuitos combinacionales en un único CLC y todos los biestables (Flip Flops) en un único REG. – Se denomina FSM porque un circuito con K registros solo puede estar en un número finito (2K) de estados. H k Q+ REG Entrada X k Q Clk Tema 4 : Circuitos Lógicos Secuenciales CLC G Modelo de Mealy: m W Salida n W = H(X,Q) Ec. de salida Q+= G(X,Q) Ec. estado siguiente 23 Máquinas de Estados • Representación alternaWva del CLS de Mealy: – Separando las funciones H y G. Modelo de Mealy: n Q m CLC k G Q W = H(X,Q) Ec. de salida W Q+= G(X,Q) Ec. estado siguiente Clk n X CLC G k Q+ REG Entrada W CLC n k m k Q H Salida + H Salida k REG Entrada X Clk Tema 4 : Circuitos Lógicos Secuenciales 24 Máquinas de Estados • Especificación de un CLS: – Qué datos necesitamos para caracterizar el circuito: número de entradas: X=(xn-­‐1, xn-­‐2,…,x1,x0). número de salidas: W=(wm-­‐1, wm-­‐2,…,w1,w0). número de estados: Q=(qk-­‐1, qk-­‐2,…,q1,q0). Tabla de verdad de W: CLC H. Tabla de verdad de Q+: CLC G. Estado inicial: Valor inicial de Q. m n X W CLC CLC k G k Q+ REG Entrada n k Q H Salida • • • • • • Clk Tema 4 : Circuitos Lógicos Secuenciales 25 Máquinas de Estados • Ejemplo de Especificación de un CLS: – X=(x0), W=(w1,w0), Q=(q1,q0), Estado inicial (0,0). -­‐ Tabla de verdad de W q1 0 0 0 0 1 1 1 1 q0 0 0 1 1 0 0 1 1 x0 0 1 0 1 0 1 0 1 w1 0 0 1 1 0 0 0 1 w0 0 1 0 1 1 0 0 0 Tabla de Salida Tema 4 : Circuitos Lógicos Secuenciales Clk q0 0 0 1 1 0 0 1 1 x0 0 1 0 1 0 1 0 1 q1+ q0+ 0 0 0 1 1 0 0 1 0 1 0 0 x x x x Tabla de Transición (estado siguiente) n k -­‐ Tabla de verdad de Q+ q1 0 0 0 0 1 1 1 1 X Entrada CLC G Q+ k REG Q n k CLC H m Salida W 26 Máquinas de Estados • Ejercicio 1: – Dada la especificación de un CLC de la diaposi2va anterior, implementar el circuito con los siguientes componentes: puertas NOT, AND y OR de 3 entradas y Biestables D ac2vados por flanco. Tema 4 : Circuitos Lógicos Secuenciales 27 Máquinas de Estados • Ejercicio 1: – Dada la especificación de un CLC de la diaposi2va anterior, implementar el circuito con los siguientes componentes: puertas NOT, AND y OR de 3 entradas y Biestables D ac2vados por flanco. x0 q0 q0+ q1+ w0 D Q D Q q1 q1 w1 Tema 4 : Circuitos Lógicos Secuenciales 28 q0 clk Máquinas de Estados • Ejercicio 2: – Dada la especificación de un CLC de la diaposi2va anterior, rellena la siguiente tabla con los valores de las señales de salida en cada ciclo de reloj. Ciclo n n+1 n+2 n+3 n+4 n+5 x0 0 1 1 0 1 1 w0 w1 Tema 4 : Circuitos Lógicos Secuenciales 29 Máquinas de Estados • El Grafo de Estados: – Representación alterna2va de la Tabla de Transición. – q1+(ciclo n)= q1(ciclo n+1). – Facilita el proceso de síntesis: a par2r de una descripción textual es más fácil inferir el grafo que la T.V. Formato: Entradas (x1,x0) Estado ciclo n (q1,q0) Tema 4 : Circuitos Lógicos Secuenciales Estado ciclo n+1 (q1+,q0+) 30 Máquinas de Estados • De la T.V. al Grafo de Estados: Clk 0 q1 0 0 0 0 1 1 1 1 q0 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 1 0 0 1 0 0 CLC 00 q0+ 0 1 0 1 1 1 0 1 n k Tabla de Transición x0 q1+ X Entrada G 1 0 Q+ k REG 1 1 Q 01 11 n k CLC H 0 1 m 0 Salida W 10 Tema 4 : Circuitos Lógicos Secuenciales 31 Máquinas de Estados • Ejemplo de Especificación de un CLS: – X = (x0), W = (w1,w0), Q = (q1,q0), Estado inicial (0,0). Clk X Entrada n k -­‐ Tabla de verdad de W q1 0 0 0 0 1 1 1 1 q0 0 0 1 1 0 0 1 1 x0 0 1 0 1 0 1 0 1 w1 0 0 1 1 0 0 0 1 w0 0 1 0 1 1 0 0 0 Tabla de Salida Tema 4 : Circuitos Lógicos Secuenciales -­‐ Tabla de verdad de Q+ q1 0 0 0 0 1 1 1 1 q0 0 0 1 1 0 0 1 1 x0 0 1 0 1 0 1 0 1 q1+ q0+ 0 0 0 0 1 0 0 1 1 0 1 0 x x x x Tabla de Transición (estado siguiente) CLC G Q+ k REG Q n k CLC H m Salida W 32 Máquinas de Estados • Ejemplo de Especificación de un CLS: – X = (x0), W = (w1,w0), Q = (q1,q0), Estado inicial (0,0). Clk X Entrada n k -­‐ Tabla de verdad de W -­‐ Tabla de verdad de Q+ CLC 0 q1 0 0 0 0 1 1 1 1 q0 0 0 1 1 0 0 1 1 x0 0 1 0 1 0 1 0 1 w1 0 0 1 1 0 0 0 1 w0 0 1 0 1 1 0 0 0 Tabla de Salida Tema 4 : Circuitos Lógicos Secuenciales G 00 Q+ k 1 0 REG 1 1 Q n k 01 11 CLC 0 1 H 0 m 10 Grafo de Estados Salida W 33 Máquinas de Estados • Ejercicio: – Dada la siguiente Tabla de Transición de un CLS, dibuja su grafo de estados. q1 q0 x1 x0 q 1+ q 0+ 0 0 0 0 0 0 0 0 0 1 0 1 0 0 1 0 1 0 0 0 1 1 0 1 0 1 0 0 0 0 0 1 0 1 0 1 0 1 1 0 1 0 0 1 1 1 0 1 1 0 0 0 0 0 1 0 0 1 0 1 1 0 1 0 1 0 1 0 1 1 1 0 1 1 0 0 0 0 1 1 0 1 0 0 1 1 1 0 0 0 1 1 1 1 0 0 Tema 4 : Circuitos Lógicos Secuenciales 34 Máquinas de Estados • Ejercicio: – Dada la siguiente Tabla de Transición de un CLS, dibuja su grafo de estados. q1 q0 x1 x0 q 1+ q 0+ 00 0 0 0 0 0 0 0 0 0 1 0 1 0 0 1 0 1 0 0 0 1 1 0 1 0 1 0 0 0 0 0 1 0 1 0 1 0 1 1 0 1 0 0 1 1 1 0 1 1 0 0 0 0 0 1 0 0 1 0 1 1 0 1 0 1 0 1 0 1 1 1 0 1 1 0 0 0 0 01 1 1 0 1 0 0 11 1 1 1 0 0 0 1 1 1 1 0 0 Tema 4 : Circuitos Lógicos Secuenciales 00 10 01 11 10 00 01 00 11 10 10 01 35 Máquinas de Estados • Máquinas de Estados, Modelo de Moore: – CLS en el que los valores de salida únicamente dependen del estado, no de la señal de entrada. CLC n CLC k G k Q+ REG Entrada X n k Modelo de Mealy: m H W W = H(X,Q) Ec. de salida Salida MEALEY Q Q+= G(X,Q) Ec. estado siguiente Clk Modelo de Moore: MOORE k G k + Q Clk Tema 4 : Circuitos Lógicos Secuenciales k Q CLC H m W Salida CLC REG n X W = H(Q) Ec. de salida Q+= G(X,Q) Ec. estado siguiente 36 Máquinas de Estados • Especificación de un CLS Wpo MOORE: Clk X – X = (x0), W = (w1,w0), Q = (q1,q0), Estado inicial (0,0). -­‐ Tabla de verdad de Q+ q1 0 0 0 0 1 1 1 1 q0 0 0 1 1 0 0 1 1 x0 q1+ 0 1 0 1 0 1 0 1 0 0 1 0 0 1 0 0 q0+ 0 1 0 1 1 1 0 1 k -­‐ Tabla de verdad de W q1 0 0 1 1 q0 0 1 0 1 w1 0 0 0 1 w0 0 1 0 0 n CLC G Q+ k REG Q k CLC H m Tabla de Transición (estado siguiente) Tabla de Salida Salida W Tema 4 : Circuitos Lógicos Secuenciales 37 Máquinas de Estados • Especificación de un CLS Wpo MOORE: Clk X – X = (x0), W = (w1,w0), Q = (q1,q0), Estado inicial (0,0). -­‐ Tabla de verdad de W -­‐ Tabla de verdad de Q+ 0 00 1 0 k 1 q1 0 0 1 1 q0 0 1 0 1 w1 0 0 0 1 w0 0 1 0 0 n CLC G Q+ k REG Q k 1 01 11 0 1 0 10 Grafo de Estados Igual que en Mealy, la Tabla de Transiciones se puede susWtuir por el Grafo de Estados. Tabla de Salida CLC H m Salida W Tema 4 : Circuitos Lógicos Secuenciales 38 Máquinas de Estados • Especificación de un CLS Wpo MOORE: Clk X – X = (x0), W = (w1,w0), Q = (q1,q0), Estado inicial (0,0). 0 q1 q0 w1 w0 0 0 0 0 0 1 0 1 1 0 0 0 1 1 1 0 k CLC Grafo de Estados 00 00 n G Q+ 0 1 k REG Q Como los valores de salida solo dependen del estado, se pueden incluir en el Grafo de Estados, que susWtuye ambas T.V. en la espe-­‐ cificación. Tema 4 : Circuitos Lógicos Secuenciales 1 11 k 01 01 10 1 CLC 1 0 H m 0 10 00 Salida W 39 Índice • Introducción: – Definición de CLS. – Necesidad de Memoria y Sincronización. • Latches y Flip Flops. • Máquinas de Estados: – Mealy. – Moore. • Análisis. • Síntesis: – Mínimo número de biestables. – 1 biestable por estado. • Timing. Tema 4 : Circuitos Lógicos Secuenciales 40 Análisis • Análisis Lógico: Dado el esquema lógico de un CLS obtener el grafo de estados: – PASO 1: obtener las Tablas de Verdad (transición y salida). – PASO 2: obtener el Grafo (a par2r de las tablas). clk x q1 0 0 0 0 1 1 1 1 q0 0 0 1 1 0 0 1 1 x0 0 1 0 1 0 1 0 1 q1+ q0+ 0 1 0 1 1 0 1 1 0 1 0 0 0 0 0 0 q0+ D Q q1+ D Q q1 q0 Tabla de Transición w Tema 4 : Circuitos Lógicos Secuenciales 41 Análisis • Análisis Lógico: Dado el esquema lógico de un CLS obtener el grafo de estados: – PASO 1: obtener las Tablas de Verdad (transición y salida). – PASO 2: obtener el Grafo (a par2r de las tablas). q1 0 0 0 0 1 1 1 1 q0 0 0 1 1 0 0 1 1 x0 0 1 0 1 0 1 0 1 q1+ q0+ 0 1 0 1 1 0 1 1 0 1 0 0 0 0 0 0 Tabla de Transición Tema 4 : Circuitos Lógicos Secuenciales 00 0 1 0 1 1 01 11 0 1 0 10 42 Análisis • Análisis Lógico: Dado el esquema lógico de un CLS obtener el grafo de estados: – PASO 1: obtener las Tablas de Verdad (transición y salida). – PASO 2: obtener el Grafo (a par2r de las tablas). clk x q1 q0 0 0 0 1 1 0 1 1 w 0 1 1 0 Tabla de Salida q0+ D Q q1+ D Q q1 q0 w Tema 4 : Circuitos Lógicos Secuenciales 43 Análisis • Análisis Lógico: Dado el esquema lógico de un CLS obtener el grafo de estados: – PASO 1: obtener las Tablas de Verdad (transición y salida). – PASO 2: obtener el Grafo (a par2r de las tablas). q1 q0 0 0 0 1 1 0 1 1 w 0 1 1 0 00 1 0 0 0 1 1 01 11 0 1 0 1 Tabla de Salida 0 10 1 Tema 4 : Circuitos Lógicos Secuenciales 44 Índice • Introducción: – Definición de CLS. – Necesidad de Memoria y Sincronización. • Latches y Flip Flops. • Máquinas de Estados: – Mealy. – Moore. • Análisis. • Síntesis: – Mínimo número de biestables. – 1 biestable por estado. • Timing. Tema 4 : Circuitos Lógicos Secuenciales 45 Timing • Análisis Temporal: Dado el esquema lógico de un CLS, los 2empos de propagación de los disposi2vos y los 2empos de estabilización de las entradas y las salidas, obtener el 2empo de ciclo mínimo. • Camino críWco: En un CLS Síncrono, los caminos a evaluar son diferen-­‐ tes, y corresponden a los siguientes 2pos: – Camino de Biestable a Biestable (B-­‐B). – Camino de Entrada a Biestable (E-­‐B). – Camino de Biestable a Salida (B-­‐S). n Q H X CLC k G Tiempo de estabilización de entrada k + Q k Q (B-­‐S) CLC H m W REG CLC REG REG Tiempo de estabilización de salida CLC G Q+ (B-­‐B) Tema 4 : Circuitos Lógicos Secuenciales 46 Timing • Ejemplo: Obtener el T.C. mínimo del circuito. Tiempos: – Puertas: OR: 30 u.t. AND: 30 u.t. NOT: 20 u.t. – Biestables: FF1: 100 u.t. FF2: 150 u.t. – Estabilización: Entrada: 110 u.t. Salida: 20 u.t. x clk N1 q0+ A1 O1 N2 N3 D Q FF1 A2 A3 D Q q1+ FF2 q1 q0 N5 Tema 4 : Circuitos Lógicos Secuenciales A4 N4 O2 w A5 47 Índice • Introducción: – Definición de CLS. – Necesidad de Memoria y Sincronización. • Latches y Flip Flops. • Máquinas de Estados: – Mealy. – Moore. • Análisis. • Síntesis: – Mínimo número de biestables. – 1 biestable por estado. • Timing. Tema 4 : Circuitos Lógicos Secuenciales 48 Síntesis • A parWr de una descripción textual, obtener el Circuito Secuencial: – El primer paso es obtener el Grafo de Estados. – Una vez completado el grafo, procedemos a la implementación rsica. • Ejemplo: Circuito reconocedor de secuencias: – Obtener la implementación de un circuito de una entrada y una salida que reconoce la secuencia 011 de valores en la señal de entrada. La se-­‐ ñal de salida toma valor 1 cada vez que la secuencia a detectar aparece. y 1 1 1 0 1 1 1 1 0 1 0 1 1 0 1 1 0 0 0 1 0 0 0 0 0 0 0 t y CLS w w 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 t Tema 4 : Circuitos Lógicos Secuenciales 49 Síntesis y w CLS • Grafo de Estados: Circuito reconocedor de secuencias (011). • Paso 1: obtener el estado inicial: • E0 (estado inicial): no ha llegado ningún bit de la secuencia a reconocer. • Salida (para este estado) w: 0. E0 0 Tema 4 : Circuitos Lógicos Secuenciales 50 Síntesis y w CLS • Grafo de Estados: Circuito reconocedor de secuencias (011). • Paso 1: obtener el estado inicial: • E0 (estado inicial): no ha llegado ningún bit de la secuencia a reconocer. • Salida (para este estado) w: 0. • Paso 2: comienzo a construir el grafo: • Si me encuentro en el estado inicial, ¿qué ocurre para cada posible valor de entrada del CLS?: • Llega un 1: sigue sin llegar un bit de la secuencia (me quedo en E0). • Llega un 0: llega el 1er bit de la secuencia (nuevo estado E1). 0 1 Tema 4 : Circuitos Lógicos Secuenciales E0 E1 0 0 51 Síntesis y w CLS • Grafo de Estados: Circuito reconocedor de secuencias (011). • Paso 3: repe2mos el procedimiento del paso anterior: – Lo hacemos así hasta tener completo el grafo. 0 1 0 E0 0 1 E1 0 1 E2 E3 0 0 1 0 1 E0: ningún bit de la secuencia. E1: ha llegado 1 bit de la secuencia (0). E2: han llegado 2 bits de la secuencia (01). E3: han llegado los 3 bits de la secuencia (011) -­‐> Salida = 1. Tema 4 : Circuitos Lógicos Secuenciales 52 Síntesis • Ejercicio 1: – Obtener el grafo de estados de un contador up/down módulo 7. El contador 2ene dos entradas: count Enable (E) y count Direc2on (D). Cuando E = 1 el contador cuenta en la dirección especificada por D, y termina cuando E = 0. El contador cuenta hacia arriba si D = 0 y hacia abajo si D = 1. El contador 2ene una salida Y que toma valor 1 cuando el contador alcanza el valor 7 o el valor 0. Tema 4 : Circuitos Lógicos Secuenciales 53 Síntesis • Ejercicio 2: – Obtener el grafo de estados de una puerta con cerradura de apertura por secuencia de dígitos. El display 2ene los botones mostrados en la fi-­‐ gura inferior. Cada vez que pulsamos una tecla la señal Push se ac2va, y las señales numi indican la tecla que se pulsó (valor en binario). La señal de Reset sirve para reiniciar la introducción del código de apertura. – El circuito 2ene dos señales de Salida: Open y Block. Para que la señal Open se ac2ve y la puerta se abra, debemos introducir: 0-­‐3-­‐2. Si intro-­‐ ducimos una secuencia de tres dígitos incorrecta, la puerta se bloquea (ac2vamos señal Block). num 0 1 2 3 Tema 4 : Circuitos Lógicos Secuenciales R 2 Push Reset Open CLS Block clk 54 Síntesis • Ejercicio 3: – Marge quiere instalar un sistema de alarma que la indique las per-­‐ sonas que se encuentran en la cocina en todo momento. Para ello, se instalan dos sensores en el marco de la puerta tal y como mues-­‐ tra la figura. Estos sensores toman valor 1 si su flujo es interrumpi-­‐ do, siendo 0 el resto del 2empo. Sabiendo que Bart y Homer no ca-­‐ ben por la puerta si intentan entrar a la vez, Determina el grafo de estados del circuito que avisará a Marge. S1 S0 Tema 4 : Circuitos Lógicos Secuenciales 55 Síntesis • Del Grafo de Estados a la Implementación del Circuito: – El Grafo de Estados nos proporciona las tablas de verdad. – Codificaremos los estados (binario) con el número mínimo de biestables: • Suponiendo n estados: número de biestables= int(log2n). – Conocidas las tablas, la síntesis u2liza las mismas técnicas vistas para CLCs. • Implementación de los CLCs de estado siguiente y salida: – Con Not, And y Or en suma de minterms. – Con decodificadores y puertas Or. – Con ROMs: • Dos ROMs. • Una ROM. • Una ROM y un Mul2plexor de buses. Tema 4 : Circuitos Lógicos Secuenciales 56 Síntesis • Determinación de las Tablas de Verdad: – Grafo de Estados: Circuito reconocedor de secuencias (011). 0 1 0 E0 0 1 E1 0 1 E2 0 0 0 1 Codif. de Estado Estado E0 Codif. 00 E1 01 E2 10 E3 11 Tema 4 : Circuitos Lógicos Secuenciales Tabla de Salida q1 q0 w1 0 0 0 0 1 0 1 0 0 1 1 1 E3 1 Tabla de Transición q1 0 0 0 0 1 1 1 1 q0 0 0 1 1 0 0 1 1 x0 q1+ q0+ 0 0 1 1 0 0 0 0 1 1 1 0 0 0 1 1 1 1 0 0 1 1 0 0 57 Síntesis • Implementación con Dos ROMs: x 0 1 0 1 0 1 0 1 q1+ 0 0 0 1 0 1 0 0 Tema 4 : Circuitos Lógicos Secuenciales 0 0 0 1 0 1 0 0 1 1 1 q0+ 1 0 1 0 1 1 1 0 X CLC 2 G 2 Q+ 2 CLC W H Q Salida 0 REG q1 q0 w Clk Dec q1 q0 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 Tabla de Salida Est. Cod. E0 00 E1 01 E2 10 E3 11 Tabla de Transición Codif. Estado – Grafo de Estados: Circuito reconocedor de secuencias (011). 0 1 2 x 0 q0 1 4 2 5 q1 3 q0 0 q1 1 0 1 2 3 6 7 ROM ROM w q1+ q0+ 58 Síntesis • Implementación con Una ROM (Mealy): H X + Q CLC 2 REG 2 G Q W Salida Est. Cod. E0 00 E1 01 E2 10 E3 11 Entrada Codif. Estado – Grafo de Estados: Circuito reconocedor de secuencias (011). q1 0 0 0 0 1 1 1 1 q0 0 0 1 1 0 0 1 1 x 0 1 0 1 0 1 0 1 q1+ 0 0 0 1 0 1 0 0 q0+ 1 0 1 0 1 1 1 0 w 0 0 0 0 0 0 1 1 Tema 4 : Circuitos Lógicos Secuenciales Dec Tabla de Transición/Salida Clk 0 1 x 0 q0 2 3 1 4 q1 2 5 6 7 ROM q1+ q0+ w 59 Síntesis q1 0 0 0 0 1 1 1 1 q0 0 0 1 1 0 0 1 1 x 0 1 0 1 0 1 0 1 q1+ 0 0 0 1 0 1 0 0 q0+ 1 0 1 0 1 1 1 0 w 0 0 0 0 0 0 1 1 Tabla de Transición/ Salida Tabla de Transición/Salida • Implementación con Una ROM y MulWplexor. q1 q0 0 0 0 1 1 0 1 1 X=1 q1+ q0+ 0 0 1 0 1 1 0 0 X=0 q1+ q0+ 0 1 0 1 0 1 0 1 w 0 0 0 1 X 2 + Q REG Entrada H 2 CLC Q Clk Tema 4 : Circuitos Lógicos Secuenciales G W Clk X H CLC q0 Gx=0 Gx=1 Q+ q1+ W Salida REG q1 q0+ 60 Síntesis • Ejercicio: – Dado el grafo de estados inferior, implementar su circuito correspondien-­‐ te u2lizando el número mínimo de biestables y: • Dos ROM del tamaño que consideres necesario. • Una SoIa ROM. • Una Sola ROM y un Mul2plexor. 00 Grafo de Estados 00 00 10 01 11 00 00 10 11 10 01 01 01 11 01 11 10 Tema 4 : Circuitos Lógicos Secuenciales 61 Síntesis • Implementación con un Biestable por estado, DemulWplexores y puertas OR: – A par2r del Grafo de Estados del circuito. PASO 1: asignamos un biestable a cada estado. 1 E0 01 1 0 E0 E1 D Q D Q E1 10 0 Tema 4 : Circuitos Lógicos Secuenciales 62 Síntesis • Implementación con un Biestable por estado, DemulWplexores y puertas OR: – A par2r del Grafo de Estados del circuito. PASO 2: se conecta la salida de una puerta OR a la entrada D de cada biestable. El número de entradas de la OR será igual al número de arcos que llegan al Nodo (biestable). 1 E0 01 1 0 E0 E1 D Q D Q E1 2 arcos -­‐> 2 entradas 10 2 arcos -­‐> 2 entradas 0 Tema 4 : Circuitos Lógicos Secuenciales 63 Síntesis • Implementación con un Biestable por estado, DemulWplexores y puertas OR: – A par2r del Grafo de Estados del circuito. PASO 3: en la salida de cada Biestable se conecta un demul2plexor. Tendrá tantas señales de selección como señales de entrada 2ene el circuito. Se conectan las entradas del circuito a las señales de selec-­‐ ción de cada mul2plexor. 1 E0 01 E0 1 0 D Q 0 1 x E1 E1 D Q 0 1 x 10 0 Tema 4 : Circuitos Lógicos Secuenciales 64 Síntesis • Implementación con un Biestable por estado, DemulWplexores y puertas OR: – A par2r del Grafo de Estados del circuito. PASO 4: se conectan las salidas de los demul2plexores con las entradas de las OR, de acuerdo con el grafo. 1 E0 01 E0 1 0 D Q 0 1 x E1 E1 D Q 0 1 x 10 0 Tema 4 : Circuitos Lógicos Secuenciales 65 Síntesis • Implementación con un Biestable por estado, DemulWplexores y puertas OR: – A par2r del Grafo de Estados del circuito. PASO 5: cada señal de salida se forma con la OR de las salidas de los biestables de los estados en que vale 1 esa salida. 1 E0 01 E0 1 0 D Q E1 0 D Q 1 0 1 E1 10 0 Tema 4 : Circuitos Lógicos Secuenciales w0 w1 66 Síntesis • Ejercicio: – Dado el grafo de estados inferior, implementar su circuito correspondiente u2lizando un biestable por estado. 00 Grafo de Estados E0 01 00 11 00 00 01 11 E1 10 10 E2 11 01 10 11 01 Tema 4 : Circuitos Lógicos Secuenciales 67