1 TEMA 7 SECUENCIADOR DEL PROGRAMA

Anuncio

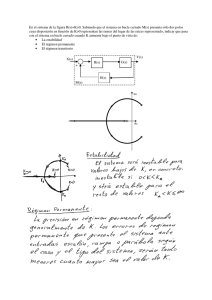

TEMA 7 SECUENCIADOR DEL PROGRAMA CURSO 2010/2011 SECUENCIADOR DEL PROGRAMA 1. 2. Introducción • Ciclo de Instrucción • Arquitectura del Secuenciador del Programa • Registros del Secuenciador y Registros del Sistema Operaciones del Secuenciador del Programa • Flujo Secuencial de Instrucciones • Acceso a datos en Memoria de Programa • Bifurcaciones • Bucles 3. Ejecución Condicional de Instrucciones 4. Bifurcaciones • Bifurcaciones Retrasadas y no Retrasadas • Pila del PC 1 SECUENCIADOR DEL PROGRAMA 5. 6. Bucles • Restricciones y Bucles Cortos • Pila de Direcciones de Bucles • Pila de Contadores de Bucles Timer • Habilitar/Inhabilitar el Timer • Interrupciones del Timer • Registros del Timer 7. Flags de las Pilas 8. Instrucciones IDLE e IDLE16 9. Caché de Instrucciones INTRODUCCION ¾ En los procesadores de la familia ADSP-2106x el flujo del programa es la mayor parte del tiempo lineal, el procesador ejecuta las instrucciones del programa de forma secuencial. ¾ Las alteraciones de este flujo secuencial vienen dadas por estructuras de programación tales como: 9 Bucles: una secuencia de instrucciones se ejecuta varias veces. 9 Saltos: el flujo del programa se transfiere de forma permanente a otra zona de la memoria de programa. 9 Subrutinas: el procesador interrumpe temporalmente el flujo secuencial para ejecutar instrucciones contenidas en otra zona de la memoria de programa. 9 Interrupciones: es un caso especial de las subrutinas en el cual la ejecución de la subrutina es desencadenada por un evento que ocurre en tiempo de ejecución, no por una instrucción del programa. 9 Instrucción Idle: es una instrucción especial cuya ejecución produce que el procesador cese sus operaciones manteniendo su estado actual. 2 INTRODUCCION INTRODUCCION ¾ Manejar estas estructuras de programación es la tarea del Secuenciador de Programa que poseen los procesadores ADSP-2106x. ¾ El Secuenciador de Programa selecciona la dirección de la siguiente instrucción y realiza también un amplio rango de funciones relacionadas como son: 9 Incrementar la dirección de búsqueda. 9 Mantenimiento de las Pilas. 9 Evaluar condiciones. 9 Decrementar el contador de bucles. 9 Calcular nuevas direcciones. 9 Mantenimiento de la caché de instrucciones. 9 Manejo de Interrupciones. 3 CICLO DE INSTRUCCION ¾ Los procesadores de la familia ADSP-2106x procesan las instrucciones en tres ciclos de reloj: 1. En el Ciclo de Búsqueda, el procesador lee la instrucción de la caché de instrucciones interna o de la memoria de programa. 2. Durante el Ciclo de Decodificación, la instrucción es decodificada generándose las condiciones que controlan la ejecución de la instrucción. 3. En el Ciclo de Ejecución, el procesador ejecuta la instrucción,se realizan todas las operaciones especificadas por la instrucción. ¾ Estos ciclos se solapan o segmentan “pipeline”. ¾ Cuando el flujo del programa es secuencial, mientras se busca una instrucción, la instrucción leída en el ciclo anterior está siendo decodificada y la instrucción buscada dos ciclos antes está siendo ejecutada. Por tanto la tasa de ejecución es de una instrucción por ciclo. CICLO DE INSTRUCCION 4 CICLO DE INSTRUCCION ¾ Cualquier alteración del flujo secuencial puede potencialmente disminuir esta tasa de ejecución de instrucciones. ¾ Operaciones del programa no secuenciales incluyen: 9 Acceso a datos en memoria de programa que entran en conflicto con búsquedas de instrucciones. 9 Saltos. 9 LLamadas y Retornos de subrutinas. 9 Interrupciones y Retornos. 9 Bucles. AQUITECTURA DEL SECUENCIADOR ¾ El Secuenciador selecciona el valor de la siguiente dirección de búsqueda de entre diversas posibles fuentes. ¾ El registro de dirección de búsqueda, registro de dirección de decodificación y el contador de programa (PC) contienen respectivamente las direcciones de las instrucciones que en el ciclo actual van a ser buscadas, decodificadas y ejecutadas. ¾ El PC está asociado con la Pila del PC, la cual es utilizada para almacenar direcciones de retorno y direcciones de comienzo de los bucles. ¾ El controlador de interrupciones realiza todas las funciones relacionadas con el procesamiento de las interrupciones, tales como determinar cuándo una interrupción está enmascarada y generar la dirección del vector de interrupción apropiada. ¾ La caché de instrucciones es la que posibilita que los procesadores de la familia ADSP-2106x puedan acceder a datos en memoria de programa y buscar una instrucción en la caché en el mismo ciclo. 5 AQUITECTURA DEL SECUENCIADOR ¾ El Generador de Direcciones DAG2 genera las direcciones de los datos contenidos en memoria de programa. ¾ El Secuenciador evalúa las instrucciones condicionales y las condiciones de terminación de los bucles usando la información contenida en los registros de estado. ¾ La Pila de direcciones de bucles y la Pila de contadores de bucles permiten los bucles anidados. ¾ La Pila de estado almacena los registros de estado para implementar rutinas de atención a interrupciones anidadas. AQUITECTURA DEL SECUENCIADOR 6 REGISTROS DEL SECUENCIADOR ¾ Todos los registros del Secuenciador de Programa son registros universales y, por tanto, accesibles desde otros registros universales así como también desde memoria de datos. ¾ Todos los registros y las cimas de las pilas se pueden leer. Todos los registros excepto el registro de dirección de búsqueda, registro de dirección de decodificación y el registro PC se pueden escribir. ¾ En la pila del PC se pueden introducir y sacar datos escribiendo en el puntero de pila del PC, el cual se puede leer y escribir en él. ¾ En las pilas de direcciones de bucles y de estado se introducen y sacan datos mediante instrucciones explícitas. ¾ Las instrucciones de manipulación de bits de registros del sistema (Grupo IV) se pueden usar para poner a uno, poner a cero, cambiar o comprobar bits específicos de los registros del sistema. REGISTROS DEL SECUENCIADOR ¾ Debido a la estructura segmentada o ”pipeline”, las escrituras en algunos de estos registros no tienen efecto en el siguiente ciclo, por ejemplo, si escribimos en el registro MODE1 en el bit correspondiente que habilita el modo saturación de la ALU, el cambio de modo no tendrá lugar hasta dos ciclos después de la escritura. ¾ También algunos registros no se actualizan en el ciclo inmediatamente después de la escritura, necesitan un ciclo extra antes de que pueda ser leído el nuevo valor. ¾ En la tabla se resume el número de ciclos extra para que una escritura tenga efecto (effect latency) y para que el nuevo valor aparezca en el registro (read latency). ¾ Un “0” indica que la escritura tiene efecto o aparece en el registro en el siguiente ciclo después de que la instrucción de escritura sea ejecutada. Un “1” indica un ciclo extra. 7 REGISTROS DEL SECUENCIADOR OPERACIONES DEL SECUENCIADOR ¾ En este apartado se pretende dar una visión general del modo de operación del Secuenciador de Programa, para ello se definen los diferentes tipos de flujo del programa que serán descritos más detalladamente en los siguientes apartados. FLUJO SECUENCIAL DE INSTRUCCIONES ¾ EL Secuenciador de Programa determina la dirección de la siguiente instrucción a ejecutar, examinando por un lado la instrucción que en el ciclo actual está siendo ejecutada y el estado actual del procesador. Si no existen condiciones, el procesador ejecuta instrucciones almacenadas en la memoria de programa en orden secuencial simplemente incrementando la dirección de búsqueda. ACCESO A DATOS EN MEMORIA DE PROGRAMA ¾ Normalmente el procesador busca una instrucción en la memoria en cada ciclo. Cuando el procesador ejecuta una instrucción que necesita leer o escribir un dato en el mismo bloque de memoria en el que está almacenada la instrucción, se produce un conflicto en el acceso a este bloque. 8 OPERACIONES DEL SECUENCIADOR ¾ El procesador utiliza su caché de instrucciones para disminuir los retrasos ocasionados por este tipo de conflictos. ¾ La primera vez que el procesador encuentra una búsqueda de instrucción que entra en conflicto con un acceso a dato en memoria de programa, debe esperar a realizar la búsqueda de instrucción en el siguiente ciclo, ocasionando un retraso. Entonces el procesador automáticamente escribe la instrucción buscada en la caché para evitar que el mismo retraso se produzca otra vez. ¾ En cada acceso a datos en memoria de programa el procesador comprueba la caché de instrucciones, si la instrucción necesitada está disponible en la caché, la búsqueda de la instrucción ocurre en paralelo con el acceso al dato en memoria de programa, sin incurrir en ningún retraso. BIFURCACIONES ¾ Una bifurcación ocurre cuando la dirección de búsqueda no es la dirección siguiente a la dirección de búsqueda previa. OPERACIONES DEL SECUENCIADOR ¾ Los tipos de bifurcaciones que los procesadores de la familia ADSP-2106x soportan son saltos y llamadas y retornos de subrutinas. ¾ En el Secuenciador de Programa la única diferencia entre un salto y una llamada a subrutina es que antes de ejecutar la llamada a subrutina se guarda en la Pila del PC la dirección de retorno que está disponible, por tanto, cuando más tarde se ejecuta una instrucción de retorno. (Las instrucciones de salto transfieren el flujo a una nueva posición sin permitir el retorno). BUCLES ¾ Los procesadores de la familia ADSP-2106x implementan los bucles mediante la instrucción DO UNTIL. ¾ Esta instrucción da lugar a que una secuencia de instrucciones se repita hasta que al evaluar la condición especificada sea verdadera. 9 EJECUCION CONDICIONAL ¾ El Secuenciador de Programa evalúa condiciones para determinar cuando ejecutar una instrucción condicional o cuando terminar un bucle. ¾ Las condiciones se basan en la información proveniente del registro de estado aritmético (ASTAT), del registro de modo (MODE1), los flags de entrada y el contador de bucles. ¾ Cada condición que puede evaluar el procesador tiene asociado un nemónico en lenguaje ensamblador y un código que es usado en el código de operación de las instrucciones condicionales. ¾ Para la mayoría de las condiciones el secuenciador de programa puede comprobar los estados verdadero y falso, es decir, igual a cero o distinto de cero. ¾ El flag BTF (bit test flag) es el bit 18 del registro ASTAT. Este flag se modifica en función de los resultados generados por las instrucciones BIT TST o BIT XOR (subgrupo de instrucciones de manipulación de bits de los registros del sistema) que se usan para comprobar el contenido de los registros del sistema. EJECUCION CONDICIONAL ¾ Una vez que este flag BTF ha sido modificado por una de estas instrucciones (BIT) puede ser usado como condición en una instrucción condicional. ¾ Las dos condiciones que no tienen complementaria son LCE/NOT LCE y TRUE/FOREVER. El significado de estas condiciones viene determinado por el contexto; TRUE y NOT LCE se usan en instrucciones condicionales; FOREVER y LCE en condiciones de terminación de bucles. ¾ La estructura IF TRUE crea una instrucción incondicional, es decir, produce el mismo efecto que quitar completamente la condición. ¾ La estructura DO FOREVER ejecuta un bucle indefinidamente hasta que ocurre una interrupción o un reset. ¾ En la instrucción DO UNTIL la condición normalmente usada es LCE (esta condición comprueba el valor del contador de bucles CURLCNTR). ¾ La condición Bus Master (BM) indica cuando el procesador funcionando en un sistema multiprocesador, es actualmente el Bus Master. Para habilitar el uso de esta condición es necesario que los bits 17 y 18 del registro MODE1 sean ambos igual a cero, en caso contrario la condición es siempre evaluada como falsa. 10 EJECUCION CONDICIONAL BIFURCACIONES ¾ Tanto los saltos como las llamadas a subrutinas transfieren el flujo del programa a otra dirección de memoria, pero una llamada a subrutina almacena en la Pila del PC la dirección de retorno, por ello esta dirección está disponible cuando más tarde se ejecuta la instrucción de retorno de subrutina. ¾ El retorno da lugar a que el procesador salte a la dirección almacenada en la cima de la Pila del PC. Hay dos tipos de instrucción de retorno: retorno de subrutina (RTS) y retorno de interrupción (RTI). ¾ La diferencia entre los dos radica en que la instrucción RTI no solamente saca de la Pila del PC la dirección de retorno sino que además: 1) Saca de la Pila de Estado los valores guardados de los registros de estado ASTAT y MODE1 si han sido guardados en la pila (esto ocurre con las interrupciones IRQ2-0, la interrupción asociada al timer y la interrupción VIRPT). 2) Borra el bit apropiado en el registro IRPTL (latch de interrupciones) y en el puntero a la máscara de interrupciones (IMASKP). 11 BIFURCACIONES ¾ En los saltos se pueden especificar una serie de parámetros: 1) Los saltos y las llamadas y retornos pueden ser condicionales. El Secuenciador de Programa puede evaluar una serie de condiciones de estado para decidir cuando el salto será ejecutado o no. Si no se especifican condiciones el salto será siempre ejecutado. 2) Los saltos y las llamadas a subrutinas pueden ser indirectos, directos y relativos al PC. Un salto indirecto salta a una dirección generada por el Generador de Direcciones DAG2. Los saltos directos saltan a una dirección de 24 bits especificada en un campo inmediato en la propia instrucción de salto. Los saltos relativos al PC también utilizan un valor especificado en la propia instrucción, pero el Secuenciador suma este valor al valor actual del PC para calcular la dirección de salto. 3) Los saltos y las llamadas a subrutinas pueden ser retrasadas y no retrasadas. En un salto retrasado, las dos instrucciones colocadas inmediatamente después de la instrucción de salto se ejecutan; en un salto no retrasado el Secuenciador de programa suprime la ejecución de estas dos instrucciones (en su lugar se ejecutan NOPs). BIFURCACIONES 4) La instrucción JUMP (LA) produce que automáticamente se aborte el bucle, si está dentro de un bucle. Cuando se aborta el bucle se extrae un dato de las Pilas de PC y de Direcciones de Bucles, por tanto si el bucle era anidado, las pilas aún contienen los valores correctos del bucle exterior. JUMP (LA) es similar a la instrucción “Break” disponible en el lenguaje C, que es utilizada para terminar la ejecución de un bucle de forma prematura. (La instrucción JUMP (LA) no puede ser usada en las últimas tres instrucciones del bucle). 12 BIFURCACIONES RETRASADAS Y NO RETRASADAS ¾ El modificador de instrucción (DB) indica que el salto es retrasado, en caso contrario no es retrasado. ¾ Si el salto es no retrasado las dos instrucciones después del salto que están en las etapas de búsqueda y decodificación no se ejecutan. ¾ En una llamada a subrutina la dirección de decodificación (que es la dirección de la instrucción colocada después de la de llamada a subrutina) es la dirección de retorno. ¾ Durante los dos ciclos de No Operación, la primera instrucción colocada en la dirección de salto es buscada y decodificada. ¾ En un salto retrasado el procesador continua ejecutando las dos instrucciones siguientes al salto, mientras la instrucción almacenada en la dirección del salto es buscada y decodificada. ¾ En el caso de una llamada a subrutina la dirección de retorno es la dirección de la tercera instrucción después de la instrucción de llamada. BIFURCACIONES RETRASADAS Y NO RETRASADAS 13 BIFURCACIONES RETRASADAS Y NO RETRASADAS BIFURCACIONES RETRASADAS Y NO RETRASADAS ¾ Un salto retrasado es más eficiente pero dificulta la comprensión del programa debido a estas dos instrucciones entre la instrucción de salto y el salto real. ¾ Debido a la estructura segmentada o “pipeline” una instrucción de salto retrasado y las dos instrucciones siguientes deben ser ejecutadas en orden secuencial. ¾ Por tanto, las instrucciones que se pueden colocar en las dos posiciones siguientes a un salto retrasado no pueden ser las siguientes: ¾ Otros saltos, llamadas a subrutinas o retornos. ¾ Introducir o sacar datos de la Pila del PC. ¾ Escrituras en el Puntero de la Pila del PC. ¾ Instrucción DO UNTIL. ¾ Instrucciones IDLE e IDLE16. 14 BIFURCACIONES RETRASADAS Y NO RETRASADAS ¾ Además estos procesadores no procesan una interrupción que se produzca entre una instrucción de salto retrasado y las dos instrucciones siguientes, puesto que estas tres instrucciones deben ser ejecutadas secuencialmente. ¾ Cualquier interrupción que ocurra durante la ejecución de estas instrucciones es guardada como pendiente y no se inicia su procesamiento hasta que no se completa el salto. ¾ Después de una llamada o retorno de subrutina retrasado si está permitido leer la Pila del PC o el Puntero de Pila del PC, pero estas lecturas muestran que la dirección de retorno ha sido ya introducida o sacada de la Pila del PC a pesar de que el salto aún no se ha ejecutado. PILA DEL PC ¾ La Pila del PC almacena las direcciones de retorno de las subrutinas software, de las subrutinas de atención a interrupción y las direcciones de comienzo de los bucles. ¾ La Pila del PC tiene 30 posiciones cada una de las cuales almacena una dirección de 24 bits. ¾ Se saca un dato de la Pila del PC cada vez que se ejecuta la instrucción de retorno de subrutina de atención a interrupción (RTI) de retorno de subrutina software (RTS) y de terminación de un bucle. ¾ La Pila está llena cuando todas sus posiciones están ocupadas, vacía cuando todas sus posiciones están libres y se produce overflow cuando se ejecuta una instrucción de llamada a subrutina y la Pila está ya llena. ¾ Los flags de vacía y llena están almacenados en el registro de adhesivos (STKY). El flag de pila llena da lugar a una interrupción enmascarable. 15 PILA DEL PC ¾ Esta interrupción ocurre cuando están ocupadas 29 posiciones de la Pila del PC, puesto que al saltar a la subrutina de servicio se almacena una nueva dirección de retorno en la pila que es la que da lugar a pila llena. Por eso la interrupción es pila llena aunque realmente la condición que provoca la interrupción es pila casi llena. ¾ Las otras pilas del secuenciador, la pila de direcciones de bucles, la pila de contadores de bucles y la pila de estado, también provocan interrupciones cuando se produce overflow, pero estas interrupciones se inician cuando se introduce un nuevo dato en ellas y las pilas están ya llenas. ¾ El puntero de Pila del PC (PCSTKP) es un registro que contiene la dirección de la cima de la pila y que puede leerse o escribirse en él. ¾ El valor del puntero PCSTKP es cero cuando la pila está vacía, 1, 2, …30 cuando la pila contiene datos y 31 cuando se produce overflow. ¾ Los datos escritos en el puntero PCSTKP tienen efecto un ciclo después. Si ha ocurrido overflow y escribimos un nuevo valor en el puntero no tiene efecto. BUCLES ¾ La instrucción DO UNTIL proporciona una forma eficiente de implementar los bucles software sin instrucciones adicionales para saltar, comprobar la condición o decrementar el contador: Ejemplo: LCNTR = 30, DO label UNTIL LCE; R0 = DM(I0, M0), F2 = PM(I8,M8); R1 = R0 – R15; label: F4 = F2 + F3; ¾ Cuando el procesador ejecuta la instrucción DO UNTIL, el secuenciador de programa almacena la dirección de la última instrucción del bucle y la condición a comprobar para salir del bucle (ambos especificados en la instrucción) en la pila de direcciones de bucles. ¾ También el procesador almacena la dirección de comienzo del bucle, que es la dirección de la instrucción siguiente a la instrucción DO UNTIL en la Pila del PC. 16 BUCLES BUCLES ¾ Debido a la estructura segmentada o “pipeline” (ciclos de búsqueda, decodificación y ejecución), el procesador comprueba la condición de terminación y, si el bucle es con contador decrementa el contador, antes del final del bucle, por tanto la siguiente búsqueda tanto si es fuera del bucle como si vuelve al comienzo del bucle, está basada en el resultado de la comprobación de la condición. ¾ Concretamente la condición se comprueba cuando se ejecuta la instrucción colocada dos posiciones antes de la última instrucción del bucle (en la posición e-2, siendo e la dirección del final del bucle). ¾ Si la condición de terminación no es verdadera, el procesador busca la instrucción en la dirección de comienzo del bucle, almacenada en la cima de la Pila del PC. ¾ Si la condición de terminación es verdadera, el secuenciador busca la siguiente instrucción en la dirección después del final del bucle y saca un dato de la pila de direcciones de bucles y de la Pila del PC. 17 BUCLES RESTRICCIONES Y BUCLES CORTOS ¾ En esta sección vamos a describir algunas restricciones de programación de los bucles. También explicaremos restricciones que afectan únicamente a los bucles cortos (con una o dos instrucciones) los cuales requieren una consideración especial debido al pipeline de tres etapas: búsqueda, decodificación y ejecución. RESTRICCIONES GENERALES 1) Los bucles anidados no pueden terminar en la misma instrucción. 2) Las tres últimas instrucciones de un bucle no pueden ser una bifurcación (jump, call o return); en caso contrario el bucle puede no ser ejecutado correctamente. Esto también debe aplicarse a los bucles de una única instrucción y los bucles de dos instrucciones con una única iteración. ¾ Hay una excepción a esta regla, una llamada a subrutina no retrasada (sin el modificador DB) seguida de retorno RTS (LR) de subrutina sin abortar el bucle. La llamada a subrutina no retrasada se puede usar como una de las tres últimas instrucciones del bucle (pero no en bucles de una única instrucción o de dos instrucciones y con una única iteración). 18 RESTRICCIONES Y BUCLES CORTOS ¾ La instrucción RTS (LR) asegura el retorno dentro del bucle de forma correcta. En bucles basados en contador, por ejemplo, la condición de terminación del bucle se comprueba decrementando el contador actual del bucle (CURLCNTR) durante la ejecución de la instrucción colocada dos posiciones antes del final del bucle. ¾ Una llamada a subrutina no retrasada se puede colocar en una de las dos últimas instrucciones del bucle siempre que se utilice la instrucción RTS (LR) como retorno de la subrutina. Este modificador (LR) asegura el retorno correcto dentro del bucle, evitando que el contador del bucle se decremente de nuevo, es decir, dos veces en la misma iteración del bucle. BUCLES CON CONTADOR ¾ En los bucles basados en contador, la tercera instrucción desde el final del bucle (e-2) no puede ser una escritura en el contador desde memoria. ¾ Los bucles cortos, con menos de tres instrucciones terminan de una forma especial debido a la estructura segmentada o pipeline de tres etapas. RESTRICCIONES Y BUCLES CORTOS ¾ Los bucles basados en contador con solamente una o dos instrucciones no son suficientemente largos para que el secuenciador compruebe la condición de terminación dos instrucciones antes del final del bucle. ¾ En estos bucles cortos el secuenciador está ya otra vez dentro del bucle cuando se comprueba la condición de terminación. ¾ Para evitar los ciclos adicionales un bucle con una única instrucción debe ser ejecutado al menos tres veces y un bucle con longitud dos instrucciones debe ser ejecutado al menos dos veces. ¾ Los bucles con una única instrucción y una única iteración o dos iteraciones y los bucles con dos instrucciones y una única iteración, incurren en dos ciclos adicionales (NOP) puesto que es necesario abortar dos instrucciones después de la última iteración para limpiar el pipeline. ¾ El procesamiento de una interrupción que ocurre durante la última iteración de un bucle de una única instrucción que se ejecuta una o dos veces o de un bucle de dos instrucciones que se ejecuta una vez o en el ciclo siguiente a estos bucles, es retrasado un ciclo. 19 RESTRICCIONES Y BUCLES CORTOS RESTRICCIONES Y BUCLES CORTOS 20 RESTRICCIONES Y BUCLES CORTOS ¾ De forma similar, en un bucle de una única instrucción con al menos tres iteraciones, el procesamiento de la interrupción es retrasado un ciclo si la interrupción ocurre durante la antepenúltima iteración. BUCLES SIN CONTADOR ¾ Los bucles no basados en contador son aquellos en los cuales la condición de terminación de los bucles es distinta de LCE. ¾ Cuando un bucle sin contador es el bucle externo de una serie de bucles anidados, la dirección del final del bucle externo debe estar localizada al menos dos direcciones después de la dirección final del bucle interno. ¾ La instrucción JUMP (LA) se usa para abortar de forma prematura un bucle. Cuando esta instrucción se coloca en un bucle interno de una serie de bucles anidados y el bucle externo es sin contador, la dirección de salto no puede ser la dirección de la última instrucción del bucle externo. La dirección de salto puede ser, sin embargo, la siguiente a la última o cualquiera más próxima. RESTRICCIONES Y BUCLES CORTOS ¾ Los bucles cortos no basados en contador terminan de una forma especial debido al pipeline de tres etapas: búsqueda, decodificación y ejecución. 1) En un bucle de tres instrucciones la condición de terminación del bucle se comprueba cuando se ejecuta la instrucción de comienzo del bucle. Cuando la condición es verdadera, el secuenciador realiza una iteración completa del bucle antes de salir. 2) En un bucle de dos instrucciones, la condición de terminación del bucle se comprueba durante la ejecución de la segunda y última instrucción. Si la condición se hace verdadera cuando se ejecuta la primera instrucción, se evalúa como verdadera durante la ejecución de la segunda y se realiza una iteración completa antes de salir del bucle. Si la condición se hace verdadera durante la ejecución de la segunda instrucción, se realizan dos iteraciones completas antes de salir del bucle. 3) En un bucle con una única instrucción la condición de terminación se comprueba en cada ciclo de instrucción. Cuando la condición se hace verdadera, el bucle se ejecuta tres veces más antes de salir. 21 PILA DE DIRECCIONES DE BUCLES ¾ La pila de direcciones de bucles tiene 6 posiciones, cada una de las cuales almacena un dato de 32 bits. ¾ Una palabra de 32 bits almacenada en una posición consta de 24 bits correspondientes a la dirección de terminación del bucle, un código de 5 bits que codifica la condición de salida del bucle y un código de 2 bits que codifica el tipo de bucle. PILA DE DIRECCIONES DE BUCLES ¾ La dirección de terminación del bucle, el código de condición de salida del bucle y el código de tipo de bucle son introducidos en la pila de direcciones de bucles cuando se ejecutan las instrucciones DO UNTIL o PUSH LOOP. ¾ Se saca un dato de la pila de direcciones de bucle dos instrucciones antes del final en la última iteración o cuando se ejecuta la instrucción POP LOOP. ¾ Ocurre overflow en la pila de direcciones de bucles cuando se introduce un dato y todas sus posiciones están ocupadas. La pila está vacía cuando no está ocupada ninguna posición. ¾ Los flags de overflow y pila vacía están en el registro de adhesivos. La condición de overflow genera una interrupción enmascarable. ¾ El registro LADDR contiene el valor de la cima de la pila de direcciones de bucles. Este registro se puede leer y se puede escribir a través del bus DM. ¾ Las operaciones de lectura y escritura en el registro LADDR no modifican el puntero de la pila de direcciones de bucles. Sin embargo si se introduce o saca un dato de esta pila mediante instrucciones explícitas si se modifica el puntero. 22 PILA DE DIRECCIONES DE BUCLES ¾ Puesto que la condición de salida del bucle se comprueba dos instrucciones antes del final del bucle, se saca una palabra de la pila de direcciones de bucles antes del final del bucle en la última iteración. Si se lee el registro LADDR en estas últimas instrucciones ya no contiene la dirección de terminación del bucle. ¾ Si se ejecuta una instrucción de salto a una dirección fuera de un bucle especificando el modificador de “abortar bucle” JUMP (LA), esta instrucción saca un dato de la pila de direcciones de bucles (y también de la pila de contadores de bucles si es un bucle basado en contador). Esto permite que el mecanismo de los bucles continue funcionando correctamente. ¾ Es importante tener en cuenta que el modificador (LA) de la instrucción de salto únicamente saca un dato de la pila de direcciones de bucles, por tanto no se puede utilizar para saltar más de un nivel en bucles anidados. PILA DE CONTADORES DE BUCLES ¾ La pila de contadores de bucles tiene 6 posiciones, cada una de las cuales almacena un dato de 32 bits. ¾ La pila de contadores de bucles trabaja sincronizada con la pila de direcciones de bucles; ambas pilas tienen siempre el mismo número de posiciones ocupadas. Por tanto, los flags de overflow y pila vacía son los mismos para estas dos pilas. ¾ El secuenciador de programa de los procesadores ADSP-2106x mantiene dos contadores de bucles independientes: el contador de bucles actual (CURLCNTR) que mantiene las iteraciones para el bucle que está siendo ejecutado y el contador de bucles (LCNTR) que mantiene el valor del contador antes de que comience a ejecutarse el bucle. ¾ Ambos contadores son necesarios para mantener el valor del contador de un bucle externo cuando se inicializa el contador de un bucle interno. 23 PILA DE CONTADORES DE BUCLES CURLCNTR ¾ La cima de la pila de contadores de bucles siempre contiene el valor del contador del bucle que actualmente se está procesando. Este valor es el del registro CURLCNTR, el cual se puede leer y escribir a través del bus DM. ¾ Si se efectúa una lectura del registro CURLCNTR cuando la pila de contadores de bucle está vacía, el valor leído es 0xffffffff. ¾ El secuenciador de programa decrementa el valor del registro CURLCNTR en cada iteración del bucle. Puesto que la condición de salida del bucle se comprueba dos instrucciones antes del final del bucle, el contador del bucle también se decrementa antes del final del bucle. Si en las dos últimas instrucciones del bucle se lee el valor del registro CURLCNTR, el valor leído es el valor del contador en la siguiente iteración. ¾ Se saca una palabra de la pila de contadores de bucles dos instrucciones antes del final del bucle en la última iteración. PILA DE CONTADORES DE BUCLES ¾ Cuando se saca un dato de la pila de contadores de bucles, el valor que queda en la cima de la pila se convierte en el nuevo CURLCNTR, el contador del bucle que en este momento se está ejecutando. Si no se está ejecutando ningún bucle, el valor del registro CURLCNTR es 0xffffffff. ¾ Una escritura en el registro CURLCNTR no provoca que se introduzca un nuevo dato en la pila de contadores de bucles. Por esta razón si escribimos un nuevo valor en el registro CURLCNTR estamos cambiando el valor del contador del bucle que está actualmente en ejecución. Si esta escritura tiene lugar cuando no hay ninguna instrucción DO UNTIL LCE ejecutándose no tiene ningún efecto. ¾ Puesto que estos procesadores utilizan el registro CURLCNTR para implementar los bucles basados en contador, existen ciertas restricciones cuando se quiere escribir en este registro: la antepenúltima instrucción de un bucle basado en contador no puede ser una escritura desde memoria en el registro CURLCNTR y la siguiente instrucción a una escritura desde memoria en el registro CURLCNTR no puede ser una instrucción IF NOT LCE. 24 PILA DE CONTADORES DE BUCLES LCNTR ¾ LCNTR es el valor de la cima de la pila más uno, es decir, es el valor de la pila que tendrá efecto cuando se introduzca un nuevo dato en la pila. ¾ Para inicializar el contador de un bucle anidado sin afectar al valor del contador del bucle que actualmente se está procesando, se escribe el nuevo valor en LCNTR. Si LCNTR se inicializa con el valor cero provoca que el bucle se ejecute 232 iteraciones. ¾ La instrucción DO UNTIL LCE coloca el valor del registro LCNTR en la pila de contadores de bucles, de esta forma se convierte en el nuevo CURLCNTR. El valor anterior del registro CURLCNTR queda almacenado una posición más abajo en esta misma pila. ¾ Si leemos el registro LCNTR cuando la pila de contadores de bucles está llena, el valor leído no es válido. Además cuando la pila de contadores de bucles esta llena las escrituras sobre LCNTR no tienen efecto. PILA DE CONTADORES DE BUCLES 25 TIMER ¾ La familia de procesadores ADSP-2106x incluye un programable capaz de generar interrupciones periódicas. temporizador ¾ El control de la operación del timer se realiza mediante un bit del registro MODE2 y la programación del intervalo de tiempo que debe generar se realiza escribiendo determinados valores en sus dos registros asociados, TPERIOD y TCOUNT. ¾ El valor almacenado en el registro TPERIOD determina la frecuencia de las interrupciones del timer. El número de ciclos entre interrupciones es TPERIOD+1. El máximo valor de TPERIOD es 232-1 (por ejemplo, si el ciclo de reloj es de 50 ns, el máximo intervalo entre interrupciones es 214,75 segundos). ¾ Una señal de salida externa, TIMEXP, informa a los dispositivos externos que la temporización programada en el timer ha finalizado. TIMER ¾ El registro TCOUNT es el contador del timer. El timer decrementa el registro TCOUNT con cada ciclo de reloj. Cuando el registro TCOUNT llega a cero, el timer genera una interrupción y pone a 1 la salida TIMEXP durante 4 ciclos de reloj (cuando el temporizador está habilitado). En el siguiente ciclo de reloj después de que TCOUNT haya llegado a cero, el temporizador automáticamente recarga TCOUNT con el contenido de TPERIOD. 26 TIMER HABILITAR/INHABILITAR EL TIMER ¾ Para iniciar y parar el timer se debe habilitar e inhabilitar mediante el bit TIMEN del registro MODE2. ¾ Con el timer inhabilitado, se debe cargar un valor inicial en el registro TCOUNT y TPERIOD con el número de ciclos correspondiente en función del intervalo de tiempo deseado. Cuando se habilita el timer comienza la temporización. ¾ Al salir de reset el bit que habilita el timer del registro MODE2 está a cero, por lo que el timer está inhabilitado (no decrementa el registro TCOUNT y no genera interrupciones). Cuando el bit de habilitación del timer se pone a 1, el timer comienza a decrementar TCOUNT al final del siguiente ciclo de reloj. Si posteriormente este bit se borra, el timer se inhabilita y deja de decrementar después del siguiente ciclo de reloj. TIMER 27 TIMER INTERRUPCIONES DEL TIMER ¾ Cuando TCOUNT llega a cero, el timer genera dos interrupciones, una con una prioridad relativamente alta y otra con una prioridad relativamente baja. Después de reset, las dos interrupciones están enmascaradas. ¾ Se debe desenmascarar únicamente la interrupción que tiene la prioridad requerida, dejando enmascarada la otra. (La prioridad de las interrupciones determina qué interrupción va a ser atendida primero cuando se producen dos interrupciones en el mismo ciclo. También afecta a las interrupciones anidadas, cuando el anidamiento está habilitado, sólo las interrupciones con mayor prioridad pueden interrumpir a una subrutina de atención a interrupción que se está ejecutando). TIMER INTERRUPCIONES DEL TIMER ¾ Al igual que el resto de interrupciones, la interrupción del timer requiere dos ciclos de reloj para buscar y decodificar la primera instrucción de la subrutina de atención. La subrutina de atención comienza por tanto a ejecutarse cuatro ciclos de reloj después de que el contador haya llegado a cero. 28 TIMER REGISTROS DEL TIMER ¾ Los dos registros del timer, TCOUNT y TPERIOD se pueden leer y escribir mediante las transferencias con registros universales. ¾ La lectura de estos registros no interfiere con el timer. ¾ Una escritura explícita en el registro TCOUNT tiene prioridad sobre tanto la carga de TCOUNT desde TPERIOD como sobre el decremento de TCOUNT. ¾ Ninguno de los dos registros, TCOUNT y TPERIOD, toman valores iniciales después de reset, por ello se deben siempre inicializar ambos después de reset y antes de habilitar el timer. FLAGS DE LAS PILAS ¾ El registro de adhesivos contiene los flags de pila llena y pila vacía para la pila del PC, así como también flags de overflow y flags de pila vacía para las pilas de estado y de bucles. ¾ Al contrario que otros bits del registro de adhesivos, varios de estos flags no son adhesivos: se ponen a uno cuando se activa la condición correspondiente y se ponen a cero cuando la condición cambia (mediante una operación push o pop o por un reset del procesador). ¾ Los flags asociados a la pila de estado son únicamente de lectura. Las escrituras en el registro de adhesivos no tienen efecto sobre estos bits. ¾ La utilidad de los flags de overflow y pila llena es únicamente como ayuda al diagnóstico ya que no es posible recuperar datos cuando se produce overflow. ¾ Cuando se produce overflow en las pilas de estado y de bucles o se llena la pila del PC, esto genera una interrupción en el procesador. 29 FLAGS DE LAS PILAS ¾ Los flags que indican pila vacía facilitan la tarea de salvar las pilas en memoria. Monitorizando los flags de pila vacía cuando se está salvando una pila en memoria, podemos conocer cuando todos los valores almacenados en la pila has sido salvados. ¾ Los flags que indican pila vacía no generan interrupciones puesto que una pila vacía es una condición de funcionamiento aceptable. INSTRUCCIONES IDLE & IDLE16 ¾ Las instrucciones IDLE & IDLE16 son dos instrucciones especiales que paran el núcleo del procesador y lo introducen en un modo de bajo consumo hasta que se active una interrupción externa (IRQ2-0), la interrupción interna asociada al timer, una interrupción DMA o la interrupción del modo multiprocesador VIRPT. ¾ Cuando el procesador ejecuta una instrucción IDLE, busca una instrucción más en la dirección actual de búsqueda y después suspende las operaciones. ¾ El procesador de E/S de la familia ADSP-2106x no se ve afectado por la ejecución de la instrucción IDLE, cualquier transferencia DMA desde o hacia memoria interna no se ve interrumpida. ¾ El reloj interno del procesador continua funcionando durante la ejecución de la instrucción IDLE, así como también el timer, si está habilitado. ¾ Cuando ocurre una interrupción externa (IRQ2-0), la interrupción interna asociada al timer, una interrupción DMA o la interrupción del modo multiprocesador VIRPT el procesador responde normalmente. 30 INSTRUCCIONES IDLE & IDLE16 ¾ Una vez transcurridos los dos ciclos de reloj necesarios para buscar y decodificar la primera instrucción de la subrutina de servicio, el procesador continua ejecutando instrucciones normalmente. ¾ Solamente en el procesador ADSP-21061, la instrucción IDLE16 ejecuta un NOP e introduce al procesador en un modo de bajo consumo. IDLE16 es una versión de menor consumo de IDLE. ¾ La instrucción IDLE16 detiene la ejecución de instrucciones en el procesador, igual que IDLE, y además en este caso el reloj interno funciona a una frecuencia 1/16 la frecuencia de CLKIN. El procesador de E/S continua funcionando, pero todas las operaciones se realizan a una frecuencia 1/16 (todas las transferencias con memoria interna requieren 15 ciclos extra). ¾ El procesador permanece en este modo de bajo consumo hasta que se activa una interrupción. ¾ Después del retorno de la interrupción, la ejecución continua en la instrucción siguiente a IDLE o IDLE16. CACHE DE INSTRUCCIONES ¾ Los procesadores de la familia ADSP-2106x disponen de una memoria caché interna, asociativa, capaz de almacenar hasta 32 instrucciones. El modo de funcionamiento de la caché es totalmente transparente al programador. ¾ La memoria caché almacena únicamente las instrucciones cuya búsqueda entra en conflicto con el acceso a datos en memoria de programa ( a través del bus PMD y con direcciones generadas por el DAG2 sobre el bus PMA). Esta característica hace que la caché sea considerablemente más eficiente que si almacenara todas las instrucciones, puesto que, normalmente sólo un conjunto reducido de instrucciones acceden a datos almacenados en memoria de programa. ¾ Debido a la estructura segmentada en tres etapas, si la instrucción almacenada en la dirección n accede a un dato en memoria de programa, se producirá un conflicto con la búsqueda de la instrucción almacenada en la dirección n+2, suponiendo ejecución secuencial. La instrucción almacenada en la dirección n+2 es la que se guarda en la caché y no la instrucción que accede a un dato en memoria de programa. 31 CACHE DE INSTRUCCIONES ¾ Si la instrucción que se busca está disponible en la caché, ésta proporciona la instrucción mientras se realiza el acceso al dato en memoria de programa. Si la instrucción que se busca no está disponible en la caché entonces está búsqueda se realiza en el ciclo siguiente al acceso al dato en memoria de programa, incurriendo en un ciclo de penalización. Esta instrucción se almacena en la caché, si la caché esta habilitada y no congelada y, por tanto, estará disponible la próxima vez que se ejecute. ¾ La caché consta de 32 entradas y cada entrada consta de un par de registros que contienen una instrucción y su dirección. Cada entrada tiene asociado un bit de validación, si este bit está a 1 indica que dicha entrada contiene una instrucción válida. ¾ Las entradas están divididas en 16 grupos (numerados de 0 a 15) de dos entradas cada uno (entrada 0 y entrada 1). Cada grupo tiene asociado un bit LRU (Least Recently Used) que indica cual de las dos entradas contiene la instrucción más recientemente usada. ¾ Habitualmente el funcionamiento de la caché y su eficiencia es transparente al programador, sin embargo algunas situaciones pueden degradar la eficiencia de la caché y pueden ser fácilmente corregidas modificando el programa adecuadamente. CACHE DE INSTRUCCIONES 32