ETSEIAT-UPC EXAMEN FINAL CIRCUITOS ELECTRÓNICOS

Anuncio

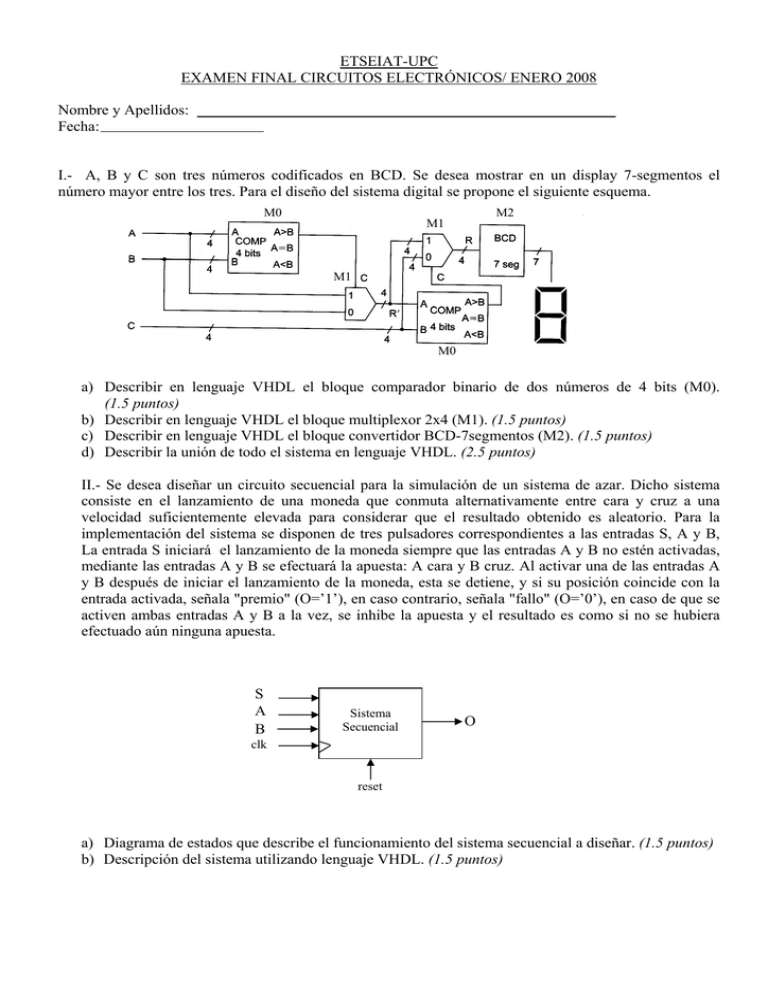

ETSEIAT-UPC EXAMEN FINAL CIRCUITOS ELECTRÓNICOS/ ENERO 2008 Nombre y Apellidos: Fecha: I.- A, B y C son tres números codificados en BCD. Se desea mostrar en un display 7-segmentos el número mayor entre los tres. Para el diseño del sistema digital se propone el siguiente esquema. M0 M2 M1 M1 M0 a) Describir en lenguaje VHDL el bloque comparador binario de dos números de 4 bits (M0). (1.5 puntos) b) Describir en lenguaje VHDL el bloque multiplexor 2x4 (M1). (1.5 puntos) c) Describir en lenguaje VHDL el bloque convertidor BCD-7segmentos (M2). (1.5 puntos) d) Describir la unión de todo el sistema en lenguaje VHDL. (2.5 puntos) II.- Se desea diseñar un circuito secuencial para la simulación de un sistema de azar. Dicho sistema consiste en el lanzamiento de una moneda que conmuta alternativamente entre cara y cruz a una velocidad suficientemente elevada para considerar que el resultado obtenido es aleatorio. Para la implementación del sistema se disponen de tres pulsadores correspondientes a las entradas S, A y B, La entrada S iniciará el lanzamiento de la moneda siempre que las entradas A y B no estén activadas, mediante las entradas A y B se efectuará la apuesta: A cara y B cruz. Al activar una de las entradas A y B después de iniciar el lanzamiento de la moneda, esta se detiene, y si su posición coincide con la entrada activada, señala "premio" (O=’1’), en caso contrario, señala "fallo" (O=’0’), en caso de que se activen ambas entradas A y B a la vez, se inhibe la apuesta y el resultado es como si no se hubiera efectuado aún ninguna apuesta. S A B Sistema Secuencial O clk reset a) Diagrama de estados que describe el funcionamiento del sistema secuencial a diseñar. (1.5 puntos) b) Descripción del sistema utilizando lenguaje VHDL. (1.5 puntos) ETSEIAT-UPC EXAMEN FINAL CIRCUITOS ELECTRÓNICOS/ ENERO 2008 Nombre y Apellidos: Fecha: I.- A, B y C son tres números codificados en BCD. Se desea mostrar en un display 7-segmentos el número mayor entre los tres. Para el diseño del sistema digital se propone el siguiente esquema. M0 M2 M1 M1 M0 a) Describir en lenguaje VHDL el bloque comparador binario de dos números de 4 bits (M0). (1.5 puntos) library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Comparador is port(A,B : in std_logic_vector (3 downto 0); AmayorB : out std_logic); end Comparador; architecture Behavioral of Comparador is begin AmayorB <='1' when A>B else '0'; end Behavioral; b) Describir en lenguaje VHDL el bloque multiplexor 2x4 (M1). (1.5 puntos) library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Mux2x4 is port(A,B : in std_logic_vector (3 downto 0); S : in std_logic; Y: out std_logic_vector (3 downto 0)); end Mux2x4; architecture Behavioral of Mux2x4 is begin Y<=A when S ='1' else B; end Behavioral; c) Describir en lenguaje VHDL el bloque convertidor BCD-7segmentos (M2). (1.5 puntos) library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Convertidor_BCD_7seg is port( N : in std_logic_vector (3 downto 0); display: out STD_LOGIC_VECTOR (6 downto 0)); end Convertidor_BCD_7seg; architecture Behavioral of Convertidor_BCD_7seg is begin with N select display<="1111110" when "0000", "0110000" when "0001", "1101101" when "0010", "1111001" when "0011", "0110011" when "0100", "1011011" when "0101", "1011111" when "0110", "1110000" when "0111", "1111111" when "1000", "1111011" when "1001", "-------" when others; end Behavioral; d) Describir la unión de todo el sistema en lenguaje VHDL. (2.5 puntos) library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ejercicio1 is Port ( A : in STD_LOGIC_VECTOR (3 downto 0); B : in STD_LOGIC_VECTOR (3 downto 0); C : in STD_LOGIC_VECTOR (3 downto 0); display : out STD_LOGIC_VECTOR (6 downto 0)); end ejercicio1; architecture Behavioral of ejercicio1 is Component Comparador port(A,B : in std_logic_vector (3 downto 0); AmayorB : out std_logic); End Component; Component Mux2x4 port(A,B : in std_logic_vector (3 downto 0); S : in std_logic; Y: out std_logic_vector (3 downto 0)); End Component; Component Convertidor_BCD_7seg port( N : in std_logic_vector (3 downto 0); display: out STD_LOGIC_VECTOR (6 downto 0)); End Component; signal C1 : std_logic; signal C2 : std_logic; signal R1 : std_logic_vector (3 downto 0); signal R2 : std_logic_vector (3 downto 0); begin U1: Comparador port map (A,B,C1); U2: Mux2x4 port map (A,B,C1,R1); U3: Comparador port map (R1,C,C2); U4: Mux2x4 port map (R1,C,C2,R2); U5: Convertidor_BCD_7seg port map (R2,display); end Behavioral; II.- Se desea diseñar un circuito secuencial para la simulación de un sistema de azar. Dicho sistema consiste en el lanzamiento de una moneda que conmuta alternativamente entre cara y cruz a una velocidad suficientemente elevada para considerar que el resultado obtenido es aleatorio. Para la implementación del sistema se disponen de tres pulsadores correspondientes a las entradas S, A y B, La entrada S iniciará el lanzamiento de la moneda siempre que las entradas A y B no estén activadas, mediante las entradas A y B se efectuará la apuesta: A cara y B cruz. Al activar una de las entradas A o B después de iniciar el lanzamiento de la moneda, esta se detiene, y si su posición coincide con la entrada activada, señala "premio" (O=’1’), en caso contrario, señala "fallo" (O=’0’), en caso de que se activen ambas entradas A y B a la vez, se inhibe la apuesta y el resultado es como si no se hubiera efectuado aún ninguna apuesta. S A B Sistema Secuencial O clk reset a) Descripción del sistema utilizando lenguaje VHDL. (1.5 puntos) Diagrama de estados: SAB X00 X11 Cara 0 100 0XX 101 110 X00 X11 X10 X01 100 Fallo 0 Reset Cruz 0 0XX 101 110 X10 Premio 1 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ejercicio2 is Port ( S : in STD_LOGIC; A : in STD_LOGIC; B : in STD_LOGIC; CLK : in STD_LOGIC; Reset : in STD_LOGIC; O : out STD_LOGIC); end ejercicio2; architecture Behavioral of ejercicio2 is --Definimos un tipo con los estados posibles type estados_posibles IS (fallo,premio,cara,cruz); --Declaramos una señal que puede tomar cualquiera de los estados posibles signal estado: estados_posibles; begin --Definimos un proceso sensible al reloj y al reset para modificar el estado. process(CLK, Reset) begin --Reset asíncrono de nivel activo alto. if (Reset='1') then estado <= fallo; elsif (CLK 'event and CLK='1') then case estado is when fallo => --Estado fallo. if (S='0' and A='0' and B='0') then estado <= cara; end if; when cara => --Estado cara. if (A='0' and B='1') then estado <= fallo; elsif (A='1' and B='0') then estado <= premio; else estado <= cruz; end if; when cruz => --Estado cruz. if (A='1' and B='0') then estado <= fallo; elsif (A='0' and B='1') then estado <= premio; else estado <= cara; end if; when premio => --Estado premio. if (S='0' and A='0' and B='0') then estado <= cara; end if; end case; end if; end process; --Ahora en función del estado, generamos la salida O<='1' when (estado = premio) else '0'; end Behavioral;