0 1 i ni iaR N - Facultad de Ingeniería Mecánica

Anuncio

1

ELECTRONICA DIGITAL DISCRETA Y

PROGRAMABLE

(10 Hrs)

CAPITULO

5

Objetivo: El estudiante enunciará los fundamentos del diseño de circuitos lógicos y sus aplicaciones

más comunes. Conocerá y aplicara la electrónica digital programable enfocada al uso de un

microcontrolador.

5.1 Sistemas de numeración: decimal, binario y hexadecimal.

Numeración

Sistema de símbolos o signos utilizados para expresar los números.

Numeración Arábiga

El sistema corriente de notación numérica que es utilizado hoy y en casi todo el mundo es la

numeración arábiga. Este sistema fue desarrollado primero por los hindúes y luego por los árabes

que introdujeron la innovación de la notación posicional.

Notación posicional.

La notación posicional solo es posible si existe un número para el cero. El guarismo 0 permite

distinguir entre 11, 101 y 1001 sin tener que agregar símbolos adicionales.

En la notación posicional los números cambian su valor según su posición, por ejemplo el digito 2 en

el número 20 y el mismo digito en el 2,000 toma diferente valor.

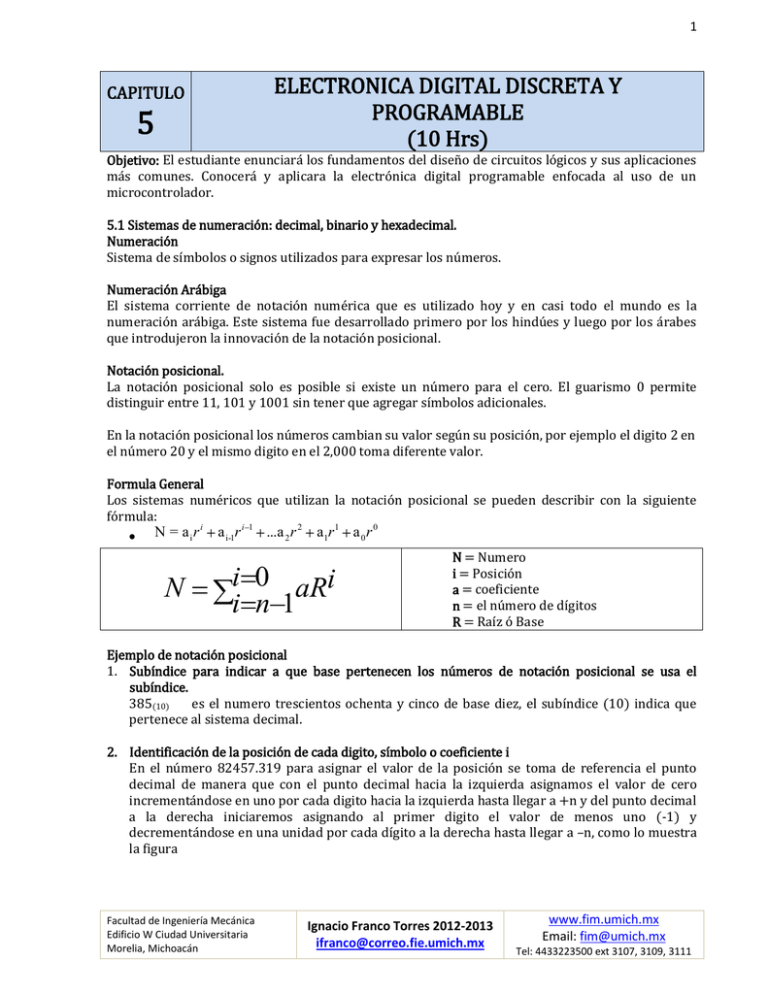

Formula General

Los sistemas numéricos que utilizan la notación posicional se pueden describir con la siguiente

fórmula:

N = a ir i

N

a i-1r i 1 ...a 2 r 2 a1r 1 a 0 r 0

i 0 aRi

i n1

N = Numero

i = Posición

a = coeficiente

n = el número de dígitos

R = Raíz ó Base

Ejemplo de notación posicional

1. Subíndice para indicar a que base pertenecen los números de notación posicional se usa el

subíndice.

385(10)

es el numero trescientos ochenta y cinco de base diez, el subíndice (10) indica que

pertenece al sistema decimal.

2. Identificación de la posición de cada digito, símbolo o coeficiente i

En el número 82457.319 para asignar el valor de la posición se toma de referencia el punto

decimal de manera que con el punto decimal hacia la izquierda asignamos el valor de cero

incrementándose en uno por cada digito hacia la izquierda hasta llegar a +n y del punto decimal

a la derecha iniciaremos asignando al primer digito el valor de menos uno (-1) y

decrementándose en una unidad por cada dígito a la derecha hasta llegar a –n, como lo muestra

la figura

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

2

Aplicación de la Formula General

Ejemplo 385(10)

En donde el digito 5 ocupa la posición cero, el 8 la uno y el 3 la posición dos,

como lo indica la figura.

Al aplicar la fórmula general obtenemos:

N = 3 102

8 101 5 100

300 80 5 385

N

i 0 aRi

i n 1

En donde se puede observar que el número adquiere valor dependiendo la posición que guarde,

como el 3 que está en la posición 2 se multiplica por 100 que es 102como lo llamamos

tradicionalmente centenas, al 8 de posición uno por 101, o decenas al 5 de posición cero 100

unidades.

Además del sistema decimal existen otras bases de notación posicional que son empleadas en los

sistemas digitales como:

Binario o base 2 que consta de solo dos símbolos 0 y 1.

Octal o base 8 consta de ocho símbolos (0, 1, 2, 3, 4, 5, 6, 7) y es una representación corta del

binario y por ejemplo 111101110(2) = 756(8). Para las máquinas es más fácil trabajar con

unos y ceros que representarían voltaje o no voltaje mientras que para nosotros es más

cómodo decir solo 756 en lugar de todo el número binario.

Hexadecimal o base 16 consta de 16 símbolos (0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F), es la

representación corta más usada del binario y Ejemplo 111101111010(2) = F7A(16).

5.1.1 Números binarios

Solo dispone de símbolos “1” y “0” se le llama bit

Bit (Binary unit).Mínima cantidad de información que se puede representar. Tiene 2 valores: 0 y 1.

Para representar más información hay que usar conjuntos de bits. Agrupaciones de bits:

Nibble (4 bits),

Byte (8 bits).

Kilobit (Kbit) (1024 bits),

Kilobyte (Kbyte) (1024 bytes).

64 Kbytes (65536 bytes).

www.fim.umich.mx

Facultad de Ingeniería Mecánica

Ignacio Franco Torres 2012-2013

Edificio W Ciudad Universitaria

Email:

fim@umich.mx

ifranco@correo.fie.umich.mx

Morelia, Michoacán

Tel: 4433223500 ext 3107, 3109, 3111

3

Representación de datos mediante bits:

Colores = {Blanco, Amarillo, Rojo, Verde, Azul, Negro}

Blanco => 000; Verde => 100; Amarillo => 010; Azul => 101; Rojo => 011; Negro =>

111;

¿Cuál es número de bits mínimo que se necesita para representar un conjunto de datos?

1 bit. 2 combinaciones:(0, 1). Hasta 2 datos.

2 bits. 4 combinaciones: (00, 01, 10, 11).

Hasta 4 datos.

3 bits. 8 combinaciones: (000, 001, 010, 011, 100, 101, 110, 111). Hasta 8 datos.

N bits: 2N combinaciones. Hasta 2N datos.

Dado un conjunto de datos de M elementos se necesitan al menos N bits, donde M ≤ 2N, para

codificarlo en binario.

Representación de números en punto fijo. Se supone el punto decimal fijo en una posición.

Normalmente los números se describen en base decimal ó base 10:

En cualquier otra base “r”:

En base 2:

Los términos ai corresponden a los dígitos del número mientras que los términos r(10ió 2i)

corresponden al peso del dígito en el número.

Números en base 10

Números en base 2

Paso de la parte entera de base 10 a base 2 por división iterativa: al dividir un número por la base

aparece el coeficiente más bajo en el resto de la división. Dividir iterativamente hasta que el

cociente de la división sea 0.

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

4

(an ... a3 a2 a1 a0 )/ r = (an ... a3 a2 a1 . a0 )

23/2=11.

11/2=5

5/2=2.

2/2=1.

1/2=0.

Resto 1;

Resto 1;

Resto 1;

Resto 0;

Resto 1;

a0 = 1

a1 = 1

a2 = 1

a3 = 0

a4 = 1.

Fin de División

(23)10 = (10111)2 = 16 + 4 + 2 + 1

Paso de la parte fraccionaria de base 10 a base 2 por división iterativa: al multiplicar un número por

la base aparece el coeficiente más bajo en la parte entera del producto. Multiplicar iterativamente

hasta que la parte fraccionaria del producto sea 0.

(0.a1 a2 a3..an )* r = (a1.a2 a3 .. an )

0.34375 * 2 = 0.6875.

0.6875 * 2 = 1.375.

0.375 * 2 = 0.750.

0.75 * 2 = 1.50.

0.50 * 2 = 1.00.

Parte fraccionaria es 0.

Parte entera 0; a-1 = 0

Parte entera 1; a-2 = 1

Parte entera 0; a-3 = 0

Parte entera 1; a-4 = 1

Parte entera 1; a-5 = 1

Fin de Multiplicación

(0.34375)10 = (0.01011)2

5.1.2 Formato Octal y Hexadecimal

El uso de estas bases reduce el número de dígitos para representar un número binario.

La base 8 (octal) utiliza dígitos de 0 a 7. Se pasa de base 2 a base 8 agrupando los bits de 3 en 3, y de

base 8 a base 2 desagrupando los dígitos de 3 en 3 bits:

(101001110011)2 => (101)(001)(110)(011) => (5 1 6 3)8

(2704)8 => (010)(111)(000)(100) => (10111000100)2

La base 16 (hexadecimal) utiliza dígitos de 0 a 15, para ello toma 0-9, A (10), B (11), C (12), D (13),

E (14) y F (15). Se pasa de base 2 a base 16 agrupando los bits de 4 en 4 y de base 16 a base 2

desagrupando los dígitos de 4 en 4 bits:

(101001110011)2 => (1010)(0111)(0011) => (A 7 3)16

(E51C)16 => (1110)(0101)(0001)(1100) => (1110010100011100)2

5.2Aritmética binaria. (Suma, resta, multiplicación y

división por la base)

5.2.1 Suma Binaria

Cuando sumamos dos operandos A y B de 1 bit se genera

la siguiente tabla según los valores de A y B. En ella 1 + 1

= 2, que debe codificarse en dos bits. Luego hay dos bits

de salida:

Suma S de peso 1.

Acarreo de salida Co (“carryout”) de peso 2.

Cuando sumamos dos operandos A y B de más de 1

bit, su primer bit se suma mediante un semisumador.

El resto de los bits requieren tres bits de suma: los

dos bits de los operandos y la salida de acarreo del bit

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

5

anterior que opera como acarreo de entrada Ci (“carry in”). El máximo valor de la salida es 3 luego

se requieren dos bits de salida como en el semisumador.

Ahora se puede sumar bit por bit desde el menos significativo (LSB, menor peso) hacia el más

significativo (MSB, mayor peso)

0+0=0

0+1=1

1+0=1

1+1=0 y llevamos (Carry) 1

ó sea 1+1=10

Reglas de la Suma

11

+10

101

111

+101

1100

1011 11110 111111 1111101

+1101 +10101 +010101 +1111000

11000 110011 1010100 11110101

Ejemplos

5.2.2 Resta Binaria

Suponemos una resta M-S con dos operandos: Minuendo (M) y Sustraendo (S),

donde M ≥S. Al restar de LSB a MSB en 1 bit puede pasar que S > M (0-1), lo

que obliga a pedir un bit de préstamo B (“Borrow”) al siguiente bit, para

realizar 10-1 = 1.

En el bit que ha realizado el préstamo, se tiene que hacer primero M-B, (con la

posibilidad de generar préstamo de salida), al resultado se le resta S.

Ahora se puede restar bit por bit desde el menos significativo (LSB, menor

peso) hacia el más significativo (MSB, mayor peso)

11

-10

001

111

+101

0010

1011 11110 111111 1111101

+1101 +10101 +010101 +1111000

11110 01001 101010 0001000

Ejemplos

5.2.3 Multiplicación Binaria

Cuando se multiplican dos operandos A y B de 1 bit se genera un resultado de 1 bit según los valores

de A y B.

Para multiplicar operandos de más de 1 bit se utiliza el mismo algoritmo que en la multiplicación

decimal, se generan los productos parciales y luego se suman.

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

6

Ejemplo

5.2.4 División Binaria

Igual que en el producto, la división es muy fácil de realizar, porque no son

posibles en el cociente otras cifras que UNOS y CEROS.

Consideremos el siguiente ejemplo, 42 / 6 = 7, en binario:

Se intenta dividir el dividendo por el divisor, empezando por tomar en ambos

el mismo número de cifras (100 entre 110, en el ejemplo). Si no puede

dividirse, se intenta la división tomando un dígito más (1001 entre 100).

Si la división es posible, entonces, el divisor sólo podrá estar contenido una

vez en el dividendo, es decir, la primera cifra del cociente es un UNO. En ese

caso, el resultado de multiplicar el divisor por 1 es el propio divisor.

Restamos las cifras del dividendo del divisor y bajamos la cifra siguiente.

El procedimiento de división continúa del mismo modo que en el sistema

decimal.

5.3 Elementos del álgebra Booleana. Funciones Booleanas.

5.3.1 Funciones básicas y derivadas.

Funciones en la que las variables independientes son variables lógicas, y el valor de la función o

variable dependiente también es una variable lógica.

Z=f(A,B,C,…,N)

Donde: Z,A,B,C,…, N son variables lógicas

Sirven para la representación de problemas lógicos

Una función lógica es una expresión matemática que evalúa cuando una variable lógica toma el valor

lógico Verdadero en función de los valores (Verdadero o Falso) de otras variables lógicas operados

mediante las operaciones AND, OR y NOT. Normalmente, para escribir las funciones lógicas se usan

los valores (0, 1) y los operadores típicos (- , •, +) del álgebra de conmutación (de mayor a menor

prioridad).

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

7

Puertas Lógicas

• Para una representación circuital de las funciones lógicas se utilizan puertas lógicas. Los circuitos

lógicos se generan como una conexión de puertas lógicas.

Existen:

Funciones lógicas de 1 variable

Funciones lógicas de 2 variables

Se les llama funciones lógicas básicas o puertas lógicas básicas a las funciones: NOT, AND y

OR y funciones lógicas derivadas o puertas lógicas derivadas a las: BUFFER, NAND, NOR,

EXOR, EXNOR ó NEXOR.

Se les llama funciones lógicas universales o puertas lógicas universales: a las NAND y NOR

porque con ellas se pueden construir todas las funciones que se deseen.

Funciones lógicas de más variables como la mostrada para alarma del auto

5.3.2 Algebra Booleana.

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

8

Leyes básicas del Álgebra de Boole:

Leyes conmutativas de la suma y multiplicación.

Leyes asociativas de la suma y multiplicación.

Ley distributiva.

• Son las mismas que las del álgebra ordinaria.

Leyes Conmutativas

•El orden en que se aplica a las variables la operación OR es indiferente:

Ley conmutativa de la suma para dos variables:

• El orden en que se aplica a las variables la operación AND es indiferente:

Ley conmutativa de la multiplicación para dos variables:

Leyes Asociativas

• Al aplicar la operación OR a más de dos variables, el resultado es el mismo independientemente de

la forma en que se agrupen las variables:

Ley asociativa de la suma para tres variables:

• Al aplicar la operación AND a más de dos variables, el resultado es el mismo independientemente

de la forma en que se agrupen las variables:

Ley asociativa de la multiplicación para tres variables:

Ley Distributiva

• Aplicar la operación OR a dos o más variables y luego aplicar la operación AND al resultado de la

operación y a otra variable aislada, es equivalente a aplicar la operación AND a la variable aislada

con cada uno de los sumandos y luego aplicar la operación OR a los productos resultantes.

• Esta ley también expresa el proceso de sacar factor común, en el que la variable común se saca

como factor de los productos parciales.

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

9

Ley distributiva para tres variables:

Reglas Básicas del Álgebra de Boole

• Muy útiles para la manipulación y simplificación de expresiones booleanas.

1

2

3

4

5

6

=1

7

=A

8

=0

9

=A

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

10

10

11

12

=A

=A

Regla 4

=A+(A+ )B

=A+1 B

=A+B

=A+AC+AB+BC

=(A+AC)+AB+BC

=A+AB+BC

=(A+AB)+BC

=A+BC

5.3.3 Funciones booleanas. Un problema lógico se corresponde con un enunciado en el que se

puede describir el problema mediante relaciones (funciones) entre variables que se pueden definir

mediante los valores verdadero y falso (variables lógicas).

La alarma de un coche se enciende cuando se cierran las puertas sin ajustar los cinturones de

seguridad, ó cuando se enciende el motor estando las puertas abiertas.

Al (alarma encendida)

Encendida (V=1), Apagada (F=0)

Pu (puertas cerradas)

Cerrada (V=1), Abierta (F=0)

Ci (cinturón ajustado)

Ajustado (V=1), Suelto (F=0)

Mo (motor encendido)

Encendido (V=1), Apagado (F=0)

Para la resolución del problema hay que plasmar el enunciado de forma

que se pueda expresar como una serie de entradas y salidas de tipo lógico.

Hay dos representaciones de los problemas:

Tabla de Verdad para el problema

5.3.4 Reducción de funciones booleanas. Consiste en aplicar las reglas del algebra booleana

para reducir la función a una mínima expresión

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

11

Para reducir las funciones booleanas se puede usar el algebra de boole o mapas de Karnaugth que es

un método que ayuda a simplificar funciones de muchas variables de una manera más rápida que

con el algebra de boole

Mapa de Karnaugh

Ejemplo de mapa de Karnaugh.

POS

F=A/D+A/C+A/B+BC/D = A

SOP

F=A(B+C+/D)(/B+/C+/D)=

Un mapa de Karnaugh (también conocido como tabla de Karnaugh o diagrama de Veitch, abreviado

como Mapa-K o Mapa-KV) es un diagrama utilizado para la simplificación de funciones algebraicas

Booleanas. El mapa de Karnaugh fue inventado en 1950 por Maurice Karnaugh, un físico y

matemático de los laboratorios Bell.

Los mapas de Karnaugh reducen la necesidad de hacer cálculos extensos para la simplificación de

expresiones booleanas, aprovechando la capacidad del cerebro humano para el reconocimiento de

patrones y otras formas de expresión analítica, permitiendo así identificar y eliminar condiciones

muy inmensas.

El mapa de Karnaugh consiste en una representación bidimensional de la tabla de verdad de la

función a simplificar. Puesto que la tabla de verdad de una función de N variables posee 2N filas, el

mapa K correspondiente debe poseer también 2N cuadrados. Las variables de la expresión son

ordenadas en función de su peso y siguiendo el código Gray, de manera que sólo una de las variables

varía entre celdas adyacentes. La transferencia de los términos de la tabla de verdad al mapa de

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

12

Karnaugh se realiza de forma directa, albergando un 0 ó un 1, dependiendo del valor que toma la

función en cada fila. Las tablas de Karnaugh se pueden utilizar para funciones de hasta 6 variables.

Hay dos formas de obtención de función cuando se agrupan los “1” se le conoce como suma de

productos (SOP) y cuando se agrupan los “0” se le llama producto de sumas, también se les llama

formas CANONICAS, como se muestra en la figura del ejemplo anterior mostrado

5.4 Lógica Programable. Se pretende dar un panorama general de la tecnología digital

programable

5.4.1 Flip-Flop. Estos circuitos son la base de los Circuitos secuenciales

Los circuitos digitales que hasta ahora se han considerado, han sido combinacionales, esto es, las

salidas en cualquier momento dependen por completo de las entradas presentes en ese tiempo.

Aunque cualquier sistema digital es susceptible de tener circuitos combinacionales, la mayoría de

los sistemas que se encuentran en la práctica también incluyen elementos de memoria, los cuales

requieren que el sistema se describa en términos de Lógica Secuencial.

Un diagrama en bloques de un circuito

secuencial consta de un circuito

combinacional al que se conectan

elementos de memoria para formar

una trayectoria de retroalimentación.

Los elementos de memoria son

dispositivos capaces de almacenar

dentro de ellos información binaria. La

información binaria almacenada en los

elementos de memoria se define como

el estado del circuito secuencial.

En los circuitos combinacionales las

Figura 1.1: Modelo de Huffman para un circuito secuencial. salidas son funciones que dependen

únicamente de las entradas actuales al

circuito. Pero sin embargo, en muchos sistemas digitales esto no es suficiente, siendo necesario

además circuitos capaces de almacenar información, puesto que en ellos las salidas no quedan

definidas únicamente por las entradas actuales, sino que dependen también de cuáles fueron los

valores de éstas en el pasado. Se trata de los circuitos secuenciales.

Ejemplos de la utilización de circuitos secuenciales podemos encontrarlos en la vida diaria: relojes

digitales, sistemas de control de semáforos en rutas y líneas férreas, marcadores (deportes).

Todos estos sistemas se caracterizan porque pueden ser descritos utilizando el llamado modelo de

Huffman. Se trata de un modelo estructural que permite la descripción de un circuito secuencial

genérico. Según el modelo, el circuito consta de dos partes: un circuito combinacional C y un

conjunto de elementos de memoria M, como muestra la figura. Pues bien, el valor de las salidas

depende, a través de la función de salida que implementa el circuito combinacional, no sólo de los

valores actuales de las entradas, sino también del contenido actual de los elementos de memoria, En

estos elementos, lo que se almacena es el llamado estado actual del sistema secuencial, que puede

considerarse como su registro histórico, ya que da cuenta de su evolución anterior. El paso desde el

estado actual del sistema a un estado siguiente, viene a su vez definido por la llamada función de

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

13

transición de estados, que también dependerá no sólo de los valores actuales de las entradas, sino

también del propio estado actual.

Centrándonos en la arquitectura de los computadores, componentes básicos como los registros,

memorias y la unidad de control, constituyen circuitos secuenciales, aunque de muy diverso grado

de complejidad.

Los Flip-Flop o biestables. Clasificación.

Un circuito flip-flop puede mantener un estado binario en forma indefinida (en cuanto se suministre

potencia al circuito) hasta que recibe la dirección de una señal de entrada para cambiar de estado.

La diferencia principal entre los diversos tipos de flip-flops está en el número de entradas que

poseen y en la manera en la cual las entradas afectan el estado binario.

Las células elementales de memoria de los circuitos secuenciales se denominan biestables o FlipFlop. Se caracterizan por ser capaces de adoptar dos estados estables, que se corresponden a los

niveles lógicos "0" y "1", que perduran en el tiempo de un modo indefinido, aunque haya

desaparecido la excitación que los originó. Es decir: son capaces de memorizar un bit de

información.

Una estructura con puertas lógicas que consigue el propósito anterior, es un biestable elemental que

tiene únicamente dos posibilidades de almacenamiento: estado 0 (Q=O) y estado 1 (Q=1). La

realimentación entre las salidas y las entradas garantiza la permanencia de la información

almacenada (memorizada) en todo momento del funcionamiento electrónico normal (tensión y

corrientes de alimentación adecuadas). Esto no ocurre en los sistemas combinacionales, donde la

información a la salida de las puertas se desvirtúa necesariamente al eliminar las excitaciones de

entrada.

A las señales de control de los biestables se les llama CK (Clock). Estas señales son generalmente

periódicas (aunque pueden no serlo) y gobiernan la transición de un estado a otro.

Son señales de "sincronismo" que miden el tiempo del circuito. La sincronización es la técnica

principal para hacer evolucionar un circuito secuencial, podemos añadir dos entradas asíncronas de

reset o CLR o CLEAR y set o PRE. El objetivo de estas señales, es que al tener estos dispositivos

información almacenada que en un momento dado puede ser desconocida, se hace necesario el

poderlos inicializar a un valor conocido. Así con la señal CLEAR ponemos a 0 la salida y con la señal

PRE a 1.

Flip Flop tipo SET-RESET (SR)

Como ya se menciono anteriormente, estos circuitos pueden construirse con compuertas NAND o

dos compuertas NOR. Cada circuito forma un flip-flop básico, La conexión y el acoplamiento

cruzado mediante la salida de una compuerta a la entrada de otra constituye una trayectoria de

retroalimentación. Por esta razón los circuitos se clasifican como secuenciales asíncronos. Cada flipflop tiene dos salidas Q y Q negada, y dos entradas, SET para ajustar y RESET para restaurar. A este

tipo de flip-flop se les llama SR.

La operación del FF SR disparado por flanco es similar a la operación analizada anteriormente, con

la diferencia de que el cambio de estado se efectúa en el flanco de bajada del pulso de reloj. El estado

S=R=1 es un estado prohibido.

La tabla característica resume el comportamiento del FF tipo SR disparado por flanco negativo.

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

14

Flip Flop tipo J K

Un flip-flop JK es un refinamiento del SR ya que el estado indeterminado del SR se soluciona en el JK.

Las entradas J y K se comportan como las entradas S y R para ajustar y despejar el flip-flop. Cuando

se aplican señales de entrada en forma simultánea a J como a k, el flip-flop cambia a su estado

complementario, esto es si Q=1, cambia a Q=0 y viceversa.

La operación de un FF tipo J K es muy similar a la de un FF SR. La única diferencia es que no tiene un

estado inválido. Para la condición J=K=1 el FF complementa el estado presente.

La tabla característica resume el comportamiento del FF tipo JK disparado por flanco negativo.

Flip Flop tipo D

El flip-flop tipo D recibe esta denominación debido a su capacidad de transferir "datos" en el flipflop. En forma básica es un flip-flop SR con un inversor en la entrada R, El inversor agregado reduce

el número de entradas de dos a uno.

La operación de un FF tipo D es mucho más simple. Sólo posee una entrada además de la del reloj. Se

le denomina "data" y es muy útil cuando queremos almacenar un dato de un bit (0 o 1).

Si hay un 1 en la entrada D cuando se aplica el pulso de reloj la salida Q toma el valor de 1 (SET) y lo

almacena. Si hay un 0 en la entrada D, cuando se aplica el pulso de reloj la salida toma el valor de 0

(RESET) y lo almacena. El cambio en la salida del FF se efectúa en el flanco de bajada del reloj.

La tabla característica resume el comportamiento del FF tipo D disparado por flanco negativo.

Flip Flop tipo T

Sólo posee una entrada además de la del reloj. Se le denomina "toggle". Si hay un 0 en la entrada T,

cuando se aplica el pulso de reloj la salida mantiene el valor del estado presente. Si hay un 1 se

complementa. El flip-flop tipo T es una versión de una sola entrada del flip-flop JK, el flip-flop T se

obtiene mediante un tipo JK si ambas entradas se unen. La denominación T proviene de la capacidad

del flip-flop para conmutar (toggle), o cambiar de estado. Sin importar el estado presente del flipflop, asume el estado complementario cuando ocurre el pulso de reloj mientras la entrada T es

lógica 1

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

15

La tabla característica resume el comportamiento del FF tipo T disparado por flanco negativo.

Para el caso de los FF disparados por flanco positivo la diferencia es que el cambio de estado ocurre

en la subida del pulso de reloj. La diferencia básica entre flip flops disparados por flanco y los

disparados por nivel, es que en los disparados por flanco los cambios se efectúan en el frente de

bajada o en el de subida del pulso de reloj, y aunque las entradas cambien de valor durante la

duración del pulso, no se efectúan cambios hasta el siguiente pulso de reloj. En los flip-flops

disparados por nivel en cambio, el flip flop responde a los cambios de las entradas mientras el pulso

de reloj está en 1. En cuanto a la representación los FF disparados por nivel no poseen el símbolo >

en la entrada de reloj.

El estado de un flip-flop cambia por un cambio momentáneo en sus entradas. Este cambio se

denomina disparo. En los básicos (RS con compuertas NAND o NOR) se necesitaba un disparo de

entrada definido por un cambio de nivel. Este nivel debe regresar a su nivel inicial antes de aplicar

otro disparo. Los FF con reloj eran disparados por pulsos. La realimentación entre la circuitería

combinacional y el elemento de memoria puede producir inestabilidad, haciendo que el FF pueda

cambiar varias veces durante la duración de un pulso de reloj por lo que el intervalo de tiempo

desde la aplicación del pulso hasta que ocurre la transición de la salida, es un factor crítico. Una

manera de resolver este problema es hacer que los FF sean sensitivos a la transición del pulso más

que a la duración. Una manera de hacerlo da origen los flip flops maestro esclavo.

Flip-Flop maestro-esclavo

Un flip flop maestro-esclavo se construye con dos FF, uno sirve de maestro y otro de esclavo.

Durante la subida del pulso de reloj se habilita el maestro y se deshabilita el esclavo. La información

de entrada es transmitida hacia el FF maestro. Cuando el pulso baja nuevamente a cero se

deshabilita el maestro lo cual evita que lo afecten las entradas externas y se habilita el esclavo.

Entonces el esclavo pasa al el mismo estado del maestro. El comportamiento del flip-flop maestroesclavo que acaba de describirse hace que los cambios de estado coincidan con la transición del

flanco negativo del pulso.

Este tipo de biestables controlados por flanco se diseñan a partir de dos biestables elementales RS

sin entrada de control, conectados en cascada, más cierta lógica combinacional, como se muestra en

la figura. Uno de los biestables trabaja como maestro, y el otro como esclavo. Cuando CK está a 1, la

información de entrada pasa al biestable maestro, mientras que el esclavo permanece cerrado, con

lo que la salida no sufre variación. Cuando CK baja a 0 (flanco de bajada), la información del maestro

pasa al esclavo y se cierra el maestro, con lo cual, los datos que en este instante estén en la entrada

no pueden progresar, mientras que los datos que capturó el maestro y que ahora se transfieren al

esclavo, son los que aparecen a la salida. Cuando CK vuelva a pasar a 1, se cerrará el esclavo con la

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

16

información transferida anteriormente del maestro y que será la que esté presente en la salida, y

éste se volverá a abrir. Luego la transferencia completa de la información, desde la entrada a la

salida, sólo tendrá lugar durante los flancos de bajada de la señal CK.

Flip-Flop disparado por flanco: Otro tipo de FF que sincroniza el cambio de estado durante la

transición del pulso de reloj es el flip flop disparado por flanco. Cuando la entrada de reloj excede un

nivel de umbral específico, las entradas son aseguradas y el FF no se ve afectado por cambios

adicionales en las entradas hasta tanto el pulso de reloj no llegue a cero y se presente otro pulso.

Algunos FF cambian de estado en la subida del pulso de reloj, y otros en el flanco de bajada. Los

primeros se denominaran Flip flop disparados por flanco positivo y los segundos Flip-flops

disparados por flanco negativo. La distinción entre unos y otros se indicará con la presencia o

ausencia de una negación en la entrada de reloj como se muestra en la figura.

El FF JK puede considerarse como el flip flop universal puesto que puede configurarse para obtener

los demás flip-flops. En el cuadro a continuación se muestra el equivalente de cada uno de los tipos

de flip-flop en función del J K.

Circuitos sincrónicos y asincrónicos

Hay dos tipos principales de circuitos secuenciales. Su clasificación depende del temporizado de sus

señales. Un circuito secuencial asíncrono es un sistema cuyo comportamiento puede definirse por el

conocimiento de sus señales en instantes discretos de tiempo.

El comportamiento de un circuito secuencial asíncrono depende del orden en el cual cambian sus

señales de entrada y puede afectarse en cualquier instante de tiempo. Los elementos de memoria

que por lo común se utilizan en los circuitos secuenciales asíncronos son dispositivos de retardo de

tiempo. La capacidad de memoria de un dispositivo de retardo de tiempo se debe al hecho de que

toma un tiempo finito para que la señal se propague a través del dispositivo.

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

17

Un sistema lógico secuencial asíncrono, por definición, debe emplear señales que afecten los

elementos de memoria solo en instantes discretos de tiempo. Una forma de lograr este objetivo es

usar pulsos de duración limitada a través del sistema, de modo que una amplitud de pulso

represente la lógica 1 y otra amplitud (o la ausencia de pulso) represente la lógica 0.

Los sistemas lógicos secuenciales asíncronos utilizan amplitudes fijas, como niveles de voltaje para

señales binarias. La sincronización se logra a través de un dispositivo sincronizador llamado reloj

maestro generador, el cual genera un tren periódico de pulsos de reloj. Los pulsos de reloj se

distribuyen a través del sistema de tal forma que los elementos de memoria están afectados solo por

la llegada del pulso de sincronización.

Ejercitación:

Complete el diagrama de tiempos para un flip-flop JK:

5.4.2 Memorias: RAM, ROM, PROM, EPROM. EEPROM.

RAM son las siglas de random access memory, un tipo de memoria de ordenador a la que se puede

acceder aleatoriamente; es decir, se puede acceder a cualquier byte de memoria sin acceder a los

bytes precedentes. La memoria RAM es el tipo de memoria más común en ordenadores y otros

dispositivos como impresoras.

Hay dos tipos básicos de memoria RAM

RAM dinámica (DRAM)

RAM estática (SRAM)

Los dos tipos de memoria RAM se diferencian en la tecnología que utilizan para guardar los datos, la

memoria RAM dinámica es la más común.

La memoria RAM dinámica necesita actualizarse miles de veces por segundo, mientras que la

memoria RAM estática no necesita actualizarse, por lo que es más rápida, aunque también más cara.

Ambos tipos de memoria RAM son volátiles, es decir, que pierden su contenido cuando se apaga el

equipo.

Coloquialmente el término RAM se utiliza como sinónimo de memoria principal, la memoria que

está disponible para los programas, por ejemplo, un ordenador con 8M de RAM tiene

aproximadamente 8 millones de bytes de memoria que los programas puedan utilizar.

ROM La memoria ROM, (read-only memory) o memoria de sólo lectura, es la memoria que se utiliza

para almacenar los programas que ponen en marcha el ordenador y realizan los diagnósticos. La

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

18

mayoría de los ordenadores tienen una cantidad pequeña de memoria ROM (algunos miles de

bytes).

Aplicaciones de ROM

Tipos De ROM: Hay 5 tipos básicos de ROM, los cuales se pueden identificar como:

ROM: De un modo similar a la memoria RAM, los chips ROM contienen una hilera de filas y

columnas, aunque la manera en que interactúan es bastante diferente. Mientras que RAM

usualmente utiliza transistores para dar paso a un capacitador en cada intersección, ROM

usa un diodo para conectar las líneas si el valor es igual a 1. Por el contrario, si el valor es 0,

las líneas no se conectan en absoluto.

PROM: Crear chips desde la nada lleva mucho tiempo. Por ello, los desarrolladores crearon

un tipo de ROM conocido como PROM (programmable read-only memory). Los chips PROM

vacíos pueden ser comprados económicamente y codificados con una simple herramienta

llamada programador.

La peculiaridad es que solo pueden ser programados una vez. Son más frágiles que los chips

ROM hasta el extremo que la electricidad estática lo puede quemar. Afortunadamente, los

dispositivos PROM vírgenes son baratos e ideales para hacer pruebas para crear un chip

ROM definitivo.

EPROM: Trabajando con chips ROM y PROM puede ser una labor tediosa. Aunque el precio

no sea demasiado elevado, al cabo del tiempo puede suponer un aumento del precio con

todos los inconvenientes. Los EPROM (Erasable programmable read-only memory)

solucionan este problema. Los chips EPROM pueden ser regrabados varias veces.

Borrar una EEPROM requiere una herramienta especial que emite una frecuencia

determinada de luz ultravioleta. Son configuradas usando un programador EPROM que

provee voltaje a un nivel determinado dependiendo del chip usado.

Para sobrescribir una EPROM, tienes que borrarla primero. El problema es que no es

selectivo, lo que quiere decir que borrará toda la EPROM. Para hacer esto, hay que retirar el

chip del dispositivo en el que se encuentra alojado y puesto debajo de la luz ultravioleta

comentada anteriormente.

EEPROM y Memoria Flash: Aunque las EPROM son un gran paso sobre las PROM en

términos de utilidad, siguen necesitando un equipamiento dedicado y un proceso intensivo

para ser retirados y reinstalados cuando un cambio es necesario. Como se ha dicho, no se

pueden añadir cambios a la EPROM; todo el chip sebe ser borrado. Aquí es donde entra en

juego la EEPROM (Electrically erasable programmable read-only memory). La memoria

EEPROM es programable y borrable eléctricamente y su nombre proviene de la sigla en

inglés Electrical Erasable Programmable Read Only Memory. Actualmente estas memorias

se construyen con transistores de tecnología MOS (Metal Oxide Silice) y MNOS (Metal

Nitride-Oxide Silicon).

Las memorias EEPROM son memorias no volátiles y eléctricamente borrables a nivel de

bytes. La posibilidad de programar y borrar las memorias a nivel de bytes supone una gran

flexibilidad, pero también una celda de memoria más compleja.

5.4.3 Contadores (ascendentes, descendente).

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

19

Definición

• Un contador es un circuito digital capaz de contar sucesos electrónicos, tales como impulsos,

avanzando a través de una secuencia de estados binarios.

• Contador síncrono es un tipo de contador en el que todas las etapas utilizan el mismo impulso

de reloj.

Hay contadores ascendentes y descendentes con salidas en binario de n bits

Un contador ascendente/descendente (up/down) es aquel capaz de procesar en cualquier dirección

a lo largo de una cierta secuencia. Un contador ascendente/descendente, algunas veces también

denominado contador bidireccional, puede tener cualquier secuencia de estados especificada. Un

contador binario de 3 bits que avanza en modo ascendente a través de la secuencia (0,1,2,3,4,5,6,7)

y que luego pueda invertirse para recorrer la secuencia en sentido contrario (7,6,5,4,3,2,1,0) es un

ejemplo de un modo de operación secuencial ascendente/descendente.

La figura muestra un contador síncrono ascendente/descendente básico de 3 bits. El FF0 bascula

con cada impulso de reloj. Luego las entradas J0 y K0 de FF0 son: J0=K0=1

Esquema lógico de un contador UP/DOWN síncrono de 3 bits.

Para la secuencia ascendente, Q1 cambia de estado en el siguiente impulso de reloj cuando Q0=1.

Para la secuencia descendente, Q1 cambia en el siguiente impulso de reloj cuando Q0=0. Por lo tanto,

las entradas J1 y K1 del FF1 tienen que ser igual a 1, para las condiciones expresadas en la siguiente

ecuación:

Para la secuencia ascendente, Q2 cambia de estado en el siguiente impulso de reloj cuando Q0=Q1=1.

Para la secuencia descendente, Q2 cambia en el siguiente impulso de reloj cuando Q0=Q1=0. Por lo

tanto, las entradas J2 y K2 de FF2 tienen que ser igual a 1, para las condiciones expresadas en la

siguiente ecuación:

Cada una de las condiciones para las entradas J y K de cada flip-flop produce una basculación en el

punto apropiado de la secuencia del contador.

5.4.4 Sumadores. Para aprender a sumar, con cinco o seis años de edad, tuviste que memorizar las

100 combinaciones posibles que pueden darse al sumar dos dígitos decimales. La tabla de sumar, en

binario, es mucho más sencilla que en decimal. Sólo hay que recordar cuatro combinaciones

posibles:

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

20

+

0

1

0

0

1

1

1

0+1

Las sumas 0+0, 0+1 y 1+0 son evidentes:

0+0 = 0

0+1 = 1

1+0 = 1

Pero la suma de 1+1, que sabemos que es 2 en el sistema decimal, debe escribirse en binario con

dos cifras (10) y, por tanto 1+1 es 0 y se arrastra una unidad, que se suma a la posición siguiente a

la izquierda.

Veamos algunos ejemplos:

Suma Binaria

010 + 101 = 111

001101 + 100101 = 110010

1011011 + 1011010 = 10110101

110111011 + 100111011 = 1011110110

Suma decimal

210 + 510 = 710

1310 + 3710 = 5010

9110 + 9010 = 18110

44310 + 31510 = 75810

Ejercicio 1:

Realiza las siguientes sumas de números binarios:

111011 + 110

____________________

111110111 + 111001

____________________

10111 + 11011 + 10111

____________________

Suma con puertas lógicas

Si planteamos la suma a nivel de tabla de verdad para un sumador de dos bits tendríamos la

siguiente tabla donde se muestra el resultado de la suma y del acarreo

Entrada A Entrada B Acarreo Suma

0

0

0

0

0

1

0

1

1

0

0

1

1

1

1

0

Por lo que las funciones de Suma y Acarreo se pueden

implementar usando puertas lógicas básicas

Dos Implementaciones de semisumador

SUMADOR COMPLETO

Hasta aquí se ha logrado implementar una suma de dos números de un bit, pero en una

computadora las sumas de hacen con un número mayor de bits.

Si cada par de sumandos binarios puede producir un bit de acarreo, también debe tener la

capacidad de reconocer cuando viene un bit de acarreo del sumador de nivel inferior (digamos

cuando en el sistema decimal hay un "llevo" debido a la suma de las unidades y hay que pasarla a las

decenas)

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

21

Para lograr este propósito se implementa el siguiente circuito con su

tabla de verdad:

El circuito anterior es un poco complicado de graficar así que se puede reemplazar por una caja

negra con tres entradas y dos salidas (ver la tabla de verdad)

ENTRADAS SALIDAS

A B Cin Cout S

0 0

0

0

0

0 0

1

0

1

0 1

0

0

1

0 1

1

1

0

1 0

0

0

1

1 0

1

1

0

1 1

0

1

0

1 1

1

1

1

Con lo anteriormente mencionado se

puede implementar un sumador de "n"

bits. Conectando sumadores completos

de 2 bits en cascada.

Nota: Cin=acarreo entrante,

Cout= acarreo saliente

5.4.5 Codificadores/decodificadores.

En un sentido general, se puede decir que un codificador es un circuito hecho para pasar

información de un sistema a otro con clave diferente, y en tal caso un decodificador sería el circuito

o dispositivo que retorne los datos o información al primer sistema. Debido a que el caso que nos

ocupa es el de la lógica digital, y en especial la aritmética binaria, hemos de dar sentido más directo

a los términos "codificador" y "decodificador".

Un codificador es un bloque combinacional hecho para convertir una entrada no binaria en una

salida de estricto orden binario. En otras palabras, es un circuito integrado por un conjunto de

componentes electrónicos con la habilidad para mostrar en sus terminales de salida un word

binario (01101, 1100, etc.), equivalente al número presente en sus entradas, pero escrito en un

código diferente. Por ejemplo, un Octal-to-binary encoder es un circuito codificador con ocho

entradas (un terminal para cada dígito Octal, o de base 8) y tres salidas (un terminal para cada bit

binario).

Los codificadores pueden, también, proporcionar otras operaciones de conversión, tal como ocurre

en las calculadoras de bolsillo con el teclado: El Keyboard (teclas, llaves) encoder convierte la

posición de cada tecla (No. 9, No. 3, No. 5, + , %, etc.) en su correspondiente word asignado

previamente. Un ejemplo de lo anterior es el teclado codificador en ASCII (American Standard Code

for Information Interchange), que genera el word de 7 bits 0100101 cuando es presionada la tecla

del porcentaje (%).

El decodificador es un circuito combinacional diseñado para convertir un número binario (entrada)

en word de "unos" y "ceros" (niveles altos y bajos de voltaje) con un orden distinto, para ejecutar un

trabajo especial. En otras palabras, el word que sale es diferente al word que entró, aunque tenga la

misma cantidad de bits. En Electrónica Digital es a menudo necesario pasar un número binario a

otro formato, tal como el requerido para energizar los siete segmentos de los display hechos con

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

22

diodos emisores de luz, en el orden adecuado para que se ilumine la figura de un individual número

decimal.

Los decodificadores son también usados en los microprocesadores para convertir instrucciones

binarias en señales de tiempo, para controlar máquinas en procesos industriales o implementar

circuitos lógicos avanzados. El decodificador convierte números binarios en sus equivalentes

Octales (base 8), decimales (base 10) y Hexadecimales.

Los codificadores nos permiten “compactar” la información, generando un código de salida a partir

de la información de entrada. Y como siempre, lo mejor es verlo con un ejemplo.

Imaginemos que estamos diseñando un circuito digital que se encuentra en el interior de una

Equipo de música. Este circuito controlará el equipo, haciendo que funcione correctamente.

Una de las cosas que hará este circuito de control será activar la radio, el CD, la cinta o el Disco según

el botón que haya pulsado el usuario. Imaginemos que tenemos 4 botones en la cadena, de manera

que cuando no están pulsados, generan un ’0’ y cuando se pulsan un ’1’ (Botones digitales). Los

podríamos conectar directamente a nuestro circuito de control del equipo de música, como se

muestra en la figura

Circuito de control de un equipo de música, y 4 botones de selección de lo que se quiere escuchar

Sin embargo, a la hora de diseñar el circuito de control, nos resultaría más sencillo que cada botón

tuviese asociado un número. Como en total hay 4 botones, necesitaríamos 2 bits para identificarlos.

Para conseguir esta asociación utilizamos un codificador, que a partir del botón que se haya pulsado

nos devolverá su número asociado:

Fijémonos en las entradas del codificador, que están conectadas a los botones. En cada momento,

sólo habrá un botón apretado, puesto que sólo podemos escuchar una de las cuatro fuentes.

Bien estaremos escuchando el CD, bien la cinta, bien la radio o bien un disco, pero no puede haber

más de un botón pulsado1. Tal y como hemos hecho las conexiones al codificador, el CD tiene

asociado el número 0, la cinta el 1, la radio el 2 y el disco el 3 (Este número depende de la entrada

del codificador a la que lo hayamos conectado).

A la salida del codificador obtendremos el número del botón apretado. La tabla de verdad será así:

E3 E2 E1 E0 C1 C0 Botón

0

0

0

1

0

0

CD

0

0

1

0

0

1

TAPE

0

1

0

0

1

0 RADIO

1

0

0

0

1

1 DISCO

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

23

El circuito de control del equipo ahora sólo tendrá 2 bits de entrada para determinar el botón que se

ha pulsado. Antes necesitábamos 4 entradas. El codificador que hemos usado tiene 4 entradas y 2

salidas, por lo que se llama codificador de 4 a 2. Existen codificadores de mayor número de

entradas, como el que vamos a ver en el siguiente ejemplo.

A continuación deduciremos las ecuaciones de un codificador de 4 a 2.

Las ecuaciones las obtenemos siguiendo el mismo método de siempre: primero obtendremos la

tabla de verdad completa y aplicaremos el método de Karnaugh. Con ello obtendremos las

ecuaciones más simplificadas para las salidas C1 y C0.

Al hacer la tabla de verdad, hay que tener en cuenta que muchas de las entradas NO SE PUEDEN

PRODUCIR. En las entradas de un decodificador, una y sólo una de las entradas estará activa en cada

momento. Utilizaremos esto para simplificar las ecuaciones. Se ha utilizado una X para indicar que

esa salida nunca se producirá:

E3 E2 E1 E0 C1 C0

0

0

0

0

X

X

0

0

0

1

0

0

0

0

1

0

0

1

0

0

1

1

X

X

0

1

0

0

1

0

0

1

0

1

X

X

0

1

1

0

X

X

0

1

1

1

X

X

1

0

0

0

1

1

1

0

0

1

X

X

1

0

1

0

X

X

1

0

1

1

X

X

1

1

0

0

X

X

1

1

0

1

X

X

1

1

1

0

X

X

1

1

1

1

X

X

C1 y C0 siempre valen ’X’ excepto para 4 filas.

Los mapas de Karnaugh que obtenemos son:

Las casillas que tienen el valor ’X’ podemos asignarles el valor que

más nos convenga, de forma que obtengamos la expresión más

simplificada. Las ecuaciones de un decodificador de 4 a 2 son:

La manera “rápida” de obtenerlas es mirando la tabla simplificada, como la que se muestra en el

ejemplo del equipo de música. Sólo hay que fijarse en los ’1’ de las funciones de salida (como si

estuviésemos desarrollando por la primera forma canónica) y escribir la variable de entrada que

vale ’1’.

Habrá tantos sumandos como ’1’ en la función de salida.

Decodificadores

Un decodificador es un circuito integrado por el que se introduce un número y se activa una y sólo

una de las salidas, permaneciendo el resto desactivadas. Y como siempre, lo mejor es verlo con un

ejemplo sencillo. Imaginemos que queremos realizar un circuito de control para un semáforo. El

semáforo puede estar verde, amarillo, rojo o averiado.

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

24

En el caso de estar averiado, se activará una luz interna

“azul”, para que el técnico sepa que lo tiene que reparar.

A cada una de estas luces les vamos a asociar un número.

Así el rojo será el 0, el amarillo el 1, el verde el 2 y el azul

(averiado) el 3.

Para controlar este semáforo podemos hacer un circuito

que tenga 4 salidas, una para una de las luces. Cuando

una de estas salidas esté a ’1’, la luz correspondiente

estará encendida. Sin embargo, ocurre que NO PUEDE HABER DOS O MAS LUCES ENCENDIDAS A LA

VEZ.

Por ejemplo, no puede estar la luz roja y la verde encendidas a la vez!!!!.

Si utilizamos un decodificador de 2

a 4, conseguiremos controlar el

semáforo asegurándonos que sólo

estará activa una luz en cada

momento. Además, el circuito de

control que diseñemos sólo tiene

que tener 2 salidas. El nuevo

esquema se muestra en la figura 6.3.

El funcionamiento es muy sencillo.

Si el circuito de control envía el número 2 (E1 = 1, E0 = 0), _se encenderá la luz verde (que tiene

asociado el número 2) y sólo la luz verde!!!. Un decodificador activa sólo una de las salidas, la salida

que tiene un número igual al que se ha introducido por la entrada. En el ejemplo del semáforo, si el

circuito de control envía el número 3, se activa la salida O3 y se encenderá la luz azul (y sólo esa!!

E1

0

0

1

1

E0

0

1

0

1

03

0

0

0

1

02

0

0

1

0

01

0

1

0

0

00

1

0

0

0

,,

Y las ecuaciones las podemos obtener desarrollando por la

primera forma canónica.

Puesto que por cada función de salida sólo hay un ’1’, no se podrá

simplificar (No hace falta que hagamos Karnaugh)

,

,

5.4.6 Multiplexores/Demultiplexores

Un Multiplexor o “Selector de datos” es un circuito lógico que acepta varias entradas de datos y

permite que sólo una de ellas pase a un tiempo a la salida. El enrutamiento de la entrada de datos

hacia la salida está controlado por las entradas de selección (a las que se hace referencia a veces

como las entradas de dirección).

El multiplexor, también conocido como MUX, actúa como un conmutador multiposicional controlado

digitalmente, donde el código digital aplicado a las entradas de selección controla cuáles entradas de

datos serán conmutadas hacia la salida. Por ejemplo, la salida será igual a la entrada de datos,

llamémosle D0 para el código de entrada de selección que sea cero (ABC=000 en el diagrama de

abajo); la salida será igual D1 para cuando el código de selección sea uno y así sucesivamente.

Establecido de otra manera, un multiplexor selecciona 1 de N fuentes de datos y transmite los datos

seleccionados a un solo canal de salida. Esto se llama multiplexión o multiplexaje.

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

25

Los multiplexores son representados en diagramas de bloques como trapezoides isósceles. A

continuación muestro el esquemático de un multiplexor de dos entradas y una salida con su

respectivo bit de selección:

Ó

Un ejemplo de multiplexores (aunque no digitales como los que vemos aquí) se ve en las líneas

telefónicas. Éstas usan exactamente este principio. Transmiten varias llamadas telefónicas (señales

de audio) a través de un único par cableado usando la técnica de “multiplexado” y cada señal de

audio va únicamente al receptor al que está destinado.

Una aplicación común para los MUX es encontrado en las computadoras, en las cuales la memoria

dinámica usa las mismas líneas de dirección para el direccionamiento tanto de las filas como de las

columnas. Un grupo de multiplexores es usado para primero seleccionar las direcciones de la

columna y luego cambiar para seleccionar la de la fila. Este esquema permite que grandes

cantidades de memoria sean incorporadas dentro de una computadora mientras se limita a la vez la

cantidad de conexiones de cobre requeridas para conectar la memoria al resto del circuito. Por eso

es que también se les conoce a veces como “selectores de datos”.

Ya se vio el símbolo esquemático del multiplexor de 2 entradas y una salida pero los multiplexores

no están limitados a 2 entradas. Si las líneas de selección son dos podemos alternar entre 4 datos de

entrada, si son 3 entre 8 y así sucesivamente. A continuación se muestran los símbolos

esquemáticos de los multiplexores de “4 a 1” (cuatro entradas y una salida), “8 a 1” (ocho entradas y

una salida) y “16 a 1” (dieciséis entradas y una salida) con sus respectivas líneas de selección,

respectivamente.

En todos los casos la salida es Z, las entradas de selección S y el resto es la entrada que será

multiplexada.

El Multiplexor es típicamente usado para combinar dos o más señales digitales en una sola línea

pero no es la única forma. También puede conseguirse de otras características pero aquí

mencionaré sólo un par de ejemplos de multiplexores:

1. De dos entradas de 4 bits y una salida de 4 bits. Éste selecciona uno de los nibbles de entrada

(internamente son 4 multiplexores de 2 a 1 en un solo encapsulado) y lo refleja en la salida.

2. De dos entradas de 4 bits a una salida de dos bits que representan un bit direccionado en

cada nibble reflejado a la salida (internamente son 2 multiplexores de 4 a 1).

Algunas designaciones para multiplexores de la familia TTL son: 74153 que son dos MUX 4 a 2,

74157 que son cuatro MUX 2 a 1 y el 74151 que es un MUX 8 a 1.

Los circuitos multiplexores pueden incluir también una línea de habilitación indicado con una E por

Enable.

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

26

Como último comentario de lo multiplexores quiero agregar que estos pueden ser organizados en

cascada (tal como los sumadores que vimos en el tema anterior) para implementar multiplexores

más grandes. Por ejemplo podemos usar multiplexores de 2 a 1 para implementar un multiplexor de

4 a 1 (o de 4 a 2 que si lo piensan se darán cuenta de que es elemental) o incluso para implementar

multiplexores de más entradas. Veamos específicamente el ejemplo de implementación de un

multiplexor de 16 a 1 usando sólo multiplexores de 4 a 1. El dato de entrada es X formado por los 16

bits x0, x1,...,x14 y x15. Las líneas de selección vienen dadas por S. OJO con este ejemplo. Analícelo y

entiéndalo.

En los multiplexores vemos también la

entrada de enable E (que además son

de lógica negativa que quiere decir que

los IC's se activaran con un cero). Ese

es el bit de habilitación que les dije

veremos en el próximo tema.

Ejemplos de Circuitos con Multiplexores

Demultiplexores. Es lo inverso a un multiplexor. Los demultiplexores o DEMUX tienen una entrada que

es transferida a una de las m posibles líneas de salida. La línea m vendrá direccionada por los n bits de

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

27

selección donde lo normal es que 2n=m. Se podría decir que, cada salida del demultiplexor corresponde

con el término mínimo del número binario que se encuentra en las líneas de selección.

Un uso popular del DEMUX es como decodificador y por eso suele usarse el término

Demultiplexor/Decodificador indistintamente. El propósito principal de un decodificador no es

tanto transferir una entrada a una de las salidas sino llevar un valor binario (el de la entrada de

selección) a una representación de una única línea a la salida. Esta función es de gran utilidad en la

decodificación de la dirección en los microprocesadores por ejemplo cuando involucra la selección

de uno de múltiples dispositivos (como por ejemplo la memoria). De hecho, la mayoría de los

decodificadores son de lógica invertida (o negativa) debido a que la mayoría de los dispositivos

periféricos de los microprocesadores son activados por una señal baja (como el pin E' que vimos en

los multiplexores en cascada hace un par de párrafos).

Los DEMUX también suelen incluir un bit de entrada de habilitación. Algunos DEMUX de la familia

TTL son: el 74139 que son dos DEMUX de 1 a 4 con salidas invertidas (lógica negada), el 74156 que

son dos DEMUX de 1 a 4 con salida de colector abierto (Open Collector), el 74138 que es un DEMUX

de 1 a 8 con salida invertida, el 74156 que es un DEMUX de 1 a 16 y el 74159 que es de 1 a 16 con

salida a colector abierto.

Entrada

s

A B C

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Salidas

S0

1

0

0

0

0

0

0

0

S1

0

1

0

0

0

0

0

0

S2

0

0

1

0

0

0

0

0

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

S3

0

0

0

1

0

0

0

0

S4

0

0

0

0

1

0

0

0

S5

0

0

0

0

0

1

0

0

S6

0

0

0

0

0

0

1

0

S7

0

0

0

0

0

0

0

1

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

28

5.4.7 PAL. GAL. PLD; FPGA, FPGAA. La lógica programable, como el nombre implica, es una familia

de componentes que contienen conjuntos de elementos lógicos (AND, OR, NOT, LATCH, FLIP-FLOP)

que pueden configurarse en cualquier función lógica que el usuario desee y que el componente

soporte. Hay varias clases de dispositivos lógicos programables: ASICs, FPGAs, PLAs, PROMs, PALs,

GALs, y PLDs complejos.

ASIC: Significa Circuitos Integrados de Aplicación Específica y son dispositivos definibles por el

usuario. Los ASICs, al contrario que otros dispositivos, pueden contener funciones analógicas,

digitales, y combinaciones de ambas. En general, son programables mediante máscara y no

programables por el usuario. Esto significa que los fabricantes configurarán el dispositivo según las

especificaciones del usuario. Se usan para combinar una gran cantidad de funciones lógicas en un

dispositivo. Sin embargo, estos dispositivos tienen un costo inicial alto, por lo tanto se usan

principalmente cuando es necesario una gran cantidad.

PLD

Familia de los PLD

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Estructura básica de un PLD

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

29

Un dispositivo programable por el usuario es aquel que contiene una arquitectura general predefinida en la que el usuario puede programar el diseño final del dispositivo empleando un conjunto

de herramientas de desarrollo. Las arquitecturas generales pueden variar pero normalmente

consisten en una o más matrices de puertas AND y OR para implementar funciones lógicas. Muchos

dispositivos también contienen combinaciones de flip-flops y latches que pueden usarse como

elementos de almacenaje para entrada y salida de un dispositivo. Los dispositivos más complejos

contienen macrocélulas. Las macrocélulas permiten al usuario configurar el tipo de entradas y

salidas necesarias en el diseño.

CRONOLOGIA DE LOS PLD´S

1948

Se inventa el transistor de contacto puntual en los Laboratorios Bell Telephone en

Estados Unidos, resultado de una investigación sobre semiconductores llevada a cabo

por Walter Brattain, John Bardeen y William Shockley, quienes recibirían el premio

Nobel por su enorme contribución en 1956.

1951

Se logra un transistor con una estructura como la que se conoce actualmente.

1957

John Wallmark de RCA patenta el FET ( Field Effect Transistor ).

1959

Se concibe el primer Circuito Integrado Digital en la compañía Texas Instruments y es

Jack Kilby quién desarrolla un Flip-Flop sobre una base de substrato de Germanio y

contenía solo cuatro transistores.

1961

Se presenta la primera familia de Circuitos Integrados Digitales comerciales,

denominada R.T.L. ( Resistor - Transistor - Logic ) y que fue introducida por Fairchild

Semiconductor bajo la serie 900, está familia operaba a 3.2 Voltios, poco tiempo

después nace otra familia denominada D.T.L. ( Diode - Transistor - Logic ).

1962

Aparece la familia T.T.L. ( Transistor - Transistor - Logic ), con características como el

de ser más rápida que sus predecesoras, los primeros trabajos hechos en TTL los

realizó James Buie de Pacific Semiconductor ( hoy subsidiaria de TRW ). En ese

mismo año Steven Hofstein y Frederick Heiman de RCA, desarrollan el MOSFET y a

finales del mismo, fabrican el primer Circuito Integrado MOS ( Metal - Oxide - Silicon

) que contenía 16 transistores sobre una pastilla de silicio de 0.063 mm por lado.

1963

La compañía RCA producía un Circuito Integrado con cientos de MOSFET´S en un

área muy reducida, al mismo tiempo nacían familias como la MOS de canal N y de

canal P, NMOS y PMOS respectivamente y así como la CMOS ( Complementary MOS ).

La CMOS se impuso con el tiempo bajo la serie 40XX lanzada por RCA. Y poco tiempo

después la 74CXX de National Semiconductor.

A mediados Surge el primer PLD, una matriz de diodos configurables y fusibles desarrollado por

de los 60´s

Harris Semiconductor ( conocida en ese tiempo como Radiation, Inc. ).

1967

Fairchild lanza al mercado una ROM de 64 bits con tecnología MOS.

1969

Nace el primer PLA, desarrollado por IBM y descrito como ROAM ( Read -Only

Associative - Memory ).

1970

La compañía Harris crea la PROM, que combinaba la tecnología de fusibles de

nicromo con una simplificación en la estructura de la ROM. En este mismo año Texas

Instruments fabrica el TMS 200 y era un Circuito Integrado de máscara programable

basado en el ROAM de IBM, este manejaba diecisiete entradas y ocho salidas,

contenía ocho Flip-Flops JK como elementos de memoria.

1971

Collins Radio ofrece otro PLA de máscara programable denominado CRC 3506/7,

similar al TMS 200. Intel hace una innovación tecnológica al introducir la EPROM

borrable con rayos UV. General Electric abre una puerta más con una nueva

tecnología PROM, desarrollada por David Greer, donde la estructura consistía de un

Plano-Or y señales que van hacia un Plano-And; permitiendo el uso de lógica de

multinivel sin desperdicio de pines I/O.

1971

Al mismo tiempo General Electric hace experimentos con PLD´s de tecnología MOS,

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

30

1972

1973

1974

1975

1978

1980

1981

1982

1983

1983

1984

usando las características de los PLA y con la tecnología de borrado con rayos UV. En

junio Intel ofrece al mercado el primer microprocesador MOS ( el 4004, de 4 bits )

que contenía 2300 transistores.

MOSTEK Corporation lanza la primera Memoria de Alta Densidad (una RAM

dinámica de 1024 bits) e Intel ofrece los primeros microprocesadores de 8 bits (el

8008 y el 8080).

National Semiconductor crea su propio PLA de máscara programable similar al TMS

200 pero con catorce entradas y ocho salidas sin elementos de memoria. El mérito a

este dispositivo consistió en su menor complejidad en el diseño, mostrando así un

avance en la nueva tecnología. Este dispositivo fue conocido como DM7575/DM8575.

Monolithic Memories fabrica un dispositivo denominado PALA ( Programable

Associative Logic Array ) bajo el número de parte MMT 5760/6760 implementaba

multiniveles y circuitos secuenciales de más de 100 compuertas e incorporó bajo

acuerdo de General Electric innovaciones en el dispositivo de máscara programable.

Intersil anuncia el IM5200 un FPLA; poco después, Signetics hace lo mismo con el

82S100 que logró encabezar la carrera de los PLD´s durante un tiempo.

En el verano de este año nace el dispositivo PAL, como un proyecto de MMI

encabezado por John Birkner, en el que se pretendían satisfacer varias necesidades

del mercado, entre ellas las de reemplazar la lógica estándar, mejorar los tamaños y

la velocidad de los ya existentes; bajo esta idea los PAL invaden el mercado. El PAL

que conocemos actualmente se basa en un diseño de H.T. Chua. MMI ofrece soporte

para el manejo de los nuevos dispositivos en el “ PAL Handbook “ escrito por John

Birkner y que en el mismo se acompañaba de un programa hecho en Fortran para

ayudar a programar los dispositivos.

Se propone y presenta el primer formato JEDEC para los PLD´s.

Signetics registra FPLA´s con aplicaciones para máquinas de estados.

En el verano de este año Bill Wiley Smith de Signetics crea una muestra de lo que

sería el soporte para la programación de PLD´s, llamado BEE ( Boolean Equation

Entry ); cuyas características eran las Ecuaciones Booleanas, notación de estados,

tablas de verdad, minimización lógica en forma automática así como la simulación de

los diseños. En diciembre de este año se anuncia el proyecto ABEL ( Advanced

Boolean Expression Language ) para un número limitado de PLD’s de diferentes

manufacturas y que fue un Software muy bien recibido por el mercado. Se crea otra

herramienta denominada CUPL (Common Universal tool for Programable Logic)

desarrollado por Bob Osann de Assited Technology.

En Marzo se crea una segunda versión de CUPL soportando a todos los PAL´s

soportados por PALASM y un número limitado de FPLAS combinacionales de

Signetics con características similares al BEE. Poco después surge la segunda versión

de ABEL que soportaba virtualmente a todos los PLD´s de esa época y esto toma por

sorpresa a los diseñadores de otras herramientas de Software. En seguida National

Semiconductor lanza el Software llamado PLAN ( Programable Logic Analysis by

National ). Cypress Semiconductor crea un PAL que se hace popular por su alta

velocidad. Lattice Semiconductor compañía especializada en tecnología borrable

CMOS crea un PAL borrable eléctricamente al que llamaron Generic Array Logic o

GAL, pero esta compañía tuvo problemas legales con MMI hoy parte de AMD quién

obtuvo el derecho de producir el GAL pero bajo otro nombre, en seguida Lattice crea

el GAL 39V18 conocido hoy como Lattice 6001.

International CMOS Technology (I.C.T.) desarrolla un dispositivo llamado PEEL

(Programable Electrically Erasable Logic) con tecnología de Lattice y fue llevado a

primera producción en 1986.

Se anuncia un nuevo concepto en cuanto a la tecnología de los PLD´s y es encabezado

Facultad de Ingeniería Mecánica

Edificio W Ciudad Universitaria

Morelia, Michoacán

Ignacio Franco Torres 2012-2013

ifranco@correo.fie.umich.mx

www.fim.umich.mx

Email: fim@umich.mx

Tel: 4433223500 ext 3107, 3109, 3111

31

1988

1989

1995

por Xilinix Corporation, el dispositivo desarrollado es el LCA (Logic Cell Array)

compuesto de pequeñas celdas lógicas, similares a la arquitectura de una PROM,

donde cada celda es capaz de crear cuatro o cinco funciones de entrada y dos de

salida. Poco después Exel Microelectronic´s crece el XL78C800 Erasic, este

dispositivo creado bajo arreglo de multiniveles de lógica y tardo aún más el diseño

del Software y programación en estar disponible.

Actel Corporation introduce un FPGA diferente al de los dispositivos de Xilinix. El Act

1 de densidad comparable al arreglo de compuertas de máscara programable al igual

que el LCA requiere de el trazado de rutas de funciones lógicas para ser usado

efectivamente.

Plessey Semiconductor introduce un FPGA con características similares, pero con una

mejor arquitectura.

Lattice Semiconductor Corporation, anuncia el 7 de Agosto, la introducción de

WorldÆ fastest 3.3 Volt 22V10, cuya máxima velocidad de operación es de 7.5 ns

(133.33 Mhz).

Que permite la utilización del dispositivo con baterías.

Lattice Semiconductor Corporation, anuncia una actualización para los

Programadores Universales en septiembre de ese año. La actualización responde a

que sus nuevos productos, el GAL16LV8D-3LJ y el GAL16V8D-5LJ son lanzados al

mercado. Las nuevas cualidades de estos dispositivos son : velocidades desde 3.5 ns

(286 Mhz ); además de operar a un voltaje de alimentación de 3.3 Volts.

PROM: Son memorias programables de sólo lectura. Aunque el nombre no implica la lógica

programable, las PROM, son de hecho lógicas. La arquitectura de la mayoría de las PROM consiste

generalmente en un número fijo de términos AND que alimenta una matriz programable OR. Se usan

principalmente para decodificar las combinaciones de entrada en funciones de salida.

PAL: Son dispositivos de matriz

programable. La arquitectura interna

consiste en términos AND programables

que alimentan términos OR fijos. Todas las

entradas a la matriz pueden ser

combinadas mediante AND entre sí, pero

los términos AND específicos se dedican a

términos OR específicos. Las PAL tienen

una arquitectura muy popular y son

probablemente el tipo de dispositivo