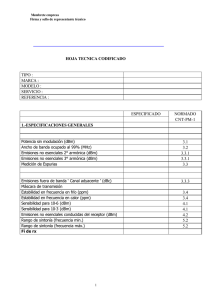

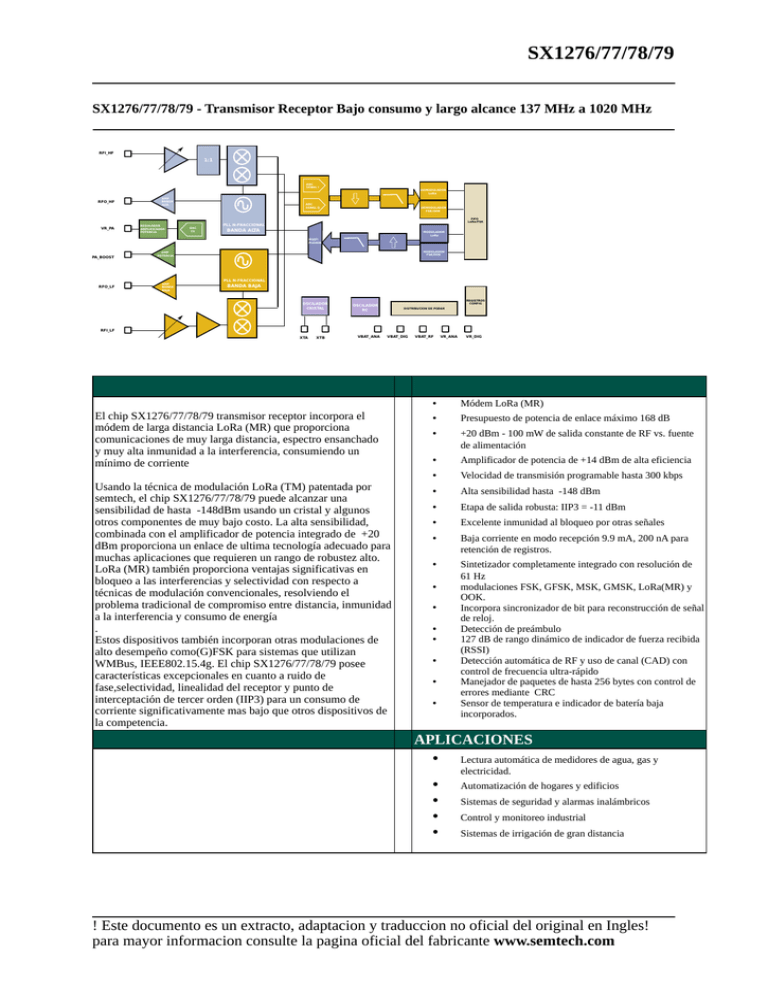

SX1276/77/78/79

Anuncio