Programa y evaluación - Arquitectura y Tecnología de Computadores

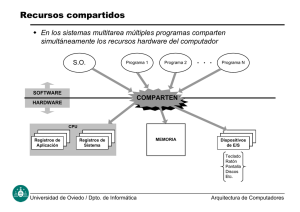

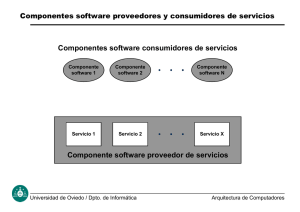

Anuncio

UNIVERSIDAD DE OVIEDO Departamento de Informática Programa de la asignatura: INGENIERÍA DE COMPUTADORES Titulación: INGENIERO TÉCNICO EN INFORMÁTICA DE SISTEMAS Centro: ESCUELA UNIVERSITARIA DE INGENIERÍA TÉCNICA INFORMÁTICA DE GIJÓN CURSO ACADÉMICO: 2008-2009 CRÉDITOS: 6 (3 Teoría + 1,5 Tablero + 1,5 Laboratorio) CRÉDITOS ECTS: 4,8 (2,4 Teoría + 2,4 Práctica) PROFESORES: Juan Carlos Granda Candás (jcgranda@uniovi.es) Manuel García Vázquez (mgarcia@uniovi.es) UNIVERSIDAD DE OVIEDO Departamento de Informática PRERREQUISITOS Conceptos básicos de arquitectura de computadores. Conceptos básicos de sistemas operativos. Programación en lenguaje C. OBJETIVOS El objetivo fundamental de la asignatura es introducir al alumno el computador real, en contraposición al computador Von Neumann estudiado en la asignatura de Estructura de computadores de primer curso. Este objetivo fundamental se traduce en los siguientes objetivos específicos: Presentar aquellas características del computador moderno que representan una mejora indispensable del computador von Neumann básico y que son necesarias para dar soporte a los nuevos sistemas operativos multitarea. Incidir en que los sistemas operativos multitarea requieren un soporte hardware específico, y como este soporte es proporcionado por las CPUs protegidas. Indicar qué mecanismos hardware son necesarios para dar soporte a los sistemas operativos multitarea. Explicar los mecanismos de transferencia de control al sistema operativo (llamada a los servicios del sistema, interrupciones y excepciones). Indicar que aparte del soporte a los sistemas operativos multitarea, también se busca el incremento en el rendimiento de las CPUs. Se presentan las técnicas básicas de segmentación y replicación de unidades funcionales. Introducir una arquitectura real como ejemplo de los conceptos vistos, la arquitectura IA-32. Presentar su evolución histórica, sus diferentes modos de funcionamiento, los modos de protección y los mecanismos de transferencia de control. Hacer ver a los alumnos que el deseo de todo programador es disponer de una memoria lo más grande y lo más rápida posible, lo cual se puede conseguir utilizando memorias de diferentes tecnologías organizadas jerárquicamente. Explicar el principio de localidad, en sus dos modalidades, espacial y temporal, y hacer ver a los alumnos que este principio es el que hace que la jerarquía de memoria funcione. Presentar los principios organizativos y de funcionamiento de una memoria cache. Así se presentaran los conceptos de bloque y de fallo, así como la necesidad de resolver los problemas de ubicación, identificación, reemplazo y escritura de los bloques de la cache. Explicar las tres estrategias de correspondencia comúnmente utilizadas, es decir, la correspondencia directa, la asociativa y la asociativa por conjuntos. Utilizando los mismos ejemplos, explicar también las estrategias de reemplazo y escritura. Presentar diferentes tipos de arquitecturas de cache (caches de un nivel frente a multinivel, unificadas frente a divididas), así cómo sus ventajas e inconvenientes. Programa de la asignatura Ingeniería de computadores Curso 2008-2009 1 UNIVERSIDAD DE OVIEDO Departamento de Informática Comentar los parámetros básicos de los sistemas de cache de las arquitecturas IA-32/PC actuales. Comentar las diferentes técnicas utilizadas en el diseño de la memoria principal para minimizar el impacto de los fallos de cache, y así mejorar el rendimiento global del sistema. Explicar los objetivos perseguidos por el mecanismo de traslación de direcciones virtuales a físicas. Indicar las estrategias posibles para la ubicación de direcciones virtuales en el espacio físico de direcciones. Discutir acerca de la organización de las direcciones de los programas y del sistema operativo en un entorno multitarea. Hacer ver al alumno que la asignación de una tabla de páginas a cada proceso, hace que cada proceso tenga un espacio de direcciones privado. Plantear como el sistema operativo se ubica en las direcciones virtuales de todos los procesos. Analizar cómo la paginación proporciona protección, pero al mismo tiempo, permite también compartir direcciones entre procesos. Comentar dónde se almacena la tabla de páginas y qué mecanismos utiliza la CPU para conocer su ubicación. Explicar el concepto y el objetivo de la TLB. Explicar el concepto de fallo de página y qué pasos debe llevar a cabo el sistema operativo para tratarlo. Analizar el sistema de translación de direcciones de la arquitectura IA-32 basado en un sistema de tablas de doble nivel. Indicar cómo este sistema permite reducir drásticamente el tamaño de la tabla de páginas. Presentar el concepto de espacios de direcciones separados para E/S y para memoria. Explicar las técnicas clásicamente utilizadas para llevar a cabo los procesos de E/S, ordenadas de menor a mayor complejidad, e incidir en las mejoras que las más complejas van aportando sobre las más simples. Explicar los aspectos básicos de la organización del sistema de E/S de un computador real. Para ello se utilizará como ejemplo el PC. Entre dichos aspectos están la organización de los dispositivos en los espacios de direcciones y el sistema de gestión de interrupciones. Repasar los sistemas de interconexión existentes, plantear sus ventajas e inconvenientes. Describir la interconexión mediante buses. Introducción del concepto de ciclo de bus. Explicar los dos modelos de sincronización de las operaciones de un bus: el modelo síncrono y el asíncrono. Describir la problemática planteada por el acceso de múltiples dispositivos a un mismo bus. Presentar el concepto de maestro de bus. Programa de la asignatura Ingeniería de computadores Curso 2008-2009 2 UNIVERSIDAD DE OVIEDO Departamento de Informática Describir el problema planteado en un bus con múltiples maestros. Presentar el concepto de arbitraje, así como las diferentes técnicas para arbitrar un bus. Plantear las razones que hacen necesario la organización jerárquica de los buses. Poner algunos ejemplos de jerarquías de buses. Presentar la organización jerárquica de los buses de un PC moderno, haciendo hincapiés en las diferentes velocidades y anchos de banda de los distintos niveles de su jerarquía. Programa de la asignatura Ingeniería de computadores Curso 2008-2009 3 UNIVERSIDAD DE OVIEDO Departamento de Informática PROGRAMA DE TEORÍA 1. Introducción 1.1. Objetivos de la asignatura 1.2. Introducción a los sistemas operativos multitarea 1.2.1. Llamada a los servicios del sistema operativo 1.2.2. Interrupciones 1.2.3. Excepciones 2. La CPU 2.1. Soporte a los sistemas operativos multitarea 2.2. Mejoras del rendimiento 2.2.1. La segmentación en la ejecución de instrucciones 2.2.2. La replicación de unidades funcionales 2.3. La arquitectura IA-32 2.3.1. Introducción histórica a la arquitectura IA-32 2.3.2. Soporte de la arquitectura IA-32 a los sistemas operativos multitarea Modos de operación Registros de ejecución básicos Modelo de memoria Niveles de privilegio Mecanismos de transferencia de control al sistema operativo Llamadas a los servicios del SO Interrupciones Excepciones Secuencia de pasos durante la transferencia de control 3. La jerarquía de memoria 3.1. Introducción 3.2. Concepto de jerarquía de memoria 3.3. La memoria cache 3.3.1. Conceptos preliminares 3.3.2. Estrategias de correspondencia Correspondencia directa Correspondencia (totalmente) asociativa Correspondencia asociativa por conjuntos 3.3.3. Estrategias de reemplazo 3.3.4. Estrategias de escritura El problema de la coherencia 3.3.5. Organización de la memoria cache 3.3.6. Memoria cache en la arquitectura IA-32/PC 3.4. Memoria principal 3.4.1. Coste temporal de un fallo cache 3.4.2. Coste temporal de la actualización de un bloque de memoria principal 3.4.3. Mejoras en la organización de la memoria principal Memoria no entrelazada Memoria entrelazada Ampliación del bus de datos Acceso mediante ráfagas Programa de la asignatura Ingeniería de computadores Curso 2008-2009 4 UNIVERSIDAD DE OVIEDO Departamento de Informática 3.5. La memoria virtual 3.5.1. Introducción 3.5.2. Objetivos Ampliación de la capacidad de memoria Protección de memoria Compartición de memoria Simplificación de las herramientas de desarrollo y carga 3.5.3. Estrategias de memoria virtual: paginación y segmentación 3.5.4. La memoria virtual paginada Concepto de página y marco de página La tabla de páginas Ubicación en memoria de las tareas y el SO Protección de memoria Compartición de memoria El TLB Fallo de página: concepto y tratamiento 3.5.5. Paginación en la arquitectura IA-32 La tabla de páginas en la arquitectura IA-32 4. El sistema de E/S 4.1. Introducción 4.2. Ubicación del sistema de E/S en los espacios de direcciones 4.3. Protección del sistema de E/S 4.4. Técnicas de E/S 4.4.1. E/S programada con muestreo 4.4.2. E/S con interrupciones 4.4.3. DMA 4.4.4. Procesadores de E/S 4.5. Interrupciones en la arquitectura IA-32/PC 4.6. DMA en la arquitectura IA-32/PC 5. Sistemas de interconexión 5.1. Topologías de interconexión 5.2. Los buses 5.2.1. El concepto de ciclo de bus 5.2.2. Características de un bus 5.2.3. Bus con múltiples maestros: concepto de arbitraje 5.2.4. Jerarquía de buses 5.3. El bus PCI 5.4. PCI Express 5.5. Conexión de los componentes de un PC moderno Programa de la asignatura Ingeniería de computadores Curso 2008-2009 5 UNIVERSIDAD DE OVIEDO Departamento de Informática PROGRAMA DE PRÁCTICAS Cada sesión requiere una hora de prácticas. Bloque1: El soporte de la arquitectura a los sistemas operativos multitarea Sesión 1. Mecanismos de transferencia de control en un sistema operativo multitarea. Sesión 2. Soporte de la CPU teórica a los sistemas operativos multitarea. Sesión 3. La protección en sistemas operativos reales. Bloque2: La jerarquía de memoria Sesión 1. Comprobación del principio de localidad e introducción al simulador SMC. Sesión 2. Prueba de estrategias de correspondencia en la memoria cache. Sesión 3. Diseño de una memoria cache. Sesión 4. Servicios de gestión de memoria en Windows. Sesión 5. La tabla de páginas en Windows. Sesión 6. La paginación en Linux. Bloque3: El sistema de E/S Sesión 1. Introducción a la E/S en el PC. Sesión 2. Introducción a la E/S a través del bus USB. BIBLIOGRAFÍA Manuel García y José María López Apuntes de organización de computadores Servicio de publicaciones de la Universidad de Oviedo, 2007 William Stallings Organización y arquitectura de computadores: diseño para optimizar prestaciones Prentice Hall, 1997 David A. Patterson y Jonh L. Henessy Estructura y diseño de computadores: interficie circuitería/programación Reverté, 2004 Tom Shandley Protected mode software architecture Addison-Wesley, 1998 Jonh H. Crawford y Patrick P. Gelsinger Programación del 80386/387 Anaya Multimedia, 1991 Programa de la asignatura Ingeniería de computadores Curso 2008-2009 6 UNIVERSIDAD DE OVIEDO Departamento de Informática CRÉDITOS Y EVALUACIÓN La nota final de la asignatura se obtendrá sumando la nota de los siguientes apartados: Problemas: 2 puntos. A lo largo del cuatrimestre se realizarán ejercicios en clase que se recogerán para su corrección. Estos ejercicios serán llevados a cabo en el aula de forma individual. Prácticas de laboratorio: 2 puntos. Durante el curso se realizarán diferentes sesiones prácticas cuya asistencia no es obligatoria. Además, se enunciarán una serie de prácticas a entregar. Para la nota de prácticas, se valorará tanto la asistencia a las clases prácticas (máximo 0,5 puntos) como la evaluación de las prácticas entregadas (máximo 1,5 puntos). Trabajos en grupo: 1 punto. Los alumnos se organizarán en grupos y llevarán a cabo un trabajo propuesto por el profesor o por ellos mismos. Como resultado del mismo, deberán presentar una memoria del trabajo realizado y llevar a cabo una exposición pública en el aula de teoría. En la evaluación del trabajo se valorará su dificultad y calidad así como la presentación. El contenido de estos trabajos puede ser materia de examen. Examen teórico: 5 puntos. Dentro de dicho examen teórico se evaluarán los contenidos teóricos de la asignatura. La evaluación se llevará a cabo mediante un examen escrito. Para que la asignatura se considere aprobada es necesario obtener una nota mínima en el examen de 4 sobre 10. Independientemente de la nota obtenida en los diferentes apartados de la evaluación, debe cumplirse la condición de obtener un 4 sobre 10 en el examen para aprobar la asignatura. Si dicha condición no se cumple, la nota final de la asignatura resultaría la obtenida en el examen, sin tenerse en cuenta el resto. PÁGINA WEB DE LA ASIGNATURA http://www.atc.uniovi.es/inf_med_gijon/3ingcomp/ Gijón, Septiembre de 2008 Programa de la asignatura Ingeniería de computadores Curso 2008-2009 7