Curso de Microcontrolares Familia HC9S08 Artículo

Anuncio

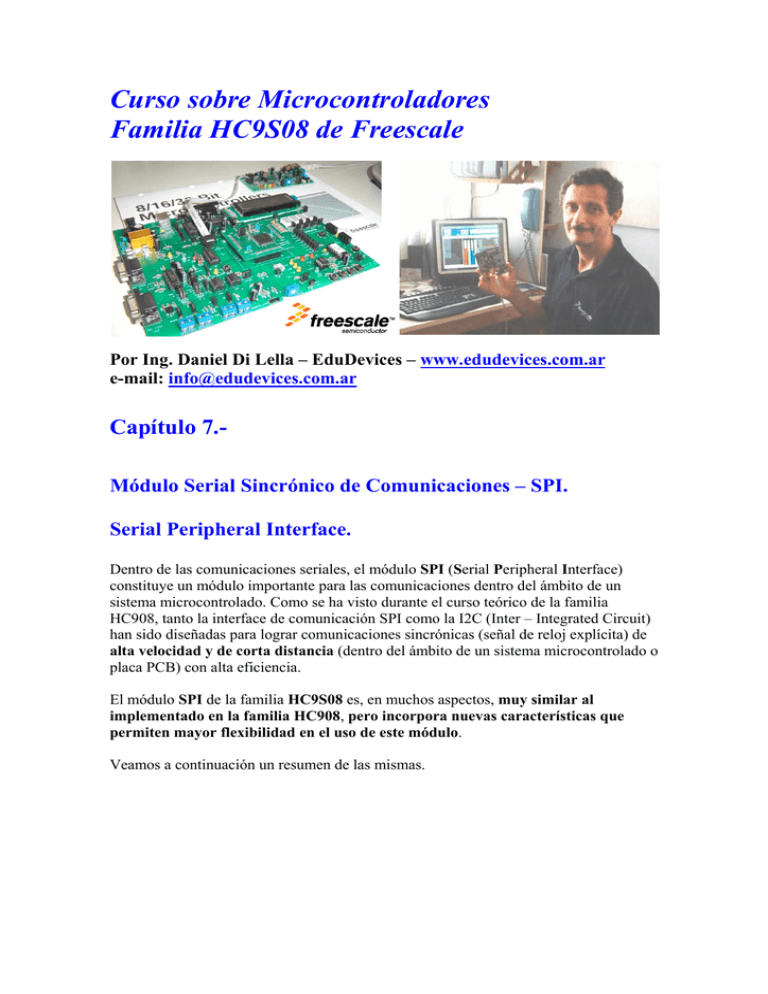

Curso sobre Microcontroladores Familia HC9S08 de Freescale Por Ing. Daniel Di Lella – EduDevices – www.edudevices.com.ar e-mail: info@edudevices.com.ar Capítulo 7.Módulo Serial Sincrónico de Comunicaciones – SPI. Serial Peripheral Interface. Dentro de las comunicaciones seriales, el módulo SPI (Serial Peripheral Interface) constituye un módulo importante para las comunicaciones dentro del ámbito de un sistema microcontrolado. Como se ha visto durante el curso teórico de la familia HC908, tanto la interface de comunicación SPI como la I2C (Inter – Integrated Circuit) han sido diseñadas para lograr comunicaciones sincrónicas (señal de reloj explícita) de alta velocidad y de corta distancia (dentro del ámbito de un sistema microcontrolado o placa PCB) con alta eficiencia. El módulo SPI de la familia HC9S08 es, en muchos aspectos, muy similar al implementado en la familia HC908, pero incorpora nuevas características que permiten mayor flexibilidad en el uso de este módulo. Veamos a continuación un resumen de las mismas. Características: • • • • • • • • Operación Full Duplex a 2 hilos. Modos de operación MASTER y SLAVE. Máxima frecuencia en modo MASTER = FBUS / 2. Máxima frecuencia en modo SLAVE = FBUS / 4. Modo especial Bidireccional de comunicación “Single Wire” (1hilo). Selección de desplazamiento MSB primero o LSB primero. Selección de fase y polaridad del reloj para distintos dispositivos SPI. Interrupciones separadas de TX / RX . Aplicaciones típicas: • Comunicación serial sincrónica con periféricos externos como conversores A/D de alta resolución, memorias externas EEPROM, MCUs de otras placas del sistema. • Procesamiento distribuido entre MCU principal y MCU´s esclavos del sistema. Configuración SPI MASTER – SLAVE. El módulo SPI está construido alrededor de un registro de desplazamiento (Shift Register) doble “buffered” (con doble almacenamiento) con ambos extremos del shif register disponibles como líneas exteriores. Una de las líneas del shift register está conectada al pin MISO (Master In –Slave Out). Este pin oficia como entrada de datos del módulo configurado como MASTER y como salida de datos para el módulo configurado como SLAVE. La otra línea conectada al pin MOSI (Master Out – Slave In) oficia en forma inversa, o sea como salida de datos para el módulo configurado como MASTER y como entrada de datos para el módulo configurado como SLAVE. El CPU comienza una transferencia SPI por medio de la escritura de un byte de datos en el registro de datos del transmisor del módulo SPI MASTER (SPID). La totalidad de los 8 bits de datos serán transferidos en forma automática por el pin MOSI sincronizados por medio de la señal de reloj SPSCK del dispositivo MASTER. De esta forma, por cada bit que es enviado al exterior por el pin MOSI, un bit ingresa al shift register desde el pin MISO. Esto permite realizar comunicaciones FULL DUPLEX con solo 8 pulsos de clock (8 Bits del MASTER y 8 Bits del SLAVE con solo 8 clocks). Como se vio durante el curso teórico de la familia HC908, la línea “SS (negada)” (Slave Select) funciona de forma distinta para el módulo configurado como MASTER (amo) o para el módulo configurado como SLAVE (esclavo). Para el módulo configurado como Amo, la línea SS (negada) debe conectarse a +VDD para indicar por hardware que el dispositivo se usará en configuración AMO antes de configurar por medio de los registros de configuración el módulo como AMO. Aunque esta acción parezca redundante, es fundamental para garantizar el funcionamiento de la red en configuraciones del tipo “Multi – Masters”, en donde más de un dispositivo puede asumir el rol de “Master” en algún momento de la comunicación. El funcionamiento de este tipo de configuración se ha explicado en detalle en el curso teórico de la familia HC908 y dejamos para el lector el repaso de dichos conceptos. Para el módulo configurado como “Esclavo”, la línea SS (negada) funcionará como línea de selección del dispositivo SPI esclavo a comunicar. Cuando la línea SS (negada) de un dispositivo esclavo es forzada a 0V (“0” lógico), este dispositivo es seleccionado para establecer la comunicación con el dispositivo “Amo”. Cuando la línea SS (negada) es forzada a + VDD, el dispositivo “esclavo” está deshabilitado para la comunicación y pone a las líneas MISO / MOSI / SPSCLK en alta impedancia. Cabe recordar que en una comunicación SPI de más de un dispositivo esclavo, las líneas MISO / MOSI / SPSCK estarán conectadas en “paralelo” con cada uno de los dispositivos SPI, formado un “BUS” de comunicaciones de 3 hilos. Las líneas SS (negada) de cada uno de los dispositivos esclavos deben ser controladas por el MCU “Amo” de forma tal de que solo 1 (un) dispositivo esclavo esté habilitado por vez. Los dispositivos esclavos no habilitados estarán en estado de alta impedancia (Tri – State) conectados al bus SPI y no formarán parte de la comunicación. Registros de Control del SPI (SPI Control Registers). Registro de Control 1 – SPIC1. Veamos bit por bit el registro de control 1 del SPI. SPIE: Este bit de lectura / escritura habilita / deshabilita la generación de pedidos de interrupción al CPU por parte del módulo SPI. Existen dos tipos de fuentes de generación de pedidos de interrupción, una de ellas es cuando el buffer de recepción del módulo está lleno y la otra es cuando se generan pedidos ante errores de la comunicación. Cuando el bit SPIE es puesto a “1”, se generará un pedido de interrupción por hardware cuando se cumpla la condición de “buffer lleno de recepción” (flag SPRF = 1) en el registro de estados del módulo (SPIS) o cuando la línea SS (negada) del dispositivo AMO (master) se fuerza a “0” lógico causando el modo “falla” (Mode fault, flag MODF = 1). SPE: El bit SPE (SPI System Enable) permite encender o apagar el módulo SPI. Cuando SPE = 0, se deshabilita el módulo SPI, se detiene cualquier transferencia que esté en curso, se limpia el buffer de datos y se inicializan las máquinas de estado internas. El flag SPRF se limpia y el flag SPTEF (SPI Transmit Data Buffer Empty Flag) en el registro de estados SPIS es forzado a “1” indicando que ambos buffers están vacíos. SPTIE: El bit SPTIE (SPI Transmit Interrpt Enable) de lectura / escritura permite generar el pedido de interrupción al CPU cuando un byte es transferido desde el registro de datos al shift register. MSTR: El bit MSTR (Master / Slave Mode Select) permite seleccionar entre el modo de funcionamiento “Master” o “Slave” del módulo SPI. Si MSTR = 1, el módulo se configurará como “Master”. Si MSTR = 0, el módulo lo hará como “Slave”. CPOL: Este bit (Clock Polarity) permite configurar la “polaridad” de la línea SPSCK durante la transmisión de un dato. En realidad, este bit permite deshabilitar / habilitar un inversor lógico en la línea de reloj lo que le permite adaptarse a las polaridades de los distintos dispositivos. Recordemos que para efectuar una comunicación SPI ambos dispositivos tienen que tener idéntica polaridad. CPHA: El bit CPHA (Clock Phase) permite controlar la relación de tiempos (timing) entre la señal de reloj y la señal de datos, o lo que se denomina “fase del clock”. Recordemos que para efectuar una comunicación SPI ambos dispositivos tienen que tener idéntica fase. SSOE: El bit SSOE (Slave Select Output Enable) se usa en combinación con el bit de habilitación del modo de falla (MODFEN) en el registro de control 2 y con el bit MSTR para determinar la función de la línea SS (negada). LSBFE: El bit LSBFE (Least Significant Bit First Enable) permite seleccionar la dirección de desplazamiento de los datos del shift register del módulo. Si LSBFE = 1, configura al módulom SPI para que la transferencia de datos comience con el bit menos Significativo (LSB). Si LSBFE = 0, se configurará para comenzar con el bit más significativo (MSB). Registro de Control 2 – SPIC2. Veamos bit por bit el registro de control 2 del SPI. MODFEN: El bit MODFEN (Master Mode – Fault Function Enable) junto con el bit SSOE y el bit MSTR determinan como se usará la línea SS (negada) en el módulo SPI. La tabla superior muestra como las distintas combinaciones de los bits mencionados le asignan distintas funciones a la línea SS (negada). Como se puede ver, cuando el módulo SPI es configurado en modo Esclavo (Slave), el bit MODFEN no tiene efecto sobre la línea SS (negada). BIDIROE: El bit BIDIROE (Bidirectional Mode Output Enable) se utiliza cuando el módulo SPI se configura en el modo bidireccional de un solo hilo (Bidirectional Single Wire Mode) y sirve para habilitar la línea I/O SPI a un solo hilo como salida. Cuando BIDIROE = 0, la línea actúa como entrada y cuando BIDIROE = 1, actúa como salida. Dependiendo de si el módulo SPI es configurado como Master o como Slave la línea bidireccional de datos I/O puede ser la MOSI (ahora como MOMI) o la MISO (ahora como SISO) respectivamente. SPISWAI: El bit SPISWAI (SPI Stop in Wait Mode) es un bit de lectura / escritura que se utiliza para mantener al reloj “corriendo” o detenido en el módulo de SPI cuando el MCU entra en un estado WAIT. Si SPISWAI = 1, el clock del SPI se detiene cuando el microcontrolador entra en modo WAIT. Esto permite un considerable ahorro de energía si se tiene pensado no utilizar el módulo SPI durante el estado WAIT del MCU. SPCO: El bit SPCO (SPI Pin Control) permite seleccionar el modo de salida del módulo SPI entre “Single Wire Bidirectional Mode” o “Full Duplex Mode”. Si SPCO = 1, el modo de salida es el de Single Wire. SPI Baud Rate Register (SPIBR). El registro SPIBR (SPI Baud Rate Register) es el utilizado para configurar la velocidad de comunicación SPI solo en el modo Master, ya que como es sabido, el nodo “Master” de una red de comunicaciones SPI es el único responsable de fijar la velocidad de comunicación debido a que este nodo es el que “impone” el reloj (SPSCK) al resto de los nodos que constituyen la red SPI. Con este registro se configuran el valor del “prescaler” y el divisor de Baud Rate para establecer el valor final del reloj SPSCK que regirá la comunicación. En modo “Slave” (esclavo) este registro no tiene efecto alguno sobre la velocidad de comunicación. A continuación describiremos cada uno de los bits que constituyen el registro. SPPR2/SPPR1/SPPR0: Estos tres bits son los utilizados para establecer el valor del divisor del pre –escaler (1 de los 8 valores posibles). La salida del pre-escaler ingresa al divisor de Baud Rate del módulo SPI. SPR2/SPR1/SPR0: Estos tres bits son los utilizados para establecer el valor del divisor de la señal de reloj proveniente del pre-escaler, y por ende, fijar el Baud Rate según la siguiente ecuación: La ecuación muestra como con los bits de los campos SPPR[2:0] y SPR[2:0] se puede determinar la velocidad de comunicación o Baud Rate del módulo SPI Master. A continuación se detallan las tablas con los diferentes valores de configuración del registro y los valores de división del pre – escaler y divisor de Baud Rate. Continuará ....... Nota de Redacción: El lector puede descargar este capítulo y capítulos anteriores del curso desde la sección “Artículos” (Curso_HC9S08) en el sitio web de EduDevices (www.edudevices.com.ar )