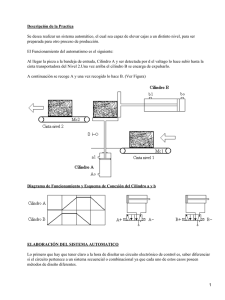

SISTEMAS DE CONTROL SECUENCIAL

Anuncio