slides1 - Universidad de Santiago de Chile

Anuncio

Taller de Programación Paralela

Fernando R. Rannou

Departamento de Ingenierı́a Informática

Universidad de Santiago de Chile

March 17, 2008

¿Qué es paralelismo?

■

Una estrategia compuesta de elementos de hardware y software para resolver complejos

problemas computacionales, en forma más rápida.

■

En términos simples, paralelismo se logra realizando las siguientes etapas

1. Dividir el problema en tareas más pequeñas

2. Asignar las tareas a un conjunto de procesadores que trabajen simultáneamente

3. Coordinar a los procesadores

■

Una solución secuencial sólo se preocupa de encontrar un algoritmo que resuelva el problema.

■

Paralelismo implica además considerar la infraestructura paralela.

Fernando R. Rannou

Diinf-USACH

2 / 28

Velocidad secuencial

■

Considere un procesador moderno de 3.0 Ghz el cual completa una instrucción en 3 ciclos.

Luego

1

N = 3 × 109 (ciclos/s) · (inst./ciclo) = 109

3

instrucciones por segundo

■

Es decir, en 60 segundos, el procesador ejecutarı́a, 60 mil millones de instrucciones.

■

Consideraciones de acceso a memoria, memoria cache, contención del bus, y otros aspectos

impiden alcanzar este rendimiento

■

En grandes aplicaciones paralelas se requieren Trillones (1012 ) de operaciones por segundo

Fernando R. Rannou

Diinf-USACH

3 / 28

Supercomputadores tradicionales

1. Tecnologı́a

■

Procesador creado especı́ficamente para un supercomputador

■

Max. performance posible con buen ancho de banda de memoria

2. Beneficios

■

Programación secuencial

■

Más de 30 años de desarrollo de herramientas de software

■

I/O es relativamente simple

3. Limitaciones

Fernando R. Rannou

Diinf-USACH

■

Procesadores dedicados extremadamente caros

■

Se requiere de sistemas sofisticados de enfriamiento

■

Rendimiento por procesador llegando a un lı́mite

4 / 28

Supercomputadores paralelos

1. Tecnologı́a

■

Uso de muchos procesadores pequeños que trabajen en una parte del problema a

resolver

■

Capitalización de la inversión de la industria de microprocesadores y redes

2. Beneficios

■

Variedad de procesadores de propósito general en el mercado

■

Buena capacidad de escalamiento

■

Más barato

3. Limitaciones

Fernando R. Rannou

Diinf-USACH

■

Nueva tecnologı́a; programación paralela

■

Códigos secuenciales no sirven

■

Necesidad de nuevas tecnologı́as de software: compiladores, depuradores

■

I/O más complicado

5 / 28

Programación paralela

■

Programación paralela involucra

1. Descomposición de la tarea en partes más simples

2. Distribución de las tareas en un pool de procesadores

3. Coordinación del trabajo y comunicación entre procesadores

■

Consideraciones

1. Tipo de arquitectura paralela usada

2. Tipo de comunicación entre procesadores usada

Fernando R. Rannou

Diinf-USACH

6 / 28

Procesador escalar

■

Un procesador escalar base consiste de un procesador que “emite” una instrucción por ciclo

■

También existe una o más unidades de I/O

■

Los elementos se comunican a través de un bus del sistema

■

En general, los procesadores escalares están basados en pipelining

■

El 99.2% de los computadores top 500 (2007) tienen procesadores escalares

Memoria Principal

Bus de Memoria

DMA

ALU

Cache

I/O

FPU

Control

Bus de I/O

Fernando R. Rannou

Diinf-USACH

7 / 28

Procesador super escalar

■

Un procesador super escalar emite múltiples instrucciones por ciclo de reloj

■

Por ejemplo, si el procesador tiene m pipelines, puede ejecutar m instrucciones en paralelo (si

éstas son independientes)

■

El número real de instrucciones ejecutadas por ciclo depende de la independencia entre las

instrucciones.

■

Uso de optimización en fase de compilación

for i=0 to N {

a[i] = sin(30*i/PI)

}

Fernando R. Rannou

Diinf-USACH

a[0] = 0.5

for i=1 to N {

a[i] = a[i-1]*sin(30*i/PI)

}

8 / 28

Procesador vectorial

■

En un procesador vectorial paralelo (PVP) una instrucción opera simultáneamente sobre

elementos de vectores o arreglos de datos

■

Generalmente son muy caros y limitados en aplicaciones

■

No hay mucho desarrollo en la actualidad

■

Apoyo del compilador para vectorizar loops (Fortran 90)

■

Ejemplos: Cray SV1, Cray SV2, NEC Earth simulator

■

El 0.8 % de los computadores top 500 (2007) tienen procesadores vectoriales

z(1:100) = x(1:100) + y(1:100)

Fernando R. Rannou

Diinf-USACH

9 / 28

Multiprocesadores de memoria compartida

■

Un multiprocesador de memoria compartidad contiene dos o más procesadores escalares que

comparten el espacio de memoria. Dos modelos:

1. UMA (Uniform memory-access): la memoria fı́sica es compartida por todos los

procesadores; por lo tanto el tiempo de acceso es el mismo para todos.

2. NUMA (Non-uniform memory-access): la memoria fı́sica esta distribuida (local a cada

procesador) y por lo tanto el tiempo de acceso a ella no es uniforme.

■

La colección de todas las memorias locales forman el espacio global de direcciones

■

Programación multihebra usa eficientemente esta aquitectura

P1

P2

P3

Pn

Red de Interconneccion

(Bus, Crossbar, Red Multietapas etc)

Red de Interconneccion

(Bus, Crossbar, Red Multietapas, etc)

I/O

Fernando R. Rannou

Diinf-USACH

M1

M2

P1

P2

P3

Pn

M1

M2

M3

Mn

Mp

10 / 28

Multiprocesadores de memoria distribuida

■

Cada nodo consiste de un procesador autónomo con memoria local, y dispositivos de I/O.

■

Los nodos se comunican mediante una red de paso de mensajes, la cual provee conexiones

punto-a-punto y estáticas

■

La memoria local a cada nodo sólo puede ser accesada por dicho nodo

■

Variadas topologı́as de interconección: anillo, torus, hypercubo, etc.

■

Librerı́as nativas para comunicación proveen mejor rendimiento que librerı́as de propósito

general

Red de Interconneccion de paso

de mensajes

(malla, anillo, torus, hipercubo, etc)

Fernando R. Rannou

Diinf-USACH

P1

P2

P3

Pn

M1

M2

M3

Mn

11 / 28

Cluster de computadores

■

Cada nodo es un computador separado del resto, ej: PCs, estaciones de trabajo, etc

■

Los nodos pueden o no ser heterogéneos (procesador, velocidad, memoria, SO, otros)

■

Se conectan a través de un red de paso de mensajes

■

Sencillos de construir, actualizar; baratos

■

Limitada escalabilidad

■

I/O puede ser complicado

Fernando R. Rannou

Diinf-USACH

12 / 28

Redes de interconección estáticas

■

Una red de interconexión estática se puede describir mediante un grafo, donde

1. cada nodo es un procesador

2. un arco es un enlace de comunicación estático

■

Criterios de evaluación de una red estática:

1. Número de nodos

2. Diámetro: distancia máxima entre dos nodos

3. Ancho de bisección: mı́nimo número de arcos que deben ser eliminados para partir el

grafo en dos subgrafos de “igual” tamaño.

4. Número de arcos por nodo

5. Número de enlaces

Fernando R. Rannou

Diinf-USACH

13 / 28

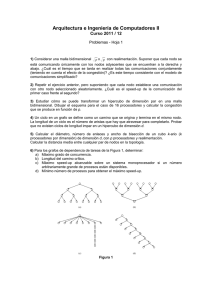

Arreglo lineal y anillo

■

Un arreglo lineal no es lo mismo que un

bus.

■

El arreglo presenta mala escalabilidad

■

Tanto el arreglo como el anillo son

baratos

Propiedad

Número de nodos

Diámetro

Ancho de bisección

Arcos por nodo

Número de enlaces

Arreglo

N

N −1

1

2

N −1

Anillo

N

⌊N/2⌋

2

2

N

3

4

2

5

0

1

2

3

4

1

0

6

7

11

8

10

9

Fernando R. Rannou

Diinf-USACH

14 / 28

Malla y Torus

■

Una malla es un lattice n-dimensional

■

Por ejemplo, para n = 2 tenemos una

malla 2D

■

Los enlances adicionales del torus reducen el diámetro a la mitad, respecto

de la malla

12

8

4

0

Fernando R. Rannou

Diinf-USACH

13

9

5

1

14

10

6

2

Propiedad

Número de nodos

Tamaño de la malla

Diámetro

Ancho de bisección

Arcos por nodo

Número de enlaces

Malla

N √

r × r (r = N )

2(r − 1)

r

4

2N − 2r

Torus

N

r×r

2⌊r/2⌋

2r

4

2N

15

5

6

7

3

4

5

0

1

2

11

7

3

15 / 28

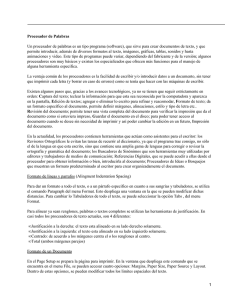

Árbol binario y estrella

■

El árbol ofrece buena escalabilidad, pero

tiene un diámetro largo

■

La raı́z es el cuello de botella; lo mismo

para la estrella

Propiedad

Número de nodos

Altura del árbol

Diametro

Ancho de bisección

Arcos por nodo

Número de enlaces

Estrella

N

h=2

2

⌊N/2⌋

N −1

N −1

Árbol

N

h = ⌈log N ⌉

2(h − 1)

1

3

N −1

2

0

3

1

2

3

7

4

8

1

9

5

6

10 11 12 13 14

0

0

4

7

5

6

Fernando R. Rannou

Diinf-USACH

16 / 28

Hipercubo

■

Cubo n-dimensional

■

Cada no se identifica por un número binario

■

Existe un arco entre nodos cuyos identificadores difieren en 1 bit

Número de nodos

Dimensión

Diametro

Ancho de bisección

Arcos por nodo

Número de enlaces

Fernando R. Rannou

Diinf-USACH

N

n = log2 N

n

N/2

n

nN/2

17 / 28

Tendencias actuales

■

Memoria distribuida compartida; necesidad de protocolos de coherencia de memoria cache

■

Procesadores que soporten nativamente (en hardware) hebras

■

Combinación de memoria compartida y memoria distribuida

■

Memoria compartida para sistemas masivos

Fernando R. Rannou

Diinf-USACH

18 / 28

Taxonomı́a Flynn

Propuesta para clasificar las arquitecturas de acuerdo a la multiplicidad de los datos e instrucciones

1. Single-Instruction, Single-Data (SISD)

■

Modelo tradicional, escalar

■

Puede tener pipelining

2. Single-Instruction, Multiple-Data (SIMD)

■

Arquitectura vectoriales

3. Multiple-Instruction, Multiple-Data (MIMD)

■

Mutliprocesadores y multicomputadores

■

MIMD de memoria compartida

■

MIMD de memoria distribuda

4. Single-Instruction, Multiple-Data (SIMD)

Fernando R. Rannou

Diinf-USACH

19 / 28

Ensalada de términos

■

SMP: Symmetric Multi Processing

■

NOW: Network of Workstations

■

Clusters Beowulf: clusters compuesto de computadores comerciales de proposito general

■

PVP: Parallel Vector Processing, procesadores vectoriales en computadores paralelos

■

MPP: Massively Parallel Processing; muuuuuchos procesadores

■

Computación distribuida

■

Computación Grid: unifica recursos dispersos geograficamente para sistema computacional

virtual y transparente

Fernando R. Rannou

Diinf-USACH

20 / 28

Los supercomputadores más veloces

www.top500.org

Rank

Nombre

Procesadores

(cores)

Procesador

Tflop/s

(Linpack)

Sistema

operativo

1

IBM BlueGene/L

212992

PowerPC 440 700 Mhz (dual core)

478.2

CNK

2

IBM BlueGene/P

65536

PowerPC 450 850 Mhz (dual core)

167.3

CNK/SLES

3

SGI Altix ICE 8200

14336

Intel Xeon 53xx 3 Ghz (quad core)

126.9

SLES10

4

HP EKA-Cluster Platform

14240

Intel Xeon 53xx 3 Ghz (quad core)

117.9

Linux

5

HP Cluster Platform

13728

Intel Xeon 53xx 2.66 Ghz (quad core)

102.8

Linux

6

Cray Red Storm

26569

AMD x86 64 Opteron 2.4 Ghz (dual core)

102.2

UNICOS/SUSE Linux

9

Cray XT4

19320

AMD x86 64 Opteron 2.6 Ghz (dual core)

85.3

UNICOS/Linux

10

Blue Gene/L

36864

PowerPC 440 700 MHz (dual core)

82.1

CNK/SLES

...

451

HP Cluster Platform (Brazil)

1024

Intel Xeon 53xx 2.3 Ghz (quad core)

6.2

Linux

...

Fernando R. Rannou

Diinf-USACH

21 / 28

Distribución geográfica

Región

America del Sur

Norte Africa

America del Norte

Asia del Este

Asia Sur Este

Europa del Sur

Australia y

Nueva Zelandia

Asia Centro-Sur

Asia Oeste

Europa del Este

Europa del Norte

Europa del Oeste

Fernando R. Rannou

Diinf-USACH

Número

computadores

1

1

288

42

5

15

2

9

2

8

64

63

Porcentaje

0.20%

0.20%

57.60%

8.40%

1.00%

3.00%

0.40%

Suma Rmax

(GFlops)

6210

9949

4196452

496966

43454

206564

18407

Suma Rpeak

(GFlops)

9555

24192

6264122

742753

76931

384390

21299

Suma

procesadores

1024

2016

1031517

102098

8656

47372

5632

1.80%

0.40%

1.60%

12.80%

12.60%

194524

13806

88972

776752

914114

303651

21575

138212

1255622

1315785

34932

2312

13084

160828

238624

22 / 28

Distribución por Sistema Operativo

Familia

SO

Linux

Unix

BSD Based

Mixed

Mac OS

Fernando R. Rannou

Diinf-USACH

Número

computadores

376

86

3

32

3

Porcentaje

75.20%

17.20%

0.60%

6.40%

0.60%

Suma Rmax

(GFlops)

2014910

559636

47697

872226

32989

Suma Rpeak

(GFlops)

3195766

807423

53248

1104103

53008

Número

procesadores

516189

142104

5888

350484

6296

23 / 28

Distribución por procesador

Fernando R. Rannou

Diinf-USACH

24 / 28

Pasado, presente y futuro

Fernando R. Rannou

Diinf-USACH

25 / 28

Arquitectura del Blue Gene/L

■

Procesador dual 2.8 GFlops, 6.5 GFlops

■

Tarjeta cómputo con dos procesadores, 11.2 GFlops

■

Tarjeta nodo con 16 tarjetas de cómputo, 180 GFlops

■

Rack con 32 tarjetas nodos, 5.6 TFlops

■

Total 350 TFlops

Fernando R. Rannou

Diinf-USACH

26 / 28

Procesador del Blue Gene/L

Fernando R. Rannou

Diinf-USACH

27 / 28

Modelos de programación paralela

Fernando R. Rannou

Diinf-USACH

28 / 28