Control de flujo

Anuncio

Computación Paralela

Curso 2012/2013

Vicente Galiano Ibarra

Introducción Arquitecturas Avanzadas

Introducción

Clasificación Sistemas Paralelos

Rendimiento Sistemas Paralelos

Procesadores Vectoriales

Procesadores Matriciales

Redes de Interconexión

Multiprocesadores

Multicomputadores

Introducción I

Procesadores superescalares

Solapamiento de instrucciones (varios

cauces):

Dependencia de datos verdadera (RAW)

Dependencia relativas al procedimiento

Conflictos en los recursos

Dependencias de salida (WAW)

Antidependencia (WAR)

Políticas de emisión de instrucciones

Introducción II

El paralelismo ya existe a nivel de

procesador:

Segmentación y supersegmentación

Se aumenta el número de etapas de cada

instrucción pipeline

Cuando más etapas mayor paralelismo,

etapas más sencillas y mayor frecuencia

de funcionamiento.

Introducción III

Procesadores VLIW (paralelización realizada por

el compilador)

Estas son Arquitecturas Von Neumann: máquinas

secuenciales procesando datos escalares

La frontera no está clara entre los procesadores

superescalares y los vectoriales (los cauces

implican hardware replicado)

Clasificación Sistemas Paralelos I

Clasificación Flynn

SISD (Single Instruction Single Data): Máquina

Von Neumann clásica

MISD (Multiple Instruction Single Data): díficil

implementación (procesadores vectoriales*)

SIMD (Single Instruction Multiple Data):

procesadores matriciales

MIMD (Multiple Instruction Multiple Data):

multiprocesador

Clasificación Sistemas Paralelos II

Clasificación Sistemas Paralelos III

Fuentes de paralelismo

Paralelismo de Control:

Dependencia de control de secuencia

Dependencia de control de comunicación

Paralelismo de Datos

Paralelismo de flujo

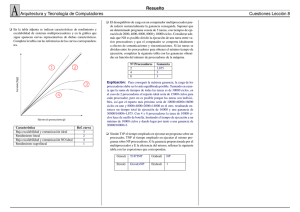

Rendimiento Sistemas Paralelos I

Eficiencia / Speed-up

Escalabilidad

Redundancia / Utilización

Calidad

Rendimiento Sistemas Paralelos II

Grado de paralelismo

Paralelismo medio

Speed-up asintótico

Para m procesos

Media aritmética del rendimiento

Media geométrica del rendimiento

Rendimiento medio armónico

Speed-up armónico medio

Rendimiento Sistemas Paralelos III

Ley de Amhdal:

Sn=n/(1+(n-1)α) Donde α es la probabilidad de usar

un modo secuencial puro.

Sn 1/α

Independientemente del número de procesadores

existe un límite superior del speed-up debido a

la parte secuencial

Si α = 0 el speed-up es el ideal

12

Arquitecturas Vectoriales

13

Arq. De Memoria Compartida

14

Arq. de Memoria Distribuida

Clusters

15

Arq. Mem.Comp. y Mem.Dist.

16

Pasos en el Desarrollo de Aplicaciones

Científicas

17

Paralelización de Programas

18

Medidas de Paralelismo

Speed-up

Tiempo ejecucion en 1 procesador

Sp =

Tiempo ejecución en p procesadores

Eficiencia

E=

Sp

p

Procesadores Vectoriales I

Computación matricial (sin dependencia de

datos)

Replica unidades de cálculo pero no de

control

Instrucciones vectoriales:

Sin dependencia de datos

Instrucciones de alta carga computacional

Patrón de acceso a memoria conocido

Sustituyen a bucles

Procesadores Vectoriales I

: Processor board of a CRAY YMP vector computer (operational ca.

1992-2000). The board was liquid cooled and is one vector processor

with shared memory (access to one central memory)

Procesadores Vectoriales II

Arquitecturas Vectoriales

Máquina vectorial con registros (actuales)

Máquina vectorial memoria-memoria

Componentes básicos

Registros Vectoriales

Unidades funcionales vectoriales

Unidad de carga/almacenamiento vectores

Registros escalares

Procesadores Vectoriales III

Instrucciones vectoriales básicas

Vector-vector

Vector-escalar

Vector-memoria

Reducción de vectores

Reunir y esparcir

Enmascaramiento

Procesadores Vectoriales III

Factores que afectan al rendimiento

Longitud de los vectores y velocidad de

inicialización

Los riesgos estructurales (control de flujo)

Dependencia de datos

Procesadores Vectoriales IV

Longitud de vectores

Longitud natural de los vectores diferente a la

de la arquitectura

VLR (Vector Lenght Register)

MVL (Maximum Vector Lenght)

La gestión de los parámetros anteriores

puede realizarla el compilador

Separación de vectores en memoria

(carga y almacenamiento con separación)

Procesadores Vectoriales V

Mejora del rendimiento

Encadenamiento de operaciones

Sentencias if

Máscara vectorial

Matrices Dispersas

Dispersión/agrupamiento (scatter/gather)

Procesadores Vectoriales VI

Medidas del rendimiento

Rn: Velocidad en MFLOPS para un vector de longitud

n

R∞: Velocidad en MFLOPS para un vector de

longitud infinita

N1/2: longitud necesaria para alcanzar R∞/2

Nv: longitud para la cual el modelo vectorial es

preferible al escalar

*** NOTA: Los procesadores escalares actuales obtienen rendimientos

muy similares a los vectoriales

Procesadores Matriciales I

Explota el paralelismo de datos más que el

paralelismo de instrucciones

Procesadores Matriciales II

Modelo basado en {N,C,I,M,R}

N: Número de elementos de proceso de la máquina

C: Conjunto de instrucciones nativas de la Unidad de

Control

I: Conjunto de instrucciones que se envían a los EPs

M: posibilidad de enmascaramientos de los EPs

R: funciones de rutado para la comunicación entre

EPs

Procesadores Matriciales III

Estructura básica de un EP

Procesadores Matriciales IV

Los modelos matriciales se caracterizan:

Están destinados a aplicaciones específicas a

las cuales extraen gran rendimiento

Su programación no es sencilla por tener que

programar con mucha dependencia del

hardware

Prácticamente no existen en el mercado de

supercomputadores comerciales

Redes de Interconexión I

Es uno de los elementos fundamentales

que modifican la propia arquitectura y el

rendimiento

Las redes se utilizan tanto en los

computadores matriciales como en

multiprocesadores y multicomputadores

Redes de Interconexión II

Definiciones básicas:

Tamaño de la red (número de nodos)

Grado del nodo (de entrada y salida) Coste

Diámetro de la red

Anchura de la bisección

Longitud del cable

Simetría

Redes de Interconexión III

Rendimiento:

Funcionalidad

Latencia

Ancho de banda

Complejidad Hardware

Escalabilidad

Capacidad de transmisión

Redes de Interconexión IV

Topología:

Grafo de interconexión

Parámetros:

Ancho de la bisección

Grado del nodo

Diámetro de la red

Longitud

Simetría

Estructura física

Redes de Interconexión V

Control de flujo, regula el tráfico en la red

asignando recursos (buffers y canales) a

las unidades de información:

Mensaje

Paquete

Flit

Debe solucionar el posible bloqueo de un

paquete

Redes de Interconexión VI

Encaminamiento, método para elegir un

camino

Dada una posición actual y un destino existe

un conjunto de canales posibles

En cada paso se elige un canal de los

posibles teniendo en cuenta información que

puede ser constante, aleatoria o en función

del tráfico

Redes de Interconexión VII

Métodos de Encaminamiento,

Deterministas: el camino depende unívocamente del

nodo destino y del nodo origen

Inconscientes: la elección puede ser aleatoria, en

función del tiempo o en función del contenido

Adaptativos: la función depende del tráfico es decir

del estado de la red

Redes de Interconexión VIII

Clasificación según topología:

Se pueden clasificar en síncronas y asíncronas y de

control centralizado, descentralizado y distribuido.

El mercado de redes de estaciones de trabajo están

copados por redes asíncronas de control distribuido:

Redes de medio compartido

Redes Directas

Redes Indirectas

Redes Híbridas

Redes de Interconexión IX

Redes de medio compartido:

El medio de transmisión es compartido por todos los elementos

de la red

Redes directas:

Cada elemento está conectado de forma directa a un conjunto

(reducido) de otros dispositivos

Entre elementos no vecinos es necesario la transmisión a través

de varios dispositivos intermedios

Redes indirectas:

Se utilizan conmutadores para conectar los elementos de

comunicación

Cualquier comunicación requiere el paso a través de

conmutadores

Híbrido

Redes de Interconexión X

Redes de medio compartido

Redes a área local

Bus de contención (Ethernet)

Bus de tokens (Arcnet)

Tokeng Ring (IBM)

Bus de sistema (monoprocesadores y

multiprocesadores)

Son las redes más sencillas en las que sólo un

elemento usa la red en un momento dado, siendo la

red un elemento pasivo (no genera mensajes)

Estas redes se convierten en un cuello de botella al

ampliar el número de procesadores de la red

Redes de Interconexión XI

Redes directas

Mallas

Toros

Hipercubos

Estas redes escalan bien. Los nodos además

de otras funciones realizan las funciones de

router o encaminador (bien el propio

procesador o routers dedicados)

Redes de Interconexión XII

Cada nodo dispone de canales internos y de canales externos

Dos nodos conectados directamente son nodos vecinos o adyacentes

Lógicamente todos los nodos deben ser visibles

Redes de Interconexión XIII

Ejemplos de redes directas

Redes de Interconexión XIV

Redes Indirectas:

Basadas en conmutadores

Conmutador dispone de puertos

El conmutador se conecta con el procesador

y con otros conmutadores

Una característica importante es el número

de conmutadores a atravesar

Redes de Interconexión XV

Redes Híbridas:

Mezcla redes de medio compartido y de

redes directas o indirectas

Ejemplos:

Redes multibus

Redes jerárquicas

Redes basadas en clusters

Multiprocesadores I

Sistema MIMD

Memoria COMPARTIDA

Parámetros importantes:

Red de interconexión

Consistencia de memoria

Coherencia de caché

Sincronización

Multiprocesadores II

Redes de interconexión:

Buses (medio compartido)

Bajo coste, Mala escalabilidad, no admite muchos

procesadores

Redes indirectas

– Red de barras cruzadas

Una sola etapa de conmutación, muy cara para

muchos elementos

– Redes multietapa

Como se conectan las diferentes etapas definen las

características de la red

Tipos: Bloqueante, No bloqueante, Reconfigurable

Multiprocesadores III

Consistencia de memoria:

Debemos asegurar una coherencia realizando las

tareas de una sincronización

Por software mediante flags (no practicable)

Modelo de consistencia que especifica el orden de

la realización de las operaciones en memoria

La consistencia implica la coherencia

Modelos:

– Consistencia secuencial estricta

– Consistencia secuencial

– Otros modelos

Multiprocesadores IV

Consistencia secuencial estricta:

Cualquier lectura devuelve el valor almacenado

más reciente

No es implementable

Consistencia secuencial:

Objetivo: modelo multihilo obtenga los mismos

resultados en 1 o varios procesadores

Las operaciones se hagan visibles en el orden del

programa

El compilador no puede optimizar

Multiprocesadores V

Otros modelos de consistencia:

Modelos relajados que afectan a:

–

–

–

–

RR

RW

WW

WR

Consistencia de procesador

– Elimina la ordenación W R por la existencia de buffers

de escritura

Ordenación por almacenamiento parcial

– Elimina W W para escrituras no conflictivas

Multiprocesadores VI

Consistencia débil elimina las cuatro ordenaciones

– Es necesaria la implementación de sincronizaciones

Consistencia de liberación

– Sincronizaciones para poder adquirir el acceso a una

variable compartida y sincronizaciones para liberar esa

variable

Multiprocesadores VII

Coherencia de caché:

Las vistas en las diferentes cachés de los

diferentes procesadores pueden diferir

Un sistema debe mantener la coherencia de la

caché

El programador en este punto no tiene mucho que

decir

Este concepto es importante en nuestros

programas en memoria compartida

Multiprocesadores VIII

Sincronización:

Cerrojos

Barreras

Implementados en hardware o software

Multicomputadores

Mejoran las sincronizaciones, las

contenciones de memoria y la escalabilidad

Solo existe memoria local

El intercambio de información se realiza por

mensajes

A nivel rendimiento mejoran a los

multiprocesadores para gran número de

nodos

Son muy importantes las redes de

interconexión y la granularidad de los

algoritmos